# intel

**AB-38**

### APPLICATION BRIEF

### **Interfacing the 82786 Graphics Coprocessor to the 8051**

RICK SCHUE REGIONAL APPLICATIONS SPECIALIST INDIANAPOLIS, INDIANA

February 1996

Order Number: 270528-003

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

\*Other brands and names are the property of their respective owners.

†Since publication of documents referenced in this document, registration of the Pentium, OverDrive and iCOMP trademarks has been issued to Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

COPYRIGHT © INTEL CORPORATION, 1996

| INTERFACING THE 82786 | CONTENTS  |

|-----------------------|-----------|

| GRAPHICS COPROCESSOR  | HARDWARE  |

| TO THE 8051           | OPERATION |

|      | CONTENTS     | PAGE |

|------|--------------|------|

| SOR  | HARDWARE     | 1    |

| 8051 | OPERATION    | 1    |

|      | DESIGN NOTES | 1    |

### intel

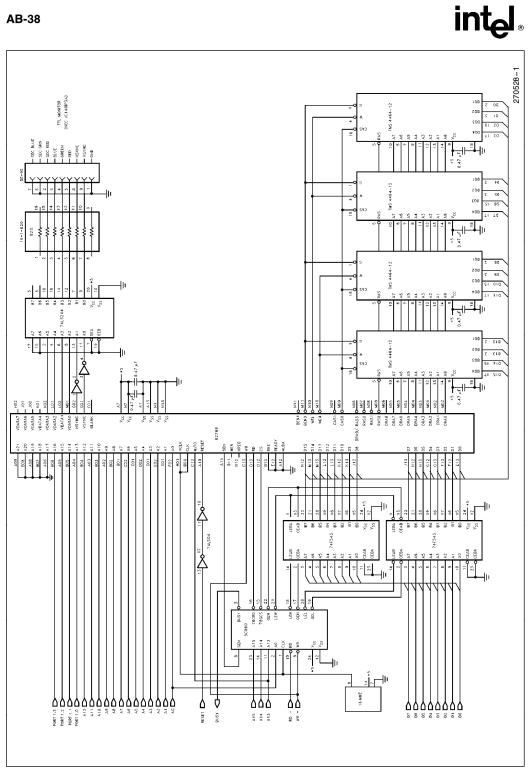

Interfacing the 82786 to the 8051 presents some interesting challenges, but can be accomplished with a little additional logic and software. Since the 82786 looks like a DRAM controller to the host CPU, wait states are often required when accessing the coprocessor. Since wait states are not supported by the 8051, latching transceivers and dummy read and write cycles are used to communicate with the 82786. Byte swapping is also required in the external logic to allow the 8 bit 8051 to read and write the 16 bit graphics memory supported by the 82786. This byte swapping is accomplished with the latching transceivers as well. All of the control logic is implemented in an Intel 5C060 EPLD, allowing the entire interface to fit into three 24 pin DIPs.

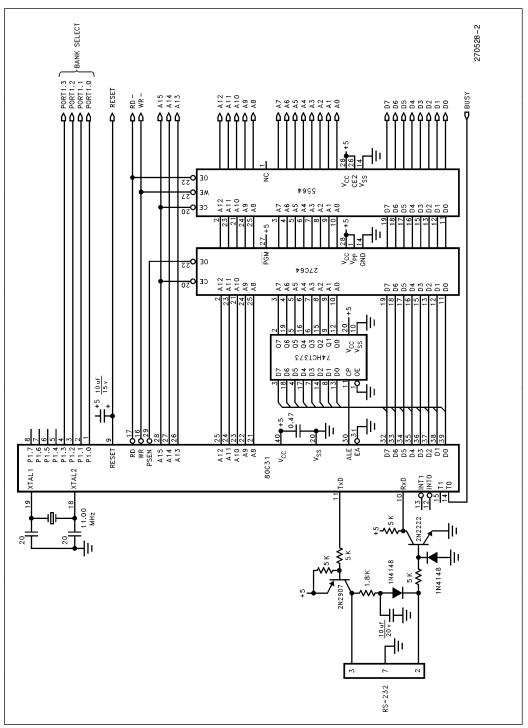

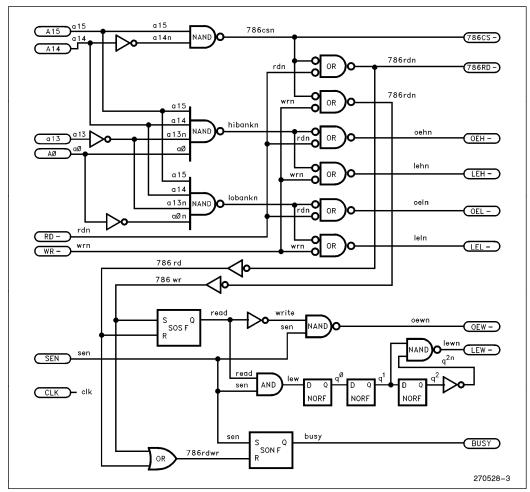

#### HARDWARE

Figure 1 shows the interface between the 8051 bus and the 82786. Figure 2 shows a typical 8051 CPU design needed to complete the circuit. In this design the 82786 is mapped into an 8K byte window in 8051 data memory space. The upper address bits are used as a "page select" and are provided by I/O pins on the 8051. The 5C060 EPLD contains the control logic for the transceivers and address decoding for the 82786. An equivalent circuit for the EPLD is shown in Figure 3; the ".ADF" file is shown in Figure 4. The 82786 data memory is mapped into one 8K block (A000H– BFFEH), the 82786 registers are mapped into another (8000H–807EH), and the transceivers are mapped into a third block of memory (C000H–C001H).

#### **OPERATION**

Operation of the interface is as follows. For reading the graphics memory, the 8051 sets the upper address bits (PORT 1.0-1.3) and then performs a dummy read operation to the desired location in graphics memory (A000H thru BFFEH). The dummy read cycle pro-

vides the address and RD/WR information to the 82786, which runs a cycle and deposits the 16 bit result into the latching transceivers at the end of the read cycle, as indicated by SEN. This event clears the BUSY flip flop in the EPLD. When the BUSY signal goes inactive, the 8051 reads the low byte from the latching transceiver at address C000H and the high byte free address C001H.

For write cycles, the 8051 writes the low byte of the word into the latch at address C000H and the high byte into address C001H. Next the upper address bits are set with PORT1 and a dummy write cycle is performed in graphics memory at the desired address (A000H–BFFEH). Like in the read example, the 82786 runs a memory cycle at this point, enabling the outputs of the latching transceivers at the proper time in the write cycle, as indicated by SEN going active.

Accessing the registers inside the 82786 is done in exactly the same fashion, except that the 82786 is addressed in locations 8000H through 807EH. This causes the EPLD to drive the M/IO pin low during these cycles.

#### **DESIGN NOTES**

74F543's are used for the latching transceivers in this design, although 74HCT646's could be used to reduce the total power consumption. Some changes to the EPLD would be required in this case. The interface assumes that all memory accesses to the 82786 are word references; accordingly, BHE is grounded at the 82786. All addresses generated by the 8051 must be even byte addresses, the only byte operations allowed are the reads and writes to the latching transceivers. The design shown here incorporates hardware workarounds for the earlier "C-step" 82786; the current "D-step" part will work in the design as well. Additional information regarding the 82786 can be found in the "82786 Graphics Coprocessor User's Manual", Intel publication number 231933.

intel

Figure 2

## intel®

#### AB-38

## intel®

| INTEL<br>August 11, 1987<br>1-003<br>0<br>5C060<br>8051/82786 Control Logic for 8051 Demo Board<br>786 I/0 800H-807FH<br>786 Memory A000H-BFFFH<br>Registers C000H,C001H<br>0PTIONS: TURB0 = 0N<br>PART: 5C060 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>INPUTS: A15@23,A14@14,A13@11,A0@2,RD/@10,WR/@9,SEN@8,CKK OUTPUTS: 786CS/@15,786RD/16,OEH/@17,LEH/@18,OEL/@19,LEL/@20, LEW/@21,OEW/@22,READ@4,BUSY@3 NETWORK: a15 = INP (A15) a14 = INP (A14)</pre>        |

| al3 = INP (Al3)<br>a0 = INP (A0)<br>rdn = INP (RD/)<br>wrn = INP (WR/)<br>sen = INP (SEN)<br>clk = INP (CLK)                                                                                                   |

| al4n = NOT (al4)<br>al3n = NOT (al3)<br>aOn = NOT (aO)<br>786csn = NAND (al5,al4n)<br>786CS/ = CONF (786csn,VCC)                                                                                               |

| 786rdn = OR (786csn,rdn)<br>786RD/ = CONF (786rdn,VCC)<br>hibankn = NAND (al5,al4,al3n,a0)<br>lobankn = NAND (al5,al4,al3n,a0n)<br>oehn = OR (hibankn,rdn)<br>OEH/ = CONF (oehn,VCC)                           |

| <pre>lehn = OR (hibankn,wrn)<br/>LEH/ = CONF (lehn,VCC)<br/>oeln = OR (lobankn,rdn)<br/>OEL/ = CONF (oeln,VCC)<br/>leln = OR (lobankn,wrn)<br/>LEL/ = CONF (leln,VCC)</pre>                                    |

| <pre>oewn = NAND (sen,write)<br/>OEW/ = CONF (oewn,VCC)<br/>lew = AND (sen,read)<br/>q0 = NORF (lew,clk,GND,GND)<br/>q1 = NORF (q0,clk,GND,GND)<br/>q2 = NORF (q1,clk,GND,GND)</pre>                           |

| <pre>q2n = NOT (q2)<br/>lewn = NAND (q1,q2n)<br/>LEW/ = CONF (lewn,VCC)<br/>786wr = NOR (786csn,wrn)<br/>786rd = NOT (786rdn)</pre>                                                                            |

| READ,read = SOSF (786rd,clk,786wr,GND,GND,VCC)<br>write = NOT (read)<br>786rdwr = OR (786rd,786wr)<br>BUSY = SONF (786rdwr,clk,sen,GND,GND,VCC)<br>END\$                                                       |

Figure 4.