AP-252

### APPLICATION NOTE

### **Designing With The 80C51BH**

**TOM WILLIAMSON** MCO APPLICATIONS ENGINEER

March 1985

Order Number: 270068-002

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

\*Other brands and names are the property of their respective owners.

†Since publication of documents referenced in this document, registration of the Pentium, OverDrive and iCOMP trademarks has been issued to Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

COPYRIGHT © INTEL CORPORATION, 1996

### DESIGNING WITH THE 80C51BH

| CONTENTS PAGE                                                                                         |  |

|-------------------------------------------------------------------------------------------------------|--|

| <b>CMOS EVOLVES</b> 1                                                                                 |  |

| WHAT IS CHMOS? 1                                                                                      |  |

| THE MCS-51 FAMILY IN CHMOS 1                                                                          |  |

| LATCHUP                                                                                               |  |

| LOGIC LEVELS AND INTERFACING<br>PROBLEMS 2                                                            |  |

| NOISE CONSIDERATIONS                                                                                  |  |

| UNUSED PINS                                                                                           |  |

| PULLUP RESISTORS 4                                                                                    |  |

| PULLDOWN RESISTORS 4                                                                                  |  |

| DRIVE CAPABILITY OF THE<br>INTERNAL PULLUPS5                                                          |  |

| POWER CONSUMPTION 6                                                                                   |  |

| Idle                                                                                                  |  |

| Power Down7                                                                                           |  |

| USING THE POWER DOWN MODE8                                                                            |  |

| USING POWER MOSFETs TO<br>CONTROL V <sub>CC</sub>                                                     |  |

| BATTERY BACKUP SYSTEMS9                                                                               |  |

| POWER SWITCHOVER CIRCUITS 11                                                                          |  |

| 80C31BH + CHMOS EPROM 12                                                                              |  |

| SCANNING A KEYBOARD 13                                                                                |  |

| DRIVING AN LCD         16           Using an LCD Driver         17                                    |  |

| <b>RESONANT TRANSDUCERS</b> 18Frequency Measurements18Period Measurements20Pulse Width Measurements21 |  |

| HMOS/CHMOS<br>INTERCHANGEABILITY                                                                      |  |

| Unused Pins 22                                                                                        |  |

| Logic Levels 22                                                                                       |  |

| Idle and Power Down 22                                                                                |  |

| <b>REFERENCES</b> 23                                                                                  |  |

### **CMOS EVOLVES**

The original CMOS logic families were the 4000-series and the 74C-series circuits. The 74C-series circuits are functional equivalents to the corresponding numbered 74-series TTL circuits, but have CMOS logic levels and retain the other well known characteristics of CMOS logic.

These characteristics are: low power consumption, high noise immunity, and slow speed. The low power consumption is inherent to the nature of the CMOS circuit. The noise immunity is due partly to the CMOS logic levels, and partly to the slowness of the circuits. The slow speed is due to the technology used to construct the transistors in the circuit.

The technology used is called metal-gate CMOS, because the transistor gates are formed by metal deposition. More importantly, the gates are formed after the drain and source regions have been defined, and must overlap the source and drain somewhat to allow for alignment tolerances. This overlap plus the relatively large size of the transistors themselves result in high electrode capacitance, and that is what limits the speed of the circuit.

High speed CMOS became feasible with the development of the self-aligning silicon gate technology. In this process polysilicon gates are deposited **before** the source and drain regions are defined. Then the source and drain regions are formed by ion implantation using the gate itself as a mask for the implantation. This eliminates most of the overlap capacitance. In addition, the process allows smaller transistors. The result is a significant increase in circuit speed. The 74HC-series of CMOS logic circuits is based on this technology, and has speeds comparable to LS TTL, which is to say about 10 times faster than the 74C-series circuits.

The size reduction that contributes to the higher speed also demands an accompanying reduction in the maximum supply voltage. High-speed CMOS is generally limited to 6V.

### WHAT IS CHMOS?

CHMOS is the name given to Intel's high-speed CMOS processes. There are two CHMOS processes, one based on an n-well structure and one based on a p-well structure. In the n-well structure, n-type wells are diffused into a p-type substrate. Then the n-channel transistors (nFETs) are built into the substrate and pFETs are built into the n-wells. In the p-well structure, p-type wells are diffused into an n-type substrate. Then the nFETs are built into the wells and pFETs, into the

substrate. Both processes have their advantages and disadvantages, which are largely transparent to the user.

Lower operating voltages are easier to obtain with the p-well structure than with the n-well structure. But the p-well structure does not easily adapt to an EPROM which would be pin-for-pin compatible with HMOS EPROMs. On the other hand the n-well structure can be based on the solidly founded HMOS process, in which nFETs are built into a p-type substrate. This allows somewhat more than half of the transistors in a CHMOS chip to be constructed by processes that are already well characterized.

Currently Intel's CHMOS microcontrollers and memory products are n-well devices, whereas CHMOS microprocessors are p-well devices.

Further discussion of the CHMOS technology is provided in References 1 and 2 (which are reprinted in the Microcontroller Handbook).

### THE MCS®-51 FAMILY IN CHMOS

The 80C51BH is the CHMOS version of Intel's original 8051. The 80C31BH is the ROMless 80C51BH, equivalent to the 8031. These CHMOS devices are architecturally identical with their HMOS counterparts, except that they have two added features for reduced power. These are the Idle and Power Down modes of operation.

In most cases, an 80C51BH can directly replace the 8051 in existing applications. It can execute the same code at the same speed, accept signals from the same sources, and drive the same loads. However, the 80C51BH covers a wider range of speeds, will emit CMOS logic levels to CMOS loads, and will draw about 1/10 the current of an 8051 (and less yet in the reduced power modes). Interchangeability between the HMOS and CHMOS devices is discussed in more detail in the final section of this Application Note.

It should be noted that the 80C51BH CPU is not static. That means if the clock frequency is too low, the CPU might forget what it was doing. This is because the circuitry uses a number of dynamic nodes. A dynamic node is one that uses the note-to-ground capacitance to form a temporary storage cell. Dynamic nodes are used to reduce the transistor count, and hence the chip area, thus to produce a more economical device.

This is not to say that the on-chip RAM in CHMOS microcontrollers is dynamic. It's not. It's the CPU that is dynamic, and that is what imposes the minimum clock frequency specification.

### LATCHUP

Latchup is an SCR-type turn-on phenomenon that is the traditional nemesis of CMOS systems. The substrate, the wells, and the transistors form parasitic pnpn structures within the device. These parasitic structures turn on like an SCR if a sufficient amount of forward current is driven through one of the junctions. From the circuit designer's point of view it can happen whenever an input or output pin is externally driven a diode drop above  $V_{CC}$  or below  $V_{SS}$ , by a source that is capable of supplying the required trigger current.

However much of a problem latchup has been in the past, it is good to know that in most recently developed CMOS devices, and specifically in CHMOS devices, the current required to trigger latchup is typically well over 100 mA. The 80C51BH is virtually immune to latchup. (References 1 and 2 present a discussion of the latchup mechanisms and the steps that are taken on the chip to guard against it.) Modern CMOS is not absolutely immune to latchup, but with trigger currents in the hundreds of mA, latchup is certainly a lot easier to avoid than it once was.

A careless power-up sequence might trigger a latchup in the older CMOS families, but it's unlikely to be a major problem in high-speed CMOS or in CHMOS. There is still some risk incurred in inserting or removing chips or boards in a CMOS system while the power is on. Also, severe transients, such as inductive kicks or momentary short-circuits, can exceed the trigger current for latchup.

For applications in which some latchup risk seems unavoidable, you can put a small resistor ( $100\Omega$  or so) in series with signal lines to ensure that the trigger current will never be reached. This also helps to control overshoot and RFI.

### LOGIC LEVELS AND INTERFACING PROBLEMS

CMOS logic levels differ from TTL levels in two ways.

### intel®

First, for equal supply voltages, CMOS gives (and requires) a higher "logic 1" level than TTL. Secondly, CMOS logic levels are  $V_{CC}$  (or VDD) dependent, whereas guaranteed TTL logic levels are fixed when  $V_{CC}$  is within TTL specs.

Standard 74HC logic levels are as follows:

$\begin{array}{l} V_{IH}MIN \,=\, 70\% \mbox{ of } V_{CC} \\ V_{IL}MAX \,=\, 20\% \mbox{ of } V_{CC} \\ V_{OH}MIN \,=\, V_{CC} \,-\, 0.1V, \, \left| I_{OH} \right| \,\leq\, 20 \ \mu A \\ V_{OL}MAX \,=\, 0.1V, \, \left| I_{OL} \right| \,\leq\, 20 \ \mu A \end{array}$

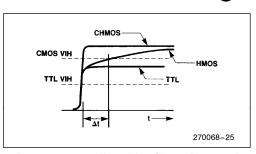

Figure 1 compares 74HC, LS TTL, and 74HCT logic levels with those of the HMOS 8051 and the CHMOS 80C51BH for  $V_{\rm CC}=5V$ .

Output logic levels depend of course on load current, and are normally specified at several load currents. When CMOS and TTL are powered by the same  $V_{CC}$ , the logic levels guaranteed on the data sheets indicate that CMOS can drive TTL, but TTL can't drive CMOS. The incompatibility is that the TTL circuit's  $V_{OH}$  level is too low to reliably be recognized by the CMOS circuit as a valid  $V_{IH}$ .

Since HMOS circuits were designed to be TTL-compatible, they have the same incompatibility.

Fortunately, 74HCT-series circuits are available to ease these interfacing problems. They have TTL-compatible logic levels at the inputs and standard CMOS levels at the outputs.

The 80C51BH is designed to work with either TTL or CMOS. Therefore its logic levels are specified very much like 74HCT circuits. That is, its input logic levels are TTL-compatible, and its output characteristics are like standard high-speed CMOS.

### NOISE CONSIDERATIONS

One of the major reasons for going to CMOS has traditionally been that CMOS is less susceptible to noise. As previously noted, its low susceptibility to noise is

| Logic State     |      |       | $V_{CC} = 5V$ |       |         |

|-----------------|------|-------|---------------|-------|---------|

| Logio otato     | 74HC | 74HCT | LS TTL        | 8051  | 80C51BH |

| V <sub>IH</sub> | 3.5V | 2.0V  | 2.0V          | 2.0V  | 1.9V    |

| V <sub>IL</sub> | 1.0V | 0.8V  | 0.8V          | 0.8V  | 0.9V    |

| V <sub>OH</sub> | 4.9V | 4.9V  | 2.7V          | 2.4V  | 4.5V    |

| V <sub>OL</sub> | 0.1V | 0.1V  | 0.5V          | 0.45V | 0.45V   |

Figure 1. Logic Level Comparison. (Output voltage levels depend on load current. Data sheets list guaranteed output levels for several load currents. The output levels listed here are for minimum loading.)

#### AP-252

partly due to superior noise margins, and partly due to its slow speed.

Noise margin is the difference between  $V_{OL}$  and  $V_{IL}$ , or between  $V_{OH}$  and  $V_{IH}$ . If  $V_{OH}$  from a driving circuit is 2.7V and  $V_{IH}$  to the driven circuit is 2.0V, then the driven circuit has 0.7V of noise margin at the logic high level. These kinds of comparisons show that an all-CMOS system has wider noise margins than an all-TTL system.

Figure 2 shows noise margins in CMOS and LS TTL systems when both have  $V_{\rm CC} = 5V$ . It can be seen that CMOS/CMOS and CMOS/CHMOS systems have an edge over LS TTL in this respect.

Noise margins can be misleading, however, because they don't say how much noise energy it takes to induce in the circuit a noise voltage of sufficient amplitude to cause a logic error. This would involve consideration of the width of the noise pulse as compared with the circuit's response speed, and the impedance to ground from the point of noise introduction in the circuit.

When these considerations are included, it is seen that using the slower 74C- and 4000-series circuits with a 12 or 15V supply voltage does offer a truly improved level of noise immunity, but that high-speed CMOS at 5V is not significantly better than TTL.

One should not mistake the wider supply voltage tolerance of high-speed CMOS for  $V_{CC}$  glitch immunity. Supply voltage tolerance is a DC rating, not a glitch rating.

For any clocked CMOS, and most especially for VLSI CMOS,  $V_{CC}$  decoupling is critical. CHMOS draws

| Interface        |                                               | argin for<br>= 5V                              |

|------------------|-----------------------------------------------|------------------------------------------------|

| interface        | Logic Low<br>V <sub>IL</sub> -V <sub>OL</sub> | Logic High<br>V <sub>OH</sub> -V <sub>IH</sub> |

| 74HC to 74HC     | 0.9V                                          | 1.4V                                           |

| LSTTL to LSTTL   | 0.3V                                          | 0.7V                                           |

| LSTTL to 74HCT   | 0.3V                                          | 0.7V                                           |

| LSTTL to 80C51BH | 0.3V                                          | 0.7V                                           |

| 74HC to 80C51BH  | 0.8V                                          | 3.0V                                           |

| 80C51BH to 74HC  | 0.8V                                          | 1.0V                                           |

Figure 2. Noise Margins for CMOS and LS TTL Circuits

current in extremely sharp spikes at the clock edges. The VHF and UHF components of these spikes are not drawn from the power supply, but from the decoupling capacitor. If the decoupling circuit is not sufficiently low in inductance,  $V_{CC}$  will glitch at each clock edge. We suggest that a 0.1  $\mu$ F decoupler cap be used in a minimum-inductance configuration with the microcontroller. A minimum-inductance configuration is one that minimizes the area of the loop formed by the chip ( $V_{CC}$  to  $V_{SS}$ ), the traces to the decoupler cap, and the decoupler cap. PCB designers too often fail to understand that if the traces that connect the decoupler cap to the  $V_{CC}$  and  $V_{SS}$  pins aren't short and direct, the decoupler loses much of its effectiveness.

Overshoot and ringing in signal lines are potential sources of logic upsets. These can largely be controlled by circuit layout. Inserting small resistors (about  $100\Omega$ ) in series with signal lines that seem to need them will also help.

The sharp edges produced by high-speed CMOS can cause RFI problems. The severity of these problems is largely a function of the PCB layout. We don't mean to imply that all RFI problems can be solved by a better PCB layout. It may well be, for example, that in some RFI-sensitive designs high-speed CMOS is simply not the answer. But circuit layout is a critical factor in the noise performance of any electronic system, and more so in high-speed CMOS systems than others.

Circuit layout techniques for minimizing noise susceptibility and generation are discussed in References 3 through 6.

#### **UNUSED PINS**

CMOS input pins should not be left to float, but should always be pulled to one logic level or the other. If they float, they tend to float into the transition region between 0 and 1, where the pullup and pulldown devices in the input buffer are both conductive. This causes a significant increase in  $I_{CC}$ . A similar effect exists in HMOS circuits, but with less noticeable results.

In 80C51BH and 80C31BH designs, unused pins of Ports 1, 2, and 3 can be ignored, because they have internal pullups that will hold them at a valid Logic 1 level. Port 0 pins are different, however, in not having internal pullups (except during bus operations).

When the 80C51BH is in reset, the Port 0 pins are in a float state unless they are externally pulled up or down. If it's going to be held in reset for just a short time, the transient float state can probably be ignored. When it comes out of reset, the pins stay afloat unless

they are externally pulled either up or down. Alternatively, the software can internally write 0s to whatever Port 0 pins may be unused.

The same considerations are applicable to the 80C31BH with regards to reset. But when the 80C31BH comes out of reset, it commences bus operations, during which the logic levels at the pins are always well defined as high or low.

Consider the 80C31BH in the Power Down or Idle modes, however. In those modes it is not fetching instructions, and the Port 0 pins will float if not externally pulled high or low. The choice of whether to pull them high or low is the designer's. Normally it is sufficient to pull them up to  $V_{CC}$  with 10k resistors. But if power is going to be removed from circuits that are connected to the bus, it will be advisable to pull the bus pins down (normally with 10k resistors). Considerations involved in selecting pullup and pulldown resistor values are as follows.

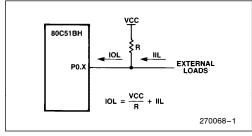

Figure 3a. Conditions defining the minimum value for R. P0.X is emitting a logic low. R must be large enough to not cause IOL to exceed data sheet specifications.

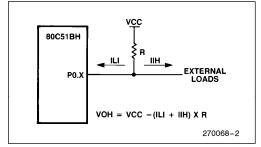

Figure 3b. Conditions defining the maximum value for R. P0.X is in a high impedance state. R must be small enough to keep  $V_{OH}$  acceptably high.

#### PULLUP RESISTORS

If a pullup resistor is to be used on a Port 0 pin, its minimum value is determined by  $I_{OL}$  requirements. If the pin is trying to emit a 0, then it will have to sink the current from the pullup resistor plus whatever other current may be sourced by other loads connected to the pin, as shown in Figure 3a, while maintaining a valid output low ( $V_{OL}$ ). To guarantee that the pin voltage will not exceed 0.45V, the resistor should be selected so that  $I_{OL}$  doesn't exceed the value specified on the data sheet. In most CMOS applications, the minimum value would be about 2k  $\Omega$ .

The maximum value you could use depends on how fast you want the pin to pull up after bus operations have ceased, and how high you want the  $V_{OH}$  level to be. The smaller the resistor the faster it pulls up. Its effect on the  $V_{OH}$  level is that  $V_{OH}=V_{CC}-(ILI+IH)\times R.$  ILI is the input leakage current to the Port 0 pin, and IIH is the input high current to the external loads, as shown in Figure 3b. Normally  $V_{OH}$  can be expected to reach 0.9  $V_{CC}$  if the pullup resistance does not exceed about 50k  $\Omega$ .

### **Pulldown Resistors**

If a pulldown resistor is to be used on a Port 0 pin, its minimum value is determined by  $V_{OH}$  requirements during bus operations, and its maximum value is in most cases determined by leakage current.

During bus operations the port uses internal pullups to emit 1s. The D.C. Characteristics in the data sheet list guaranteed  $V_{OH}$  levels for given  $I_{OH}$  currents. (The "-" sign in the  $I_{OH}$  value means the pin is sourcing that current to the external load, as shown in Figure 4.) To ensure the  $V_{OH}$  level listed in the data sheet, the resis-

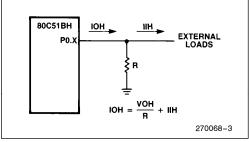

Figure 4a. Conditions defining the minimum value for R. P0.X is emitting a 1 in a bus operation. R must be large enough to not cause IOH to exceed data sheet specifications.

$$\frac{V_{OH}}{R} + I_{IH} \le |I_{OH}|$$

tor has to satisfy where  ${\bf I}_{IH}$  is the input high current to the external loads.

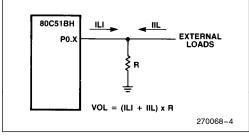

When the pin goes into a high impedance state, the pulldown resistor will have to sink leakage current from the pin, plus whatever other current may be sourced by other loads connected to the pin, as shown in Figure 4b. The Port 0 leakage current is  $I_{LI}$  on the data sheet. The resistor should be selected so that the voltage developed across it by these currents will be seen as a logic low by whatever circuits are connected to it (including the 80C51BH). In CMOS/CHMOS applications, 50k  $\Omega$  is normally a reasonable maximum value.

Figure 4b. Conditions defining the maximum value for R. P0.X is in a high impedance state. R must be small enough to keep VOL acceptably low.

#### DRIVE CAPABILITY OF THE INTERNAL PULLUPS

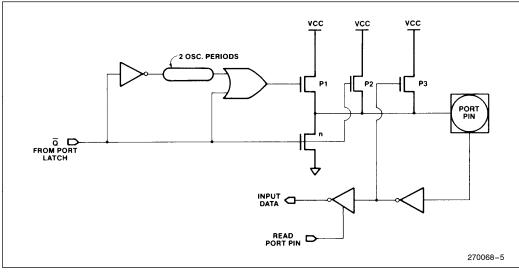

There's an important difference between HMOS and CHMOS port drivers. The pins of Ports 1, 2, and 3 of the CHMOS parts each have three pullups: strong, normal, and weak, as shown in Figure 5. The strong pullup (p1) is only used during 0-to-1 transitions, to hasten the transition. The weak pullup (p2) is on whenever the bit latch contains a 1. The "normal" pullup (p3) is controlled by the pin voltage itself.

The reason that p3 is controlled by the pin voltage is that if the pin is being used as an input, and the external source pulls it to a low, then turning off p3 makes for a lower I<sub>IL</sub>. The data sheet shows an "I<sub>TL</sub>" specification. This is the current that p3 will source during the time the pin voltage is making its 1-to-0 transition. This is what I<sub>IL</sub> would be if an input low at the pin didn't turn p3 off.

Note, however, that this p3 turn-off mechanism puts a restriction on the drive capacity of the pin if it's being used as an output. If you're trying to output a logic high, and the external load pulls the pin voltage below the pin's  $V_{IH}MIN$  spec, p3 might turn off, leaving only the weak p2 to provide drive to the load. To prevent this happening, you need to ensure that the load doesn't draw more than the  $I_{OH}$  spec for a valid  $V_{OH}$ . The idea is to make sure the pin voltage never falls below its own  $V_{IH}MIN$  specification.

Figure 5. 80C51BH Output Drivers for Ports 1, 2 and 3

#### AP-252

### POWER CONSUMPTION

The main reason for going to CMOS, of course, is to conserve power. (There are other reasons, but this is the main one.) Conserving power doesn't mean just reducing your electric bill. Nor does it necessarily relate to battery operation, although battery operation without CMOS is pretty unhandy. The main reason for conserving power is to be able to put more functionality into a smaller space. The reduced power consumption allows the use of smaller and lighter power supplies, and less heat being generated allows denser packaging of circuit components. Expensive fans and blowers can usually be eliminated.

A cooler running chip is also more reliable, since most random and wearout failures relate to die temperature. And finally, the lower power dissipation will allow more functions to be integrated onto the chip.

The reason CMOS consumes less power than NMOS is that when it's in a stable state there is no path of conduction from  $V_{CC}$  to  $V_{SS}$  except through various leakage paths. CMOS does draw current when it's changing states. How much current it draws depends on how often and how quickly it changes states.

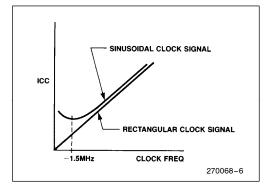

Figure 6. 80C51BH ICC vs. Clock Frequency

## intel

CMOS circuits draw current in sharp spikes during logical transitions. These current spikes are made up of two components. One is the current that flows during the transition time when pullup and pulldown FETs are both active. The average (DC) value of this component is larger when the transition times of the input signals are longer. For this reason, if the current draw is a critical factor in the design, slow rise and fall times should be avoided, even when the system speed doesn't seem to justify a need for nanosecond switching speeds.

The other component is the current that charges stray and load capacitance at the nodes of a CMOS logic gate. The average value of this current spike is its area (integral over time) multiplied by its rep rate. Its area is the amount of charge it takes to raise the node capacitance, C, to  $V_{CC}$ . That amount of charge is just C x  $V_{CC}$ . So the average value of the current spike is C x  $V_{CC}$  x f, where f is the clock frequency.

This component of current increases linearly with clock frequency. For minimal current draw, the 80C52BH-2 is spec'd to run at frequencies as low as 500 kHz.

Keep in mind, though, that other component of current that is due to slow rise and fall times. A sinusoid is not the optimal waveform to drive the XTAL1 pin with. Yet crystal oscillators, including the one on the 80C51BH, generate sinusoidal waveforms. Therefore, if the on-chip oscillator is being used, you can expect the device to draw more current at 500 kHz, than it does at 1.5 MHz, as shown in Figure 6. If you derive a good sharp square wave from an external oscillator, and use that to drive XTAL1, then the microcontroller will draw less current. But the external oscillator will probably make up the difference.

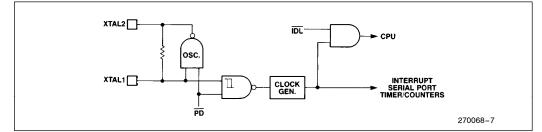

The 80C51BH has two power-saving features not available in the HMOS devices. These are the Idle and Power Down modes of operation. The on-chip hardware that implements these reduced power modes is shown in Figure 7. Both modes are invoked by software.

Figure 7. Oscillator and Clock Circuitry Showing Idle and Power Down Hardware

Idle: In the Idle Mode ( $\overline{IDL} = 0$  in Figure 7), the CPU puts itself to sleep by gating off its own clock. It doesn't stop the oscillator. It just stops the internal clock signal from getting to the CPU. Since the CPU draws 80 to 90 percent of the chip's power, shutting it off represents a fairly significant power savings. The on-chip periperals (timers, serial port, interrupts, etc.) and RAM continue to function as normal. The CPU status is preserved in its entirety: the Stack Pointer, Program Counter, Program Status Word, Accumulator, and all other registers maintain their data during Idle.

The Idle Mode is invoked by setting bit 0 (IDL) of the PCON register. PCON is not bit-addressable, so the bit has to be set by a byte operation, such as

ORL PCON,#1

The PCON register also contains flag bits GF0 and GF1, which can be used for any general purposes, or to give an indication if an interrupt occurred during normal operation or during Idle. In this application, the instruction that invokes Idle also sets one or both of the flag bits. Their status can then be checked in the interrupt routines.

While the device is in the Idle Mode, ALE and  $\overline{\text{PSEN}}$  emit logic high (V<sub>OH</sub>), as shown in Figure 8. This is so external EPROM can be deselected and have its output disabled.

The port pins hold the logical states they had at the time the Idle was activated. If the device was executing out of external program memory, Port 0 is left in a high impedance state and Port 2 continues to emit the high byte of the program counter (using the strong pullups to emit 1s). If the device was executing out of internal program memory, Ports 0 and 2 continue to emit whatever is in the P0 and P2 registers.

There are two ways to terminate Idle. Activation of any enabled interrupt will cause the hardware to clear bit 0 of the PCON register, terminating the Idle mode. The interrupt will be serviced, and following RETI the next instruction to be executed will be the one following the instruction that invoked Idle.

The other way is with a hardware reset. Since the clock oscillator is still running, RST only needs to be held active for two machine cycles (24 oscillator periods) to complete the reset. Note that this exit from Idle writes 1s to all the ports, initializes all SFRs to their reset values, and restarts program execution from location 0.

**Power Down:** In the Power Down Mode ( $\overline{PD} = 0$  in Figure 7), the CPU puts the whole chip to sleep by turning off the oscillator. In case it was running from an external oscillator, it also gates off the path to the internal phase generators, so no internal clock is generated even if the external oscillator is still running. The on-chip RAM, however, saves its data, as long as  $V_{CC}$  is maintained. In this mode the only  $I_{CC}$  that flows is leakage, which is normally in the micro-amp range.

The Power Down Mode is invoked by setting bit 1 in the PCON register, using a byte instruction such as

ORL PCON,#2

While the device is in Power Down, ALE and  $\overline{\text{PSEN}}$  emit lows (V<sub>OL</sub>), as shown in Figure 8. The reason they are designed to emit lows is so that power can be removed from the rest of the circuit, if desired, while the 80CS51BH is in its Power Down mode.

The port pins continue to emit whatever data was written to them. Note that Port 2 emits its P2 register data even if execution was from external program memory.

| Pin   | Interna  | I Execution     | Externa  | I Execution |  |

|-------|----------|-----------------|----------|-------------|--|

|       | Idle     | Idle Power Down |          | Power Down  |  |

| ALE   | 1        | 0               | 1        | 0           |  |

| PSEN/ | 1        | 0               | 1        | 0           |  |

| P0    | SFR Data | SFR Data        | High-Z   | High-Z      |  |

| P1    | SFR Data | SFR Data        | SFR Data | SFR Data    |  |

| P2    | SFR Data | SFR Data        | PCH      | SFR Data    |  |

| P3    | SFR Data | SFR Data        | SFR Data | SFR Data    |  |

Figure 8. Status of Pins in Idle and Power Down Modes. "SFR data" means the port pins emit their internal register data. "PCH" is the high byte of the Program Counter.

Port 0 also emits its P0 register data, but if execution was from external program memory, the P0 register data is FF. The oscillator is stopped, and the part remains in this state as long as  $V_{\rm CC}$  is held, and until it receives an external reset signal.

The only exit from Power Down is a hardware reset. Since the oscillator was stopped, RST must be held active long enough for the oscillator to re-start and stabilize. Then the reset function initializes all the Special Function Registers (ports, timers, etc.) to their reset values, and re-starts the program from location 0. Therefore, timer reloads, interrupt enables, baud rates, port status, etc. need to be re-established. Reset does not affect the content of the on-chip data RAM. If V<sub>CC</sub> was held during Power Down, the RAM data is still good.

### USING THE POWER DOWN MODE

The software-invoked Power Down feature offers a means of reducing the power consumption to a mere trickle in systems which are to remain dormant for some period of time, while retaining important data.

The user should give some thought to what state the port pins should be left in during the time the clock is stopped, and write those values to the port latches before invoking Power Down. If  $V_{CC}$  is going to be held to the entire circuit, one would want to write values to the port latches that would deselect peripherals before invoking Power Down. For example, if external memory is being used, the P2 SFR should be loaded with a value which will not generate an active chip select to any memory device.

In some applications,  $V_{CC}$  to part of the system may be shut off during Power Down, so that even quiescent and standby currents are eliminated. Signal lines that connect to those chips must be brought to a logic low, whether the chip in question is CMOS, NMOS, or TTL, before  $V_{CC}$  is shut off to them. CMOS pins have parasitic pn junctions to  $V_{CC}$ , which will be forward biased if  $V_{CC}$  is reduced to zero while the pin is held at a logic high. NMOS pins often have FETs that look like diodes to  $V_{CC}$ . TTL circuits may actually be damaged by an input high if  $V_{CC} = 0$ . That's why the 80C51BH outputs lows at ALE and PSEN during Power Down.

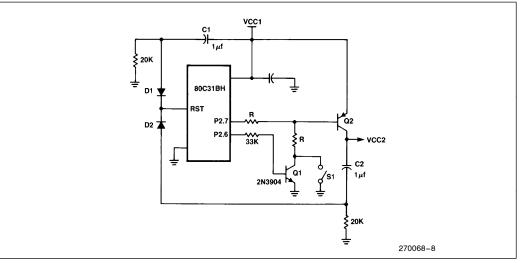

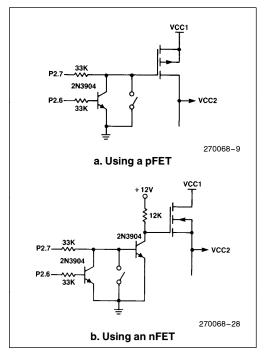

Figure 9 shows a circuit that can be used to turn  $V_{CC}$  off to part of the system during Power Down. The circuit will ensure that the secondary circuit is not de-energized until after the 80C31BH is in Power Down, and that the 80C31BH does not receive a reset (terminating the Power Down mode) before the secondary circuit is re-energized. Therefore, the program memory itself can be part of the secondary circuit.

Figure 9. The 80C31BH de-energizes part of the circuit (VCC2) when it goes into Power Down. Selections of R and Q2 depend on VCC2 current draw.

In Figure 9, when V<sub>CC</sub> is switched on to the 80C31BH, capacitor C1 provides a power-on reset. The reset function writes 1s to all the port pins. The 1 at P2.6 turns Q1 on, enabling V<sub>CC</sub> to the secondary circuit through transistor Q2. As the 80C31BH comes out of reset, Port 2 commences emitting the high byte of the Program Counter, which results in the P2.7 and P2.6 pins outputting 0s. The 0 at P2.7 ensures continuation of V<sub>CC</sub> to the secondary circuit.

The system software must now write a 1 to P2.7 and a 0 to P2.6 in the Port 2 SFR, P2. These values will not appear at the Port 2 pins as long as the device is fetching instructions from external program memory. However, whenever the 80C31BH goes into Power Down, these values will appear at the port pins, and will shut off both transistors, disabling  $V_{CC}$  to the secondary circuit.

Closing the switch S1 re-energizes the secondary circuit, and at the same time sends a reset through C2 to the 80C31BH to wake it up. The diode D1 is to prevent C1 from hogging current from C2 during this secondary reset. D2 prevents C2 from discharging through the RST pin when  $V_{CC}$  to the secondary circuit goes to zero.

Figure 10. Using Power MOSFETs to Control VCC2

### USING POWER MOSFETs to CONTROL V<sub>CC</sub>

Power MOSFETs are gaining in popularity (and availability). The easiest way to control  $V_{CC}$  is with a Logic Level pFET, as shown in Figure 10a. This circuit allows the full  $V_{CC}$  to be used to turn the device on. Unfortunately, power pFETs are not economically competitive with bipolar transistors of comparable ratings.

Power nFETs are both economical and available, and can be used in this application if a DC supply of higher voltage is available to drive the gate. Figure 10b shows how to implement a  $V_{CC}$  switch using a power nFET and a (nominally) + 12V supply. The problem here is that if the device is on, its source voltage is +5V. To maintain the on state, the gate has to be another 5 or 10V above that. The "12V" supply is not particularly critical. A minimally filtered, unregulated rectifier will suffice.

#### BATTERY BACKUP SYSTEMS

Here we consider circuits that normally draw power from the AC line, but switch to battery operation in the event of a power failure. We assume that in battery operation high-current loads will be allowed to die along with the AC power. The system may continue then with reduced functionality, monitoring a control transducer, perhaps, or driving an LCD. Or it may go into a bare-bones survival mode, in which critical data is saved but nothing else happens till AC power is restored.

In any case it is necessary to have some early warning of an impending power failure so that the system can arrange an orderly transfer to battery power. Early warning systems can operate by monitoring either the AC line voltage or the unregulated rectifier output, or even by monitoring the regulated DC voltage.

Monitoring the AC line voltage gives the earliest warning. That way you can know within one or two half-cycles of line frequency that AC power is down. In most cases you then have at least another half-cycle of line frequency before the regulated  $V_{CC}$  starts to fall. In a half-cycle of line frequency an 80C51BH can execute about 5,000 instructions—plenty of time to arrange an orderly transfer of power.

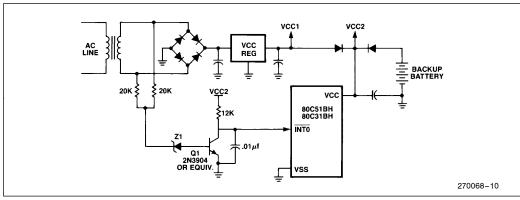

The circuit in Figure 11 uses a Zener diode to test the line voltage each half-cycle, and a junction transistor to pass the information on to the 80C51BH. (Obviously a voltage comparator with a suitable reference source can

Figure 11. Power Failure Detector with Battery Backup. When AC power fails, VCC1 goes down and VCC2 is held.

perform the same function, if one prefers.) The way it works is if the line voltage reaches an acceptably high level, it breaks over Z1, drives Q1 to saturation, and interrupts the 80C51BH. The interrupt would be transition-activated, in this application. The interrupt service routine reloads one of the C51BH's timers to a value that will make it roll over in something between one and two half-cycles of line frequency. As long as the line voltage is healthy, the timer never rolls over, because it is reloaded every half-cycle. If there is a single half-cycle in which the line voltage doesn't reach a high enough level to generate the interrupt, the timer rolls over and generates a **timer** interrupt.

The timer interrupt then commences the transition to battery backup. Critical data needs to be copied into protected RAM. Signals to circuits that are going to lose power must be written to logic low. Protected circuits (those powered by  $V_{CC}^2$ ) that communicate with unprotected circuits must be deselected. The microcontroller itself may be put into Idle, so that it can continue some level of interrupt-driven functionality, or it may be put into Power Down.

Note that if the CPU is going to invoke Power Down, the Special Function Registers may also need to be copied into protected RAM, since the reset that terminates the Power Down mode will also initialize all the SFRs to their reset values.

The circuit in Figure 11 does not show a wake-up mechanism. A number of choices are available, however. A pushbutton could be used to generate an interrupt, if the CPU is in Idle, or to activate reset, if the CPU is in Power Down. Automatic wake-up on power restoration is also possible. If the CPU is in Idle, it can continue to respond to any interrupts that might be generated by Q1. The interrupt service routine determines from the status of flag bits GF0 and GF1 in PCON that it is in Idle because there was a power outage. It can then sample  $V_{CC}$ 1 through a voltage comparator similar to Z1, Q1 in Figure 11. A satisfactory level of  $V_{CC}$ 1 would be indicated by the transistor being in saturation.

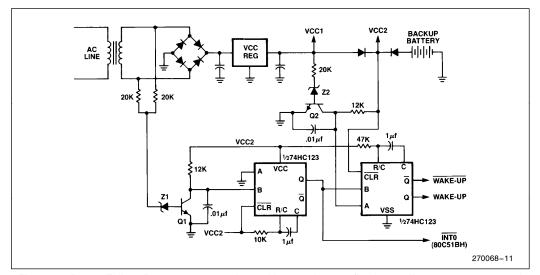

But perhaps you can't spare the timer that is the key to the operation of the circuit in Figure 11. In that case a retriggerable one-shot, triggered by the AC line voltage, can perform essentially the same function. Figure 12 shows an example of this type of power failure detector. A retriggerable one-shot (one half of a 74HC123) monitors the AC line voltage through transistor Q1. Q1 retriggers the one-shot every half-cycle of line frequency. If the output pulse width is between one and two halfcycles of line frequency, then a single missing or low half-cycle will generate an active low warning flag, which can be used to interrupt the microcontroller.

The interrupt routine takes care of the transition to battery backup. From this point  $V_{CC}1$  may or may not actually drop out. The missing half-cycle of line voltage that caused the power down sequence may have been nothing more than a short glitch. If the AC line comes back strong enough to trigger the one-shot while  $V_{CC}1$ is still up (as indicated by the state of transistor Q2), then the other half of the 74HC123 will generate a wake-up signal.

Figure 12. Power Failure Detector uses retriggerable one-shots to flag impending power outage and generate automatic wake-up when power returns.

Having been awakened, the 80C51BH will stay awake for at least another half-cycle of line frequency (another 5,000 or so instructions) before possibly being told to arrange another transfer of power. Consequently, if the line voltage is jittering erratically around the switchover point (determined by diode Z1), the system will limp along executing in half-cycle units of line frequency.

On the other hand, if the power outage is real and lengthy,  $V_{\rm CC}$ 1 will eventually fall below the level at which the backup battery takes over. The backup battery maintains power to the 80C51BH, and to the 74HC123, and to whatever other circuits are being protected during this outage. The battery voltage must be high enough to maintain  $V_{\rm CC}$ MIN specs to the 80C51BH.

If the microcontroller is an 80C31BH, executing out of external ROM, and if the C31BH is put into Idle during the power outage, then the external ROM must also be supplied by the battery. On the other hand, if the C31BH is put into Power Down during the outage, then the ROM can be allowed to die with the AC power. The considerations here are the same as in Figure 9:  $V_{CC}$  to the ROM is still up at the time Power Down is invoked, and we must ensure (through selection of diode Z2 in Figure 12) that the 80C31BH is not awakened till ROM power is back in spec.

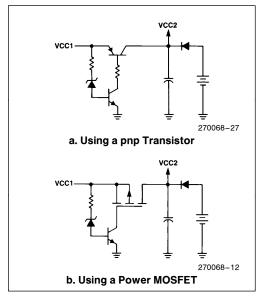

### POWER SWITCHOVER CIRCUITS

Battery backup systems need to have a way for the protected circuits to draw power from the line-operated power supply when that source is available, and to switch over to battery power when required. The switchover circuit is simple if the entire system is to be battery powered in the event of a line power outage. In that case a pair of diodes suffice, as shown in Figure 12, provided  $V_{\rm CC}$ MIN specs are still met after the diode drop has been subtracted from its respective power source.

The situation becomes more complicated when part of the circuit is going to be allowed to die when the AC power goes out. In that case it is difficult to maintain equal  $V_{CCS}$  to protected and unprotected circuits (and possibly dangerous not to).

The problem can be alleviated by using a Schottky diode instead of a 1N4001, for its lower forward voltage drop. The 1N5820, for example, has a foward drop of about 0.35V at 1A.

Other solutions are to use a transistor or power MOS-FET switch, as shown in Figure 13. With minor modifications this switch can be controlled by port pins.

Figure 13. Power Switchover Ckts.

### 80C31BH + CHMOS EPROM

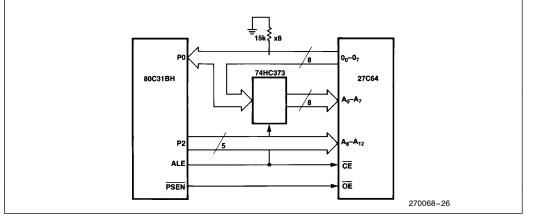

The 27C64 and 87C64 are Intel's 8K byte CHMOS EPROMs. The 27C64 requires an external address latch, and can be used with the 80C31BH as shown in Figure 14a. In most 8031 + 2764 (HMOS) appli-

cations, the 2764's Chip Enable ( $\overline{\text{CE}}$ ) pin is hardwired to ground (since it's normally the only program memory on the bus). This can be done with the CHMOS versions as well, but there is some advantage in connecting  $\overline{\text{CE}}$  to ALE, as shown in Figure 14a. The advantage is that if the 80C31BH is put into Idle mode, since ALE goes to a 1 in that mode, the 27C64 will be deselected and go into a low current standby mode.

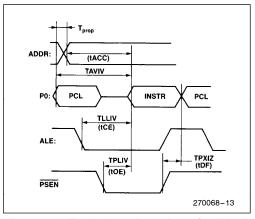

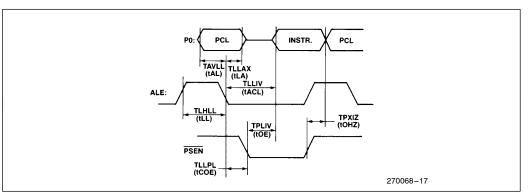

The timing waveforms for this configuration are shown in Figure 14b. In Figure 14b the signals and timing parameters in parenthesis are those of the 27C64, and the others are of the 80C31BH, except Tprop is a parameter of the address latch. The requirements for timing compatibility are

| TAVIV - | Tprop > | tACC |

|---------|---------|------|

|         | TLLIV > | tCE  |

|         | TPLIV > | tOE  |

|         | TPXIZ > | tDF  |

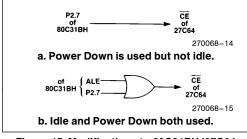

If the application is going to use the Power Down mode then we have another consideration: In Idle,  $ALE = \overline{PSEN} = 1$ , and in Power Down,  $ALE = \overline{PSEN} = 0$ . In a realistic application there are likely to be more chips in the circuit than are shown in Figure 14, and it is likely that the nonessential ones will have their V<sub>CC</sub> removed while the CPU is in Power Down. In that case the EPROM and the address latch should be among the chips that have V<sub>CC</sub> removed, and logic lows are exactly what are required at ALE and <u>PSEN</u>.

But if  $V_{CC}$  is going to be maintained to the EPROM during Power Down, then it will be necessary to de-

Figure 14a. 80C31BH + 27C64

Figure 14b. Timing Waveforms for 80C31BH + 27C64

select the EPROM when the CPU is in Power Down. If Idle is never invoked,  $\overline{CE}$  of the EPROM can be connected to P2.7 of the 80C31BH, as shown in Figure 15a. In normal operation, P2.7 will be emitting the MSB of the Program Counter, which is 0 if the program contains less than 32K of code. Then when the CPU goes into Power Down, the Port 2 pins emit P2 SFR data, which puts a 1 at P2.7, thus deselecting the EPROM.

If Idle and Power Down are both going to be used,  $\overline{CE}$  of the EPROM can be driven by the logical OR of ALE and P2.7, as shown in Figure 15b. In Idle, ALE = 1 will deselect the EPROM, and in Power Down, P2.7 = 1 will deselect it.

Figure 15. Modifications to 80C31BH/27C64 Interface

Pulldown resistors are shown in Figure 14a under the assumption that something on the bus is going to have its  $V_{CC}$  removed during Power Down. If this is not the case, pullups can be used as well as pulldowns.

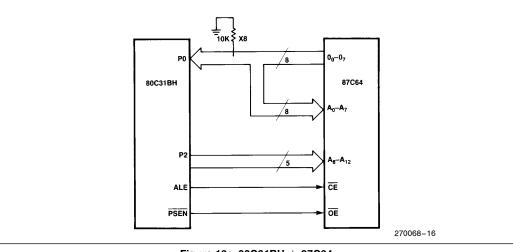

The 87C64 is like the 27C64 except that it has an onchip address latch. The Port 0 pins are tied to both address and data pins of the 87C64, as shown in Figure 16a. ALE drives the EPROM's ALE/ $\overline{CS}$  input. During ALE high, the address information is allowed to flow into the EPROM and begin accessing the code byte. On the falling edge of ALE the address byte is internally latched. The A0-A7 inputs are then ignored and the same bus lines are used to transmit the fetched code byte from the 00-07 pins back to the 80C31BH.

The timing waveforms for this configuration are shown in Figure 16b. In Figure 16b the signals and timing parameters in parentheses are those of the 87C64, and the others are of the 80C31BH. The requirements for timing compatibility are

| TLHLL > tLL  |

|--------------|

| TAVLL > tAL  |

| TLLAX > tLA  |

| TLLIV > tACL |

| TPLIV > tOE  |

| TLLPL > tCOE |

| TPXIZ > tOHZ |

|              |

The same considerations apply to the 87C64 as to the 27C64 with regards to the Idle and Power Down modes. Basically you want  $\overline{CS} = 1$  if  $V_{CC}$  is maintained to the EPROM, and  $\overline{CS} = \overline{OE} = 0$  if  $V_{CC}$  is removed.

#### SCANNING A KEYBOARD

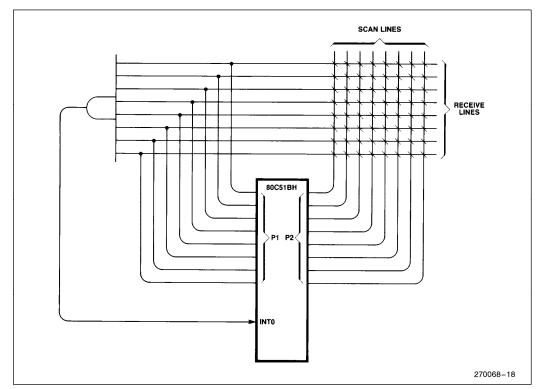

There are many different kinds of keyboards, but alphanumeric keyboards generally consist of a matrix of 8 scan lines and 8 receive lines as shown in Figure 17. Each set of lines connects to one port of the microcontroller. The software has written 0s to the scan lines, and 1s to the receive lines. Pressing a key connects a scan line to a receive line, thus pulling the receive line to a logic low.

The 8 receive lines are ANDed to one of the external interrupt pins, so that pulling any of the receive lines low generates an interrupt. The interrupt service routine has to identify the pressed key, if only one key is down, and convert that information to some useful output. If more than one key in the line matrix is found to be pressed, no action is taken. (This is a "two key lockout" scheme.)

### AP-252

On some keyboards, certain keys (Shift, Control, Escape, etc.) are not a part of the line matrix. These keys would connect directly to a port pin on the microcontroller, and would not cause lock-out if pressed simultaneously with a matrix key, nor generate an interrupt if pressed singly.

Normally the microcontroller would be in idle mode when a key has not been pressed, and another task is not in progress. Pressing a matrix key generates an interrupt, which terminates the Idle. The interrupt service routine would first call a 30 ms (or so) delay to debounce the key, and then set about the task of identifying which key is down.

First, the current state of the receive lines is latched into an internal register. If a single key is down, all but one of the lines would be read as 1s. Then 0s are written to the receive lines and 1s to the scan lines, and the scan lines are read. If a single key is down, all but one of

Figure 16a. 80C31BH + 87C64

Figure 16b. Timing Waveforms for 80C31BH + 87C64

these lines would be read as 1s. By locating the single 0 in each set of lines, the pressed key can be identified. If more than one matrix key is down, one or both sets of lines will contain multiple 0s.

A subroutine is used to determine which of 8 bits in either set of lines is 0, and whether more than one bit is 0. Figure 18 shows a subroutine (SCAN) which does that using the 8051's bit-addressing capability. To use the subroutine, move the line data into a bit-addressable RAM location named LINE, and call the SCAN routine. The number of LINE bits which are zero is returned in ZERO\_COUNTER. If only one bit is zero, its number (1 through 8) is returned in ZERO\_BIT.

The interrupt service routine that is executed in response to a key closure might then be as follows:

RESPONSE\_TO\_KEY\_CLOSURE: CALL DEBOUNCE\_DELAY MOV LINE, Pl; ;See Figure 17. CALL SCAN ZERO\_COUNTER, REJECT DJNZ MOV ADDRESS, ZERO\_BIT MOV P2,#OFFH; ;See Figure 17. MOV P1,#0 MOV LINE, P2 CALL SCAN ZERO\_COUNTER, REJECT DJNZ ХСН A,ZERO\_BIT SWAP А ORL ADDRESS,A XCH A,ZERO\_BIT MOV Pl,#OFFH MOV P2,#0 REJECT: CLR EX0 RETI

Figure 17. Scanning a Keyboard

#### AP-252

AP-252

## intel

| SCAN:  | MOV |                | ZERO_COUNTER counts the number of Os in LINE. |           |

|--------|-----|----------------|-----------------------------------------------|-----------|

|        | JB  |                | Test LINE bit O.                              |           |

|        | INC |                | If LINE.O = O, increment ZERO_COUNTER         |           |

|        | MOV | ZERO_BIT,#1 ;  |                                               |           |

| ONE:   | JB  |                | Procedure continues for other LINE bits.      |           |

|        | INC | ZERO_COUNTER   |                                               |           |

|        | MOV |                | Line number 2 is active.                      |           |

| TWO:   | JB  | LINE. 2, THREE |                                               |           |

|        | INC | ZERO_COUNTER   |                                               |           |

|        | MOV |                | Line number 3 is active.                      |           |

| THREE: | JB  | LINE. 3, FOUR  |                                               |           |

|        | INC | ZERO_COUNTER   |                                               |           |

|        | MOV |                | Line number 4 is active.                      |           |

| FOUR:  | JB  | LINE. 4, FIVE  |                                               |           |

|        | INC | ZERO_COUNTER   |                                               |           |

|        | MOV |                | Line number 5 is active.                      |           |

| FIVE:  | JB  | LINE. 5, SIX   |                                               |           |

|        | INC | ZERO_COUNTER   |                                               |           |

|        | MOV | ZERO_BIT,#6 ;  | Line number 6 is active.                      |           |

| SIX:   | JB  | LINE. 6, SEVEN |                                               |           |

|        | INC | ZERO_COUNTER   |                                               |           |

|        | MOV | ZERO_BIT,#7 ;  | Line number 7 is active.                      |           |

| SEVEN: | JB  | LINE. 7, EIGHT |                                               |           |

|        | INC | ZERO_COUNTER   |                                               |           |

|        | MOV | ZERO_BIT,#8 ;  | Line number 8 is active.                      |           |

| EIGHT: | RET |                |                                               |           |

|        |     |                |                                               | 270068-19 |

Figure 18. Subroutine SCAN Determines Which of 8 Bits in LINE is Zero

Notice that RESPONSE\_TO\_KEY\_CLOSURE does not change the Accumulator, the PSW, nor any of the registers R0 through R7. Neither do SCAN or DE-BOUNCE\_DELAY.

What we come out with then is a one-byte key address (ADDRESS) which identifies the pressed key. The key's scan line number is in the upper nibble of AD-DRESS, and its receive line number is in the lower nibble. ADDRESS can be used in a look-up table to generate a key code to transmit to a host computer, and/or to a display device.

The keyboard interrupt itself must be edge-triggered, rather than level-activated, so that the interrupt routine is invoked when a key is pressed, and is not constantly being repeated as long as the key is held down. In edgetriggered mode, the on-chip hardware clears the interrupt flag (EXO, in this case) as the service routine is being vectored to. In this application, however, contact bounce will cause several more edges to occur after the service routine has been vectored to, during the DE-BOUNCE\_DELAY routine. Consequently it is necessary to clear EXO again in software before executing RETI.

The debounce delay routine also takes advantage of the Idle mode. In this routine a timer must be preloaded with a value appropriate to the desired length of delay. This would be

timer preload =

$$\frac{(\text{osc kHz}) \times (\text{delay time ms})}{12}$$

For example, with a 3.58 MHz oscillator frequency, a 30 ms delay could be obtained using a preload value of -8950, or DD0A, in hex digits.

In the debounce delay routine (Figure 19), the timer interrupt is enabled and set to a higher priority than the keyboard interrupt, because as we invoke Idle, the keyboard interrupt is still "in progress". An interrupt of the same priority will not be acknowledged, and will not terminate the Idle mode. With the timer interrupt set to priority 1, while the keyboard interrupt is a priority 0, the timer interrupt, when it occurs, will be acknowledged and will wake up the CPU. The timer interrupt service routine does not itself have to do anything. The service routine might be nothing more than a single RETI instruction. RETI from the timer interrupt service routine, which shuts down the timer and returns execution to the keyboard service routine.

### **DRIVING AN LCD**

An LCD (Liquid Crystal Display) consists of a backplane and any number of segments or dots which will be used to form the image being displayed. Applying a voltage (nominally 4 or 5V) between any segment and the backplane causes the segment to darken. The only catch is that the polarity of the applied voltage has to be periodically reversed, or else a chemical reac-

|          |            | TL1, #TL1_PRELOAD |    |                                         |  |

|----------|------------|-------------------|----|-----------------------------------------|--|

| M        | 10V        | TH1, #TH1_PRELOAD | i. | Preload high byte.                      |  |

| S        | ETB        | ET1               | i  | Enable Timer 1 interrupt.               |  |

| S        | <b>ETB</b> | PT1               | ;  | Set Timer 1 interrupt to high priority. |  |

| S        | SETB       | TR1               | i  | Start timer running.                    |  |

| 0        | RL         | PCON, #1          | i  | Invoke Idle mode.                       |  |

| 4        |            |                   |    |                                         |  |

| ; The ne | ext inst   | ruction will not  | be | e executed until the delay times out.   |  |

| 3        |            |                   |    |                                         |  |

| С        | LR         | TR1               | i  | Stop the timer.                         |  |

| С        | LR         | PT1               | ;  | Back to priority O (if desired).        |  |

| c        | LR         | ET1               | ;  | Disable Timer 1 interrupt (if desired). |  |

|          | ET         |                   |    | Continue keyboard scan.                 |  |

tion takes place in the LCD which causes deterioration and eventual failure of the liquid crystal.

To prevent this happening, the backplane and all the segments are driven with an AC signal, which is derived from a rectangular voltage waveform. If a segment is to be "off" it is driven by the same waveform as the backplane. Thus it is always at backplane potential. If the segment is to be "on" it is driven with a waveform that is the inverse of the backplane waveform. Thus it has about 5V of periodically changing polarity between it and the backplane.

With a little software overhead, the 80C51BH can perform this task without the need for additional LCD drivers. The only drawback is that each LCD segment uses up one port pin, and the backplane uses one more. If more than, say, two 7-segment digits are being driven, there aren't many port pins left for other tasks. Nevertheless, assuming a given application leaves enough port pins available to support this task, the considerations for driving the LCD are as follows.

Suppose, for example, it is a 2-digit display with a decimal point. One port (TENS\_DIGIT) connects to the 7 segments of the tens digit plus the backplane. Another port (ONES\_DIGIT) connects to a decimal point plus the 7 segments of the ones digit.

One of the 80C51BH's timers is used to mark off halfperiods of the drive voltage waveform. The LCD drive waveform should have a rep rate between 30 and 100 Hz, but it's not very critical. A half-period of 12 ms will set the rep rate to about 42 Hz. The preload/reload value to get 12 ms to rollover is the 2's complement negative of the oscillator frequency in kHz: if the oscillator frequency is 3.58 MHz, the reload value is -3580, or F204 in hex digits.

Now, the 80C51BH would normally be in Idle, to conserve power, during the time that the LCD and other tasks are not requiring servicing. When the timer rolls over it generates an interrupt, which brings the 80C51BH out of Idle. The service routine reloads the timer (for the next rollover), and inverts the logic levels of all the pins that are connected to the LCD. It might look like this:

LCD\_DRIVE\_INTERRUPT:

| MOV  | TL1,#LOW( - XTAL_FREQ)  |

|------|-------------------------|

| MOV  | TH1,#HIGH( - XTAL_FREQ) |

| XRL  | TENS_DIGIT,#OFFH        |

| XRL  | ONES_DIGIT,#OFFH        |

| RETI |                         |

To update the display, one would use a look-up table to generate the characters. In the table, "on" segments are represented as 1s, and "off" segments as 0s. The backplane bit is represented as a 0. The quantity to be displayed is stored in RAM as a BCD value. The look-up table operates on the low nibble of the BCD value, and produces the bit pattern that is to be written to either the ones digit or the tens digit. Before the new patterns can be written to the LCD, the LCD drive interrupt has to be disabled. That is to prevent a polarity reversal from taking place between the times the two digits are written. An update subroutine is shown in Figure 20.

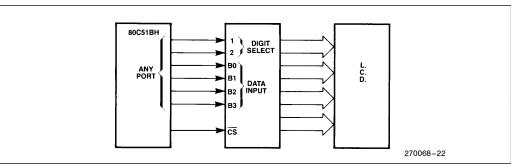

#### USING AN LCD DRIVER

As was noted, driving an LCD directly with an 80C51BH uses a lot of port pins. LCD drivers are available in CMOS to interface an 80C51BH to a 4-digit display using only 7 of the C51BH's I/O pins. Basically, the C51BH tells the LCD driver what digit is to be displayed (4 bits) and what position it is to be displayed in (2 bits), and toggles a Chip Select pin to tell the driver to latch this information. The LCD driver generates the display characters (hex digits), and takes care of the polarity reversals using its own RC oscillator to generate the timing.

Figure 21a shows an 80C51BH working with an ICM7211M to drive a 4-digit LCD, and the software that updates the display.

One could equally well send information to the LCD driver over the bus. In that case, one would set up the Accumulator with the digit select and data input bits, and execute a MOVX@ R0,A instruction. The LCD driver's chip select would be driven by the CPU's  $\overline{WR}$  signal. This is a little easier in software than the direct bit manipulation shown in Figure 21a. However, it uses more I/O pins, unless there is already some external memory involved. In that case, no **extra** pins are used up by adding the LCD driver to the bus.

### **RESONANT TRANSDUCERS**

Analog transducers are often used to convert the value of a physical property, such as temperature, pressure, etc., to an analog voltage. These kinds of transducers then require an analog-to-digital converter to put the measurement into a form that is compatible with a digital control system. Another kind of transducer is now becoming available that encodes the value of the physical property into a signal that can be directly read by a digital control system. These devices are called resonant transducers.

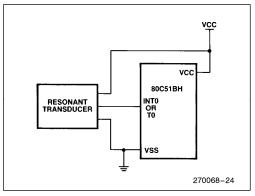

Resonant transducers are oscillators whose frequency depends in a known way on the physical property being measured. These devices output a train of rectangular pulses whose repetition rate encodes the value of the quantity being measured. The pulses can in most cases be fed directly into the 80C51BH, which then measures either the frequency or period of the incoming signal, basing the measurement on the accuracy of its own clock oscillator. The 80C51BH can even do this in its sleep; that is, in Idle. When the frequency or period measurement is completed, the C51BH wakes itself up for a very short time to perform a sanity check on the measurement and convert it in software to any scaling of the measured quantity that may be desired. The software conversion can include corrections for nonlinearities in the transducer's transfer function.

Resolution is also controlled by software, and can even be dynamically varied to meet changing needs as a situation becomes more critical. For example, in a process controller you can increase your resolution ("fine tune" the control, as it were) as the process approaches its target.

The nominal reference frequency of the output signal from these devices is in the range of 20 Hz to 500 kHz, depending on the design. Transducers are available that have a full scale frequency shift 2 to 1. The transducer operates from a supply voltage range of 3V to 20V, which means it can operate from the same supply voltage as the 80C51BH. At 5V, the transducer draws less than 5 mA (Reference 7). It can normally be connected directly to one of the C51BH's port pins, as shown in Figure 22.

#### FREQUENCY MEASUREMENTS

Measuring a frequency means counting pulses for a known sample time. Two timer/counters can be used, one to mark off the sample time and one to count pulses. If the frequency being counted doesn't exceed 50 kHz or so, one may equally well connect the transducer signal to one of the external interrupt pins, and count pulses in software. That frees up one timer, with very little cost in CPU time.

The count that is directly obtained is TxF, where T is the sample time and F is the frequency. The full scale

| UPDATE_LCD: |                      |   |                                       |           |

|-------------|----------------------|---|---------------------------------------|-----------|

| CLR         | ET1                  |   | Disable LCD drive interrupt.          |           |

| MOV         | DPTR, #TABLE_ADDRESS |   | Look-up table begins at TABLE_ADDRESS |           |

| MOV         | A, BCD_VALUE         | ; | Digits to be displayed.               |           |

| SWAP        | A _                  | ; | Move tens digit to low nibble.        |           |

| ANL.        | A, #OFH              | ; | Mask off high nibble.                 |           |

| MOVC        | A, @A+DPTR           | ; | Tens digit pattern to accumulator.    |           |

| MOV         | TENS_DIGIT, A        | ; | Update LCD tens digit.                |           |

| MOV         | A, BCD_VALUE         | i | Digits to be displayed.               |           |

| ANL         | A, #OFH              | i | Mask off tens digit.                  |           |

| MOVC        | A, @A+DPTR           | ; | Ones digit pattern to accumulator.    |           |

| MOV         | C, DECIMAL_POINT     | 1 | Add decimal point to segment          |           |

| MOV         | ACC. 7, C            | i | pattern. Update LCD decimal point     |           |

| MOV         | ONES DIGIT, A        | ; | and ones digit.                       |           |

| SETB        | ET1                  | i | Re-enable LCD drive interrupt.        |           |

| RET         |                      |   |                                       |           |

|             |                      |   |                                       | 270068-21 |

Figure 20. UPDATE\_LCD Routine Writes Two Digits to an LCD

range is Tx(Fmax-Fmin). For n-bit resolution

$$1 \text{ LSB} = \frac{\text{Tx}(\text{Fmax-Fmin})}{2^{n}}$$

Therefore the sample time required for n-bit resolution is

$$T=\frac{2^n}{Fmax\text{-}Fmin}$$

For example, 8-bit resolution in the measurement of a frequency that varies between 7 kHz and 9 kHz would require, according to this formula, a sample time of 128 ms. The maximum acceptable frequency count would be 128 ms  $\times$  9 kHz = 1152 counts. The minimum would be 896 counts. Subtracting 896 from each frequency count (or presetting the frequency counter to -896 = 0 FC80H) would allow the frequency to be reported on a scale of 0 to FF in hex digits.

Figure 21a. Using an LCD Driver

| UPDATE_LCD:     |                  |                                            |           |

|-----------------|------------------|--------------------------------------------|-----------|

| MOV             | A, DISPLAY HI ;  | High byte of 4-digit display.              |           |

| SETB            | DIGIT SELECT 2 ; | Select leftmost digit of LCD.              |           |

| SETB            | DIGIT SELECT 1 ; | (Digit address = 11B.)                     |           |

| CALL            |                  | High nibble of high byte to selected digit |           |

| CLR             |                  | Select second digit of LCD (address = 10B) |           |

| CALL            |                  | Low nibble of high byte to selected digit. |           |

| MOV             |                  | Low byte of 4-digit display.               |           |

| CLR             |                  | Select third digit of LCD.                 |           |

| SETB            |                  | (Digit address = O1B.)                     |           |

| CALL            |                  | High nibble of low byte to selected digit. |           |

| CLR             |                  | Select fourth digit (address = OOB).       |           |

| CALL            |                  | Low nibble of low byte to selected digit.  |           |

| RET             | 3.111 ()         |                                            |           |

|                 |                  |                                            |           |

| SHIFT_AND_LOAD: |                  |                                            |           |

| REC             | A                | ; MSB to carry bit (CY).                   |           |

| MOV             | DATA_INPUT_B3, C | ; CY to Data Input pin B3.                 |           |

| RLC             | Α                | ; Next bit to CY.                          |           |

| MOV             | DATA INPUT B2, C | ; CY to Data Input pin B2.                 |           |

| RLC             | Α                | ; Next bit to CY.                          |           |

| MOV             | DATA INPUT B1, C | ; CY to Data Input pin B1.                 |           |

| RLC             | A                | ; Last bit to CY.                          |           |

| MOV             | DATA INPUT BO, C | ; CY to Data Input pin BO.                 |           |

| CLR             | CHIP SELECT      | ; Toggle Chip Select.                      |           |

| SETB            | CHIP SELECT      | ; O-to-1 transition latches info.          |           |

| RET             |                  |                                            |           |

|                 |                  |                                            | 270068-23 |

Figure 21b. UPDATE\_LCD Routine Writes 4 Digits to an LCD Driver

Figure 22. Resonant Transducer Does Not Require an A/D Converter

To implement the measurement, one timer is used to establish the sample time. The timer is preset to a value that causes it to roll over at the end of the sample time, generating an interrupt and waking the CPU from its Idle mode. The required preset value is the 2's complement negative of the sample time measured in machine cycles. The conversion from sample time to machine cycles is to multiply it by 1/12 the clock frequency. For example, if the clock frequency is 12 MHz, then a sample time of 128 ms is

$(128 \text{ ms}) \times (12000 \text{ kHz})/12 = 128000 \text{ machine cycles}.$

Then the required preset value to cause the timer to roll over in 128 ms is

-128000 = FE0C00, in hex digits.

Note that the preset value is 3 bytes wide whereas the timer is only 2 bytes wide. This means the timer must be augmented in software in the timer interrupt routine to three bytes. The 80C51BH has a DJNZ instruction (decrement and jump if not zero) that makes it easier to code the third timer byte to count down instead of up. If the third timer byte counts down, its reload value is the 2's complement of what it would be for an up-counter. For example, if the 2's complement of the sample time is FE0C00, then the reload value for the third timer byte would be 02, instead of FE. The timer interrupt routine might then be:

```

TIMER_INTERRUPT_ROUTINE:

DNJ7

THIRD_TIMER_BYTE, OUT

MOV

TL0,#0

MOV

THO,#OCH

MOV

THIRD_TIMERBYTE,#2

MOV

FREQUENCY, COUNTER_LO

;Preset COUNTER to -896:

COUNTER_LO,#80H

MOV

MOV

COUNTER_HI,#OFCH

OUT:

RETI

```

intel

At this point the value of the frequency of the transducer signal, measured to 8 bit resolution, is contained in FREQUENCY. Note that the timer can be reloaded on the fly. Note too that the timer can be reloaded on the fly. Note too that for 8-bit resolution only the low byte of the frequency counter needs to be read, since the high byte is necessarily 0. However, one may want to test the high byte to ensure that it is zero, as a sanity check on the data. Both bytes, of course must be reloaded.

#### PERIOD MEASUREMENTS

Measuring the period of the transducer signal means measuring the total elapsed time over a known number, N, of transducer pulses. The quantity that is directly measured is NT, where T is the period of the transducer signal in *machine cycles*. The relationship between T in machine cycles and the transducer frequency F in arbitrary frequency units is

$$T = \frac{Fxtal}{F} \times (1/12),$$

where Fxtal is the 80C51BH clock frequency, in the same units as F.

The full scale range then is Nx (Tmax-Tmin). For n-bit resolution.

$$1 \text{ LSB} = \frac{\text{Ns(Tmax-Tmin)}}{2^{n}}.$$

Therefore the number of periods over which the elapsed time should be measured is

$$N = \frac{2^n}{Tmax-Tmin}$$

However, N must also be an integer. It is logical to evaluate the above formula (don't forget Tmax and Tmin have to be in machine cycles) and select for N the next higher integer. This selection gives a period measurement that has somewhat more than n-bit resolution, but it can be scaled back if desired.

For example, suppose we want 8-bit resolution in the measurement of the period of a signal whose frequency varies from 7.1 kHz to 9 kHz. If the clock frequency is 12 MHz, then Tmax is (12000 kHz/7.1 kHz) x (1/12) = 141 machine cycles. Tmin is 111 machine cycles. The required value for N, then, is 256/(141-111) = 8.53 periods, according to the formula. Using N = 9 periods will give a maximum NT value of 141 x 9 = 1269 machine cycles. A lookup table can be used to

scale these values back to a range of 0 to 255, giving precisely the 8-bit resolution desired.

To implement the measurement, one timer is used to measure the elapsed time, NT. The transducer is connected to one of the external interrupt pins, and this interrupt is configured to the transition-activated mode. In the transition-activated mode every 1-to-0 transition in the transducer output will generate an interrupt. The interrupt routine counts transducer pulses, and when it gets to the predetermined N, it reads and clears the timer. For the specific example cited above, the interrupt routine might be:

#### INTERRUPT\_RESPONSE:

|       | DJNZ | N,OUT        |

|-------|------|--------------|

|       | MOV  | N,#9         |

|       | CLR  | EA           |

|       | CLR  | TR1          |

|       | MOV  | NT_LO,TL1    |

|       | MOV  | NT_HI,TH1    |

|       | MOV  | TL1,#9       |

|       | MOV  | TH1,#O       |

|       | SETB | TR1          |

|       | SETB | EA           |

|       | CALL | LOOKUP_TABLE |

| 0UT : | RETI |              |

In this routine a pulse counter N is decremented from its preset value, 9, to zero. When the counter gets to zero it is reloaded to 9. Then all interrupts are blocked for a short time while the timer is read and cleared. The timer is stopped during the read and clear operations, so "clearing" it actually means presetting it to 9, to make up for the 9 machine cycles that are missed while the timer is stopped.

The subroutine LOOKUP\_TABLE is used to scale the measurement back to the desired 8-bit resolution. It can also include built-in corrections for errors or nonlinearities in the transducer's transfer function.

The subroutine uses the MOVC A, @ A + DPTR instruction to access the table, which contains 270 entries commencing at the 16-bit address referred to as TABLE. The subroutine must compute the address of the table entry that corresponds to the measured value of NT. This address is

$\mathsf{DPTR} = \mathsf{TABL} + \mathsf{NT} - \mathsf{NTMIN},$

where NTMIN = 999, in this specific example.

LOOKUP\_TABLE:

| PUSH | ACC                  |

|------|----------------------|

| PUSH | PSW                  |

| MOV  | A,#LOW(TABLE-NTMIN)  |

| ADD  | A,NT_LO              |

| MOV  | DPL,A                |

| MOV  | A,#HIGH(TABLE-NMTIN) |

|      |                      |

| ADDC | A,NT_HI   |

|------|-----------|

| MOV  | DPH,A     |

| CLR  | Α         |

| MOVC | A,@A+DTPR |

| MOV  | PERIOD,A  |

| POP  | PSW       |

| POP  | ACC       |

| RET  |           |

At this point the value of the period of the transducer signal, measured to 8 bit resolution, is contained in PE-RIOD.

### PULSE WIDTH MEASUREMENTS

The 80C51BH timers have an operating mode which is particularly suited to pulse width measurements, and will be useful in these applications if the transducer signal has a fixed duty cycle.

In this mode the timer is turned on by the on-chip circuitry in response to an input high at the external interrupt pin, and off by an input low, and it can do this while the 80C51BH is in Idle. (The "GATE" mode of timer operation is described in the Intel Microcontroller Handbook.) The external interrupt itself can be enabled, so the same 1-to-0 transition from the transducer that turns off the timer also generates an interrupt. The interrupt routine then reads and resets the timer.

The advantage of this method is that the transducer signal has direct access to the timer gate, with the result that variations in interrupt response time have no effect on the measurement.