## 8XC151SA and 8XC151SB Hardware Description

June 1996

Order Number: 272832-001

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

\*Other brands and names are the property of their respective owners.

†Since publication of documents referenced in this document, registration of the Pentium, OverDrive and iCOMP trademarks has been issued to Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

COPYRIGHT © INTEL CORPORATION, 1996

## HARDWARE DESCRIPTION OF THE 8XC151SX

| CONTENTS                                                        | PAGE |

|-----------------------------------------------------------------|------|

| 1.0 INTRODUCTION                                                | 1    |

| 2.0 MEMORY ORGANIZATION                                         | 2    |

| 2.1 Program Memory                                              | 2    |

| 2.2 Data Memory                                                 |      |

| 3.0 SPECIAL FUNCTION<br>REGISTERS                               | 4    |

| 4.0 PORT STRUCTURES AND<br>OPERATION                            | 10   |

| 4.1 I/O Configurations                                          |      |

| 4.2 Port 1 and Port 3                                           |      |

| 4.3 Port 0 and Port 2                                           |      |

| 4.4 Read-Modify-Write Instructions .                            |      |

| 4.5 Quasi-Bidirectional Port                                    |      |

| Operation                                                       |      |

| 4.6 Port Loading                                                |      |

| 4.7 Accessing External Memory                                   |      |

| 4.7.1 Bus Cycle Definition                                      |      |

| 4.7.2 External Bus Cycles with Wa<br>States                     |      |

| 4.7.3 Port 0 and Port 2 for States in<br>Non-Page and Page Mode |      |

| 5.0 TIMERS/COUNTERS                                             | 23   |

| 5.1 TIMER 0 AND TIMER 1                                         | 23   |

| 5.2 TIMER 2                                                     | 26   |

| 6.0 PROGRAMMABLE COUNTER<br>ARRAY                               | 30   |

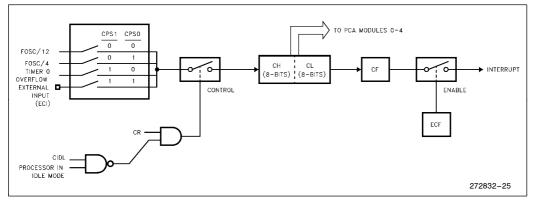

| 6.1 PCA 16-Bit Timer/Counter                                    |      |

| 6.2 Capture/Compare Modules                                     | 34   |

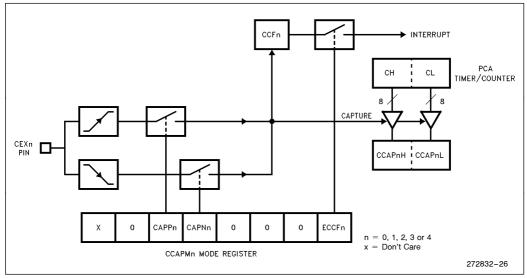

| 6.3 16-Bit Capture Mode                                         |      |

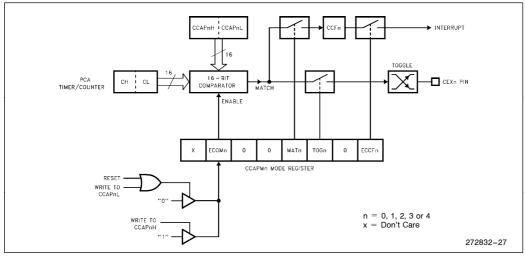

| 6.4 16-Bit Software Timer Mode                                  | 37   |

| 6.5 High Speed Output Mode                                      | 38   |

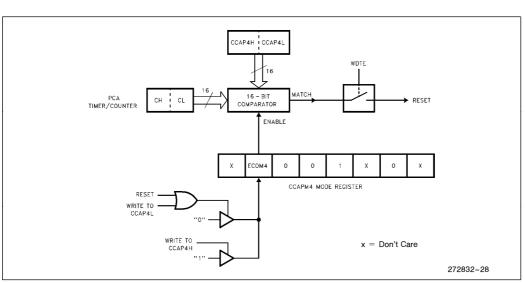

| 6.6 Watchdog Timer Mode                                         | 38   |

| 6.7 Pulse Width Modulator Mode                                  | 39   |

| С | 0 | ΝT | E١ | 1T | 5 |

|---|---|----|----|----|---|

|   |   |    |    |    |   |

| 7.0 SERIAL INTERFACE                                      | . 41 |

|-----------------------------------------------------------|------|

| 7.1 Framing Error Detection                               | . 42 |

| 7.2 Multiprocessor Communications                         | . 42 |

| 7.3 Automatic Address Recognition                         | . 42 |

| 7.4 Baud Rates                                            | . 44 |

| 7.5 Using Timer 1 to Generate Baud<br>Rates               | . 44 |

| 7.6 Using Timer 2 to Generate Baud<br>Rates               | . 45 |

| 8.0 WATCHDOG TIMER                                        | . 46 |

| 8.1 Using the WDT                                         | . 46 |

| 8.2 WDT during Idle Mode and<br>Powerdown                 | . 46 |

| 9.0 INTERRUPTS                                            | . 47 |

| 9.1 External Interrupts                                   | . 47 |

| 9.2 Timer Interrupts                                      | . 49 |

| 9.3 PCA Interrupt                                         | . 50 |

| 9.4 Serial Port Interrupt                                 | . 50 |

| 9.5 Interrupt Enable                                      | . 50 |

| 9.6 Interrupt Priorities                                  | . 51 |

| 9.7 Interrupt Processing                                  | . 54 |

| 9.7.1 Minimum Fixed Interrupt Time                        | . 55 |

| 9.7.2 Variable Interrupt<br>Parameter                     | . 55 |

| 9.7.3 Response Time Variables                             | . 55 |

| 9.7.4 Computation of Worst-Case<br>Latency With Variables | . 56 |

| 9.7.5 Blocking Conditions                                 | . 57 |

| 9.7.6 Interrupt Vector Cycle                              | . 57 |

| 9.7.7 ISRs in Process                                     | . 58 |

## CONTENTS

| <b>10.0 RESET</b>                  | В |

|------------------------------------|---|

| 10.1 Externally Initiated Resets 5 | В |

| 10.2 WDT Initiated Resets5         | Э |

| 10.3 Reset Operation5              | Э |

| 10.4 Power-on Reset 5              | Э |

| 11.0 POWER-SAVING MODES OF         |   |

| <b>OPERATION</b>                   | С |

| 11.1 Idle Mode 6                   | 0 |

## PAGE CONTENTS

| - |

|---|

|   |

| 12.0 PROGRAMMING AND VERIFYING<br>NONVOLATILE MEMORY | . 62 |

|------------------------------------------------------|------|

| 12.1 Programming and Verifying<br>Modes              | . 62 |

| 12.2 Lock Bit System                                 | . 64 |

| 12.3 Encryption Array                                | . 64 |

| 12.4 Signature Bytes                                 | . 64 |

| 13.0 ON-CIRCUIT EMULATION (ONCE)                     |      |

| MODE                                                 | . 65 |

| 14.0 ON-CHIP OSCILLATOR                              | . 66 |

| 15.0 INSTRUCTION SET<br>REFERENCE                    | . 68 |

| CONTENTS                                                                       | PAGE    |

|--------------------------------------------------------------------------------|---------|

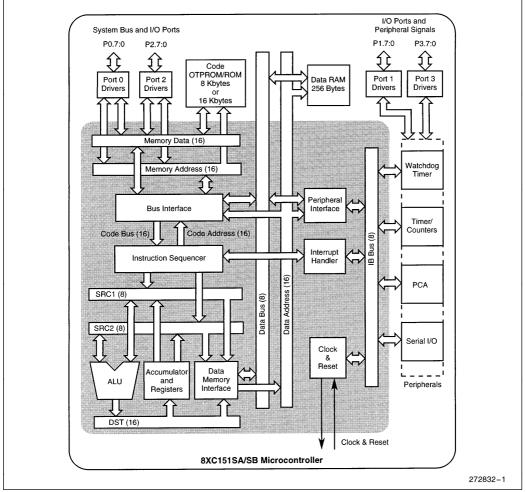

| Figure 1. 8XC151SA/SB Functional Block Diagram                                 | 3       |

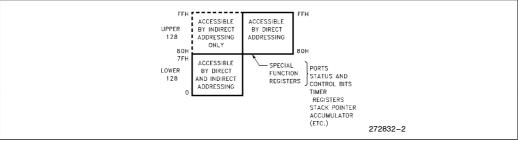

| Figure 2. Internal Data Memory                                                 | 3       |

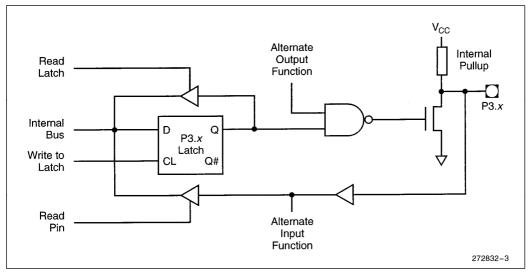

| Figure 3. Port 1 and Port 3 Structure                                          | 11      |

| Figure 4. Port 0 Structure                                                     | 11      |

| Figure 5. Port 2 Structure                                                     | 12      |

| Figure 6. Internal Pullup Configurations                                       | 14      |

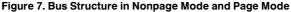

| Figure 7. Bus Structure in Nonpage Mode and Page Mode                          |         |

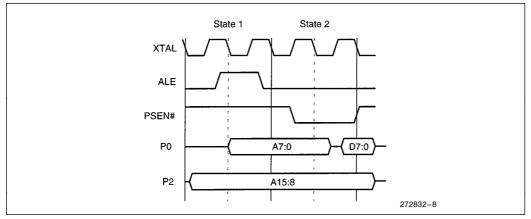

| Figure 8. External Bus Cycle: Code Fetch, Nonpage Mode                         | 17      |

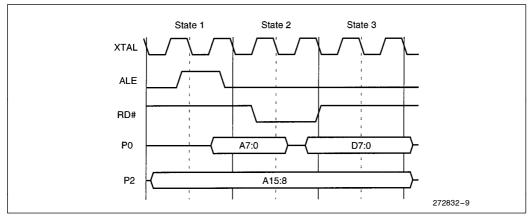

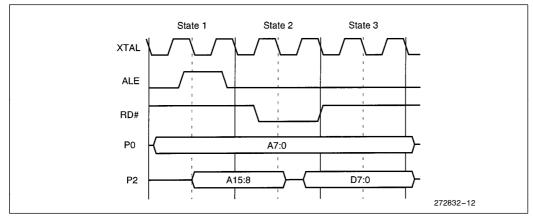

| Figure 9. External Bus Cycle: Data Read, Nonpage Mode                          |         |

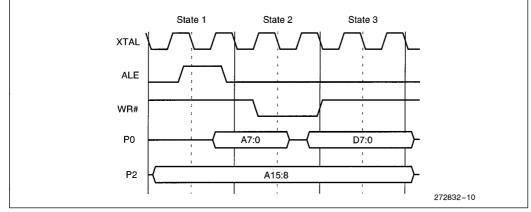

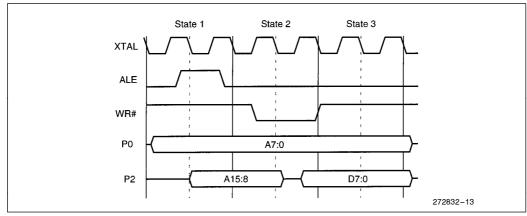

| Figure 10. External Bus Cycle: Data Write, Nonpage Mode                        |         |

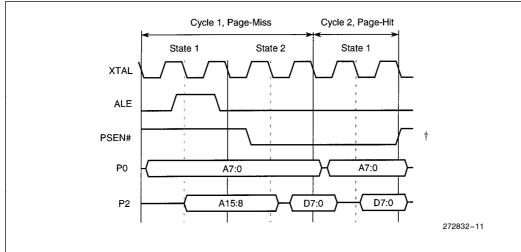

| Figure 11. External Bus Cycle: Code Fetch, Page Mode                           | 20      |

| Figure 12. External Bus Cycle: Data Read, Page Mode                            | 20      |

| Figure 13. External Bus Cycle: Data Write, Page Mode                           | 21      |

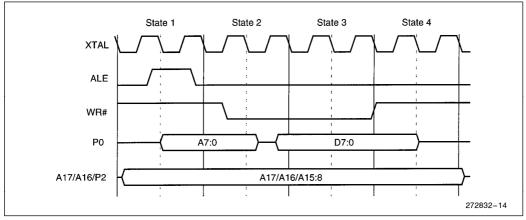

| Figure 14. External Bus Cycle: Data Write with One WR # Wait State (Nonpage Mc | ode) 21 |

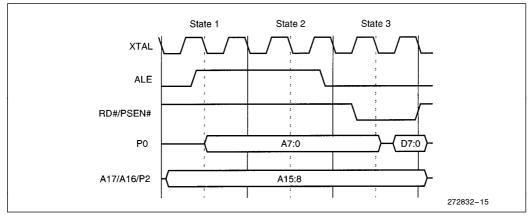

| Figure 15. External Bus Cycle: Code Fetch with One ALE Wait State (Nonpage Mo  | de) 22  |

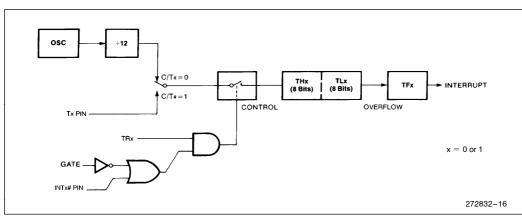

| Figure 16. Timer/Counter 0 or 1 in Mode 0: 13-Bit Counter                      | 24      |

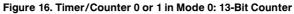

| Figure 17. Timer/Counter 0 or 1 in Mode 1: 16-Bit Counter                      |         |

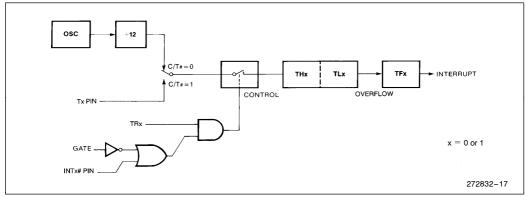

| Figure 18. Timer/Counter 1 Mode 2: 8-Bit Auto-Reload                           |         |

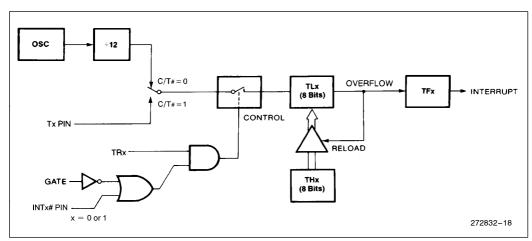

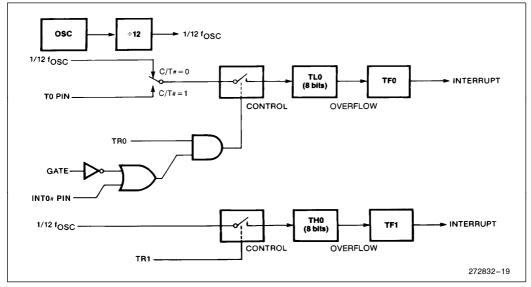

| Figure 19. Timer/Counter 0 Mode 3: Two 8-Bit Counters                          |         |

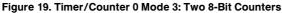

| Figure 20. Timer 2 in Capture Mode                                             |         |

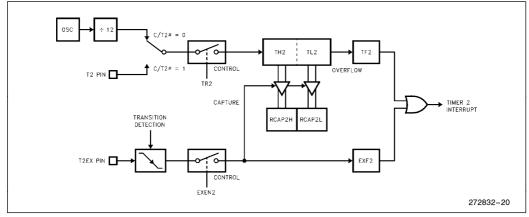

| Figure 21. Timer 2 Auto Reload Mode (DCEN = 0)                                 | 29      |

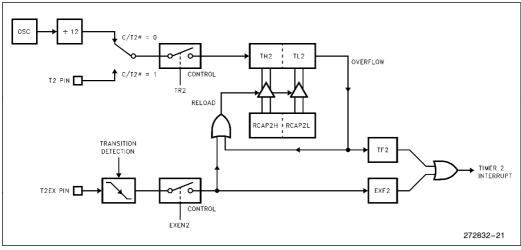

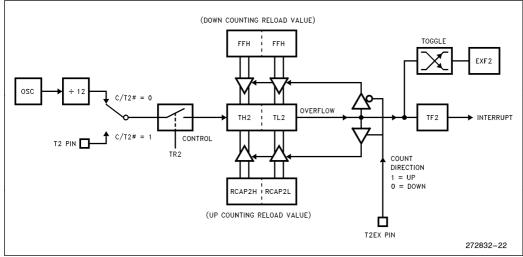

| Figure 22. Timer 2 Auto Reload Mode (DCEN = 1)                                 |         |

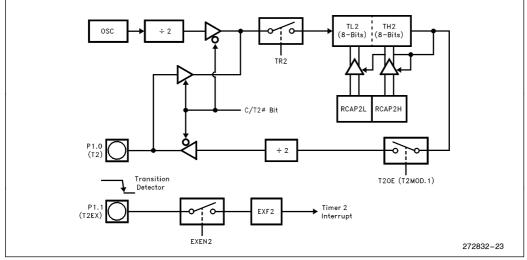

| Figure 23. Timer 2 in Clock-Out Mode                                           |         |

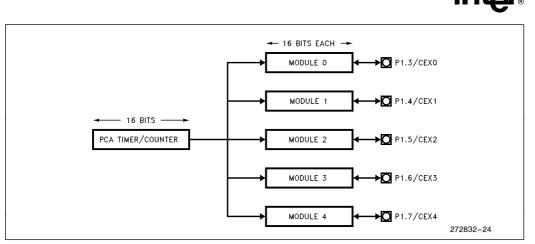

| Figure 24. Programmable Counter Array                                          | 32      |

| Figure 25. PCA Timer/Counter                                                   |         |

| Figure 26. PCA 16-Bit Capture Mode                                             |         |

| Figure 27. PCA 16-Bit Comparator Mode: Software Timer and High Speed Output    |         |

| Figure 28. Watchdog Timer Mode                                                 |         |

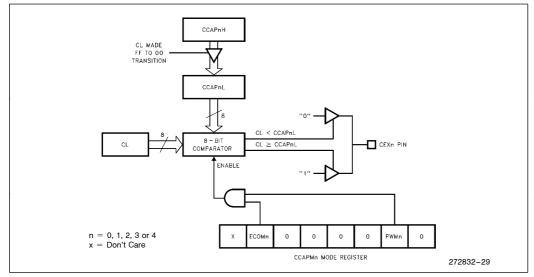

| Figure 29. PCA 8-Bit PWM Mode                                                  |         |

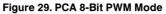

| Figure 30. CCAPnH Varies Duty Cycle                                            |         |

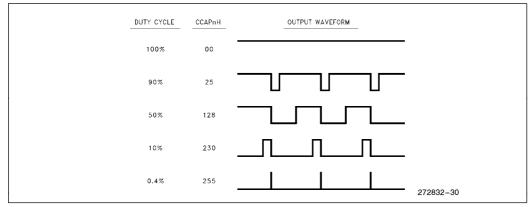

| Figure 31. Data Frame: Modes 1, 2 and 3                                        |         |

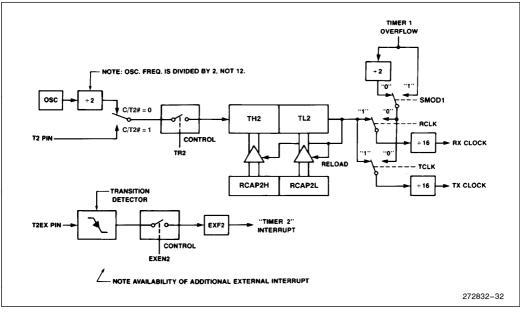

| Figure 32. Timer 2 in Baud Rate Generator Mode                                 |         |

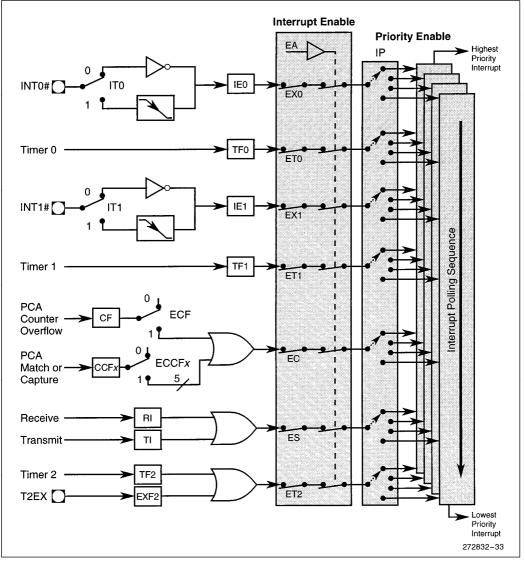

| Figure 33. Interrupt Control System                                            |         |

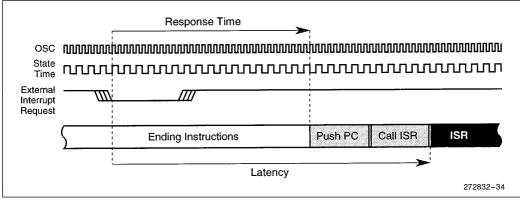

| Figure 34. The Interrupt Process                                               |         |

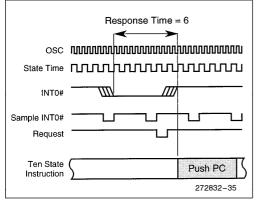

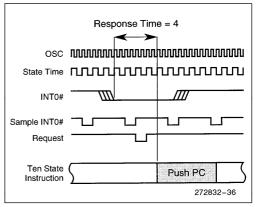

| Figure 35. Response Time Example #1                                            |         |

| Figure 36. Response Time Example #2                                            |         |

| CONTENTS                                                          | PAGE |

|-------------------------------------------------------------------|------|

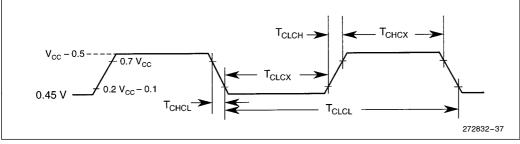

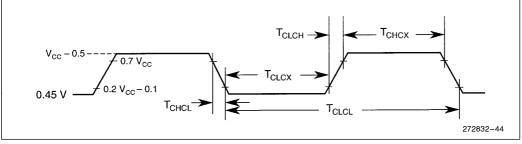

| Figure 37. External Clock Drive Waveforms                         | 58   |

| Figure 38. Power on Reset Circuitry                               | 59   |

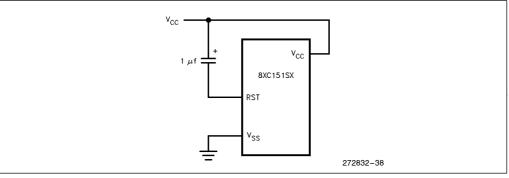

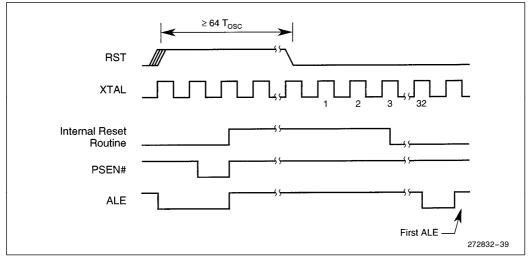

| Figure 39. Reset Timing Sequence                                  | 60   |

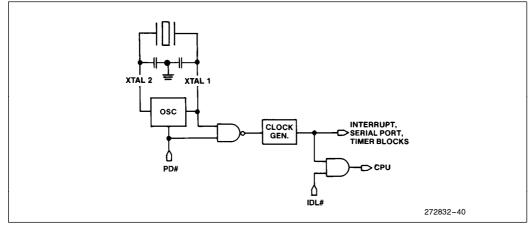

| Figure 40. Idle and Power Down Hardware                           | 61   |

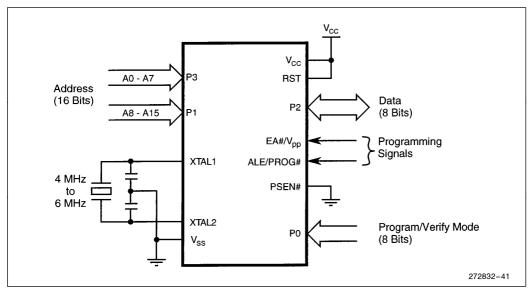

| Figure 41. Setup for Programming and Verifying Nonvolatile Memory | 62   |

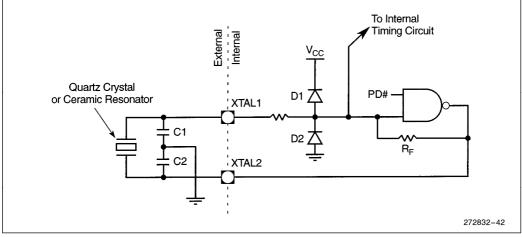

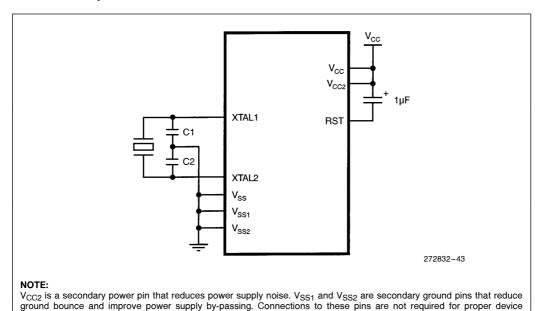

| Figure 42. CHMOS On-chip Oscillator                               | 66   |

| Figure 43. External Clock Connection                              | 67   |

| Figure 44. External Clock Drive Waveforms                         | 68   |

| CONTENTS PAGE                                                                     |

|-----------------------------------------------------------------------------------|

| Table 1. 8XC151 Family of Microcontrollers         2                              |

| Table 2. 8XC151SA/SB Map and Reset Values         4                               |

| Table 3. Core SFRs    5                                                           |

| Table 4. I/O Port SFRs 5                                                          |

| Table 5. Serial I/O SFRs    5                                                     |

| Table 6. Timer/Counter and Watchdog Timer SFRs         6                          |

| Table 7. Programmable Counter Array (PCA) SFRs         6                          |

| Table 8. User Configuration Byte UCONFIG0         16                              |

| Table 9. User Configuration Byte UCONFIG1         16                              |

| Table 10. Bus Cycle Definitions (No Wait States)    17                            |

| Table 11. Timer 2 Operating Modes    27                                           |

| Table 12. Timer 1 Generated Commonly Used Baud Rates    44                        |

| Table 13. Timer 2 Generated Commonly Used Baud Rates    46                        |

| Table 14. Interrupt Control Matrix    49                                          |

| Table 15. Level of Priority    52                                                 |

| Table 16. Interrupt Priority Within Level    52                                   |

| Table 17. Interrupt Latency Variables    57                                       |

| Table 18. Programming and Verifying Modes    63                                   |

| Table 19. Lock Bit Function    64                                                 |

| Table 20. Contents of the Signature Bytes    65                                   |

| Table 21. Summary of Add and Subtract Instructions         68                     |

| Table 22. Summary of Increment and Decrement Instructions         69              |

| Table 23. Summary of Multiply, Divide, and Decimal-adjust Instructions         69 |

| Table 24. Summary of Logical Instructions    70                                   |

| Table 25. Summary of Move Instructions    71                                      |

| Table 26. Summary of Exchange, Push, and Pop Instructions                         |

| Table 27. Summary of Bit Instructions    72                                       |

| Table 28. Summary of Control Instructions    73                                   |

## **1.0 INTRODUCTION**

The 8XC151SA/SB is a highly integrated CMOS 8-bit microcontroller which is instruction set compatible with the MCS<sup>®</sup>51 microcontroller. It comes in 40-lead PDIP and 44-lead PLCC maintaining pin compatibility with MCS 51 microcontrollers. The 8XC151SA/SB has 256 bytes of on-chip RAM and is available with 8/16 Kbytes of on-chip ROM/OTPROM or ROMless. Several new features like programmable wait states, page mode and Extended ALE can be selected by using the new user programmable configuration. Key features like instruction and code fetch in page mode are available.

Functional characteristics of 8XC151SA/SB are listed below.

- Pipeline Instruction Execution Unit

- MCS 51 Microcontroller 44-pin PLCC and 40-pin PDIP Compatibility

- MCS 51 Microcontroller Compatible Instruction Set

- Static Standby to at least 16 MHz Operation

- 64K External Code Memory Space

- 64K External Data Memory Space

- 256 Bytes On-chip Data RAM

- 8/16K On-chip Code Memory (OTPROM/ROM) or ROMless Options

- 3 16-Bit Flexible Timer/Counters

- 32 Programmable I/O Lines

- 7 Maskable Interrupt Sources with 4 Programmable Priority Levels

- Programmable Counter Array with:

- High Speed Output

- Compare/Capture

- Pulse Width Modulator

- Watchdog Timer Capabilities

- Programmable Serial I/O Port

- Framing Error Detection

- Automatic Address Recognition

- Hardware Watchdog Timer

- External WAIT Pin

- 16-Bit Internal Code Bus

- Page Mode and Wait States Configuration Options

- Minimum 2-Clock External Code Fetch in Page Mode

- User-Selectable Configurations:

- External Wait States (0–3 Wait States)

- Page Mode

- Power-Saving Features

- Idle Mode

- Power Down Mode

Table 1 summarizes the product names and memory differences of the various 8XC151SA/SB products currently available. Throughout this document, the products will generally be referred to as the C151SX.

| ROM<br>Version | OTPROM<br>Version |          | OTPROM<br>ROM Size |     |

|----------------|-------------------|----------|--------------------|-----|

| 83C151SA       | 87C151SA          | 80C151SB | 8K                 | 256 |

| 83C151SB       | 87C151SB          | 80C151SB | 16K                | 256 |

#### Table 1. 8XC151 Family of Microcontrollers

## 2.0 MEMORY ORGANIZATION

The 8XC151SA/SB devices have a separate address space for Program and Data Memory. Up to 64 Kbytes each of external Program and Data Memory can be addressed.

### 2.1 Program Memory

If the EA # pin is connected to  $V_{SS}$ , all program fetches are directed to external memory. On the 83C151SA (or 87C151SA), if the EA # pin is connected to  $V_{CC}$ , then program fetches to addresses 0000H through 1FFFH are directed to internal ROM and fetches to addresses 2000H through FFFFH are to external memory.

On the 83C151SB (or 87C151SB) if EA# is connected to  $V_{CC}$ , program fetches to addresses 0000H through 3FFFH are directed to internal ROM, and fetches to addresses 4000H through FFFFH are to external memory.

## 2.2 Data Memory

The C151SX has internal data memory that is mapped into three separate segments: the lower 128 bytes of RAM, upper 128 bytes of RAM and 128 bytes special function register (SFR). Refer to Figure 2.

The three segments are:

- 1. The Lower 128 bytes of RAM (addresses 00H to 7FH) are directly and indirectly addressable.

- 2. The Upper 128 bytes of RAM (addresses 80H to FFH) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80H to FFH) are directly addressable only.

The Lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction. Instructions that use direct addressing access SFR space. For example:

#### MOV 0A0H, # data

accesses the SFR at location 0A0H (which is P2). Instructions that use indirect addressing access the Upper 128 bytes of data RAM. For example:

#### MOV @R0, #data

where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

Figure 2. Internal Data Memory

## 3.0 SPECIAL FUNCTION REGISTERS

The special function registers (SFRs) reside in their associated on-chip peripherals or in the core. Table 2 shows the SFR address space with the SFR mnemonics and reset values. Unoccupied locations in the SFR space (the shaded locations in Table 2) are unimplemented, i.e., no register exists. If an instruction attempts to write to an unimplemented SFR location, the instruction executes, but nothing is actually written. If an unimplemented SFR location is read, it returns an unspecified value.

|    | 0/8               | 1/9               | 2/A                | 3/B                | 4/C                | 5/D                | 6/E                | 7/F              |    |

|----|-------------------|-------------------|--------------------|--------------------|--------------------|--------------------|--------------------|------------------|----|

| F8 |                   | CH<br>00000000    | CCAP0H<br>xxxxxxxx | CCAP1H<br>xxxxxxxx | CCAP2H<br>xxxxxxxx | ССАРЗН<br>хххххххх | CCAP4H<br>xxxxxxxx |                  | FF |

| F0 | B<br>00000000     |                   |                    |                    |                    |                    |                    |                  | F7 |

| E8 |                   | CL<br>00000000    | CCAP0L<br>xxxxxxxx | CCAP1L<br>xxxxxxxx | CCAP2L<br>xxxxxxxx | CCAP3L<br>xxxxxxxx | CCAP4L<br>xxxxxxxx |                  | EF |

| E0 | ACC<br>00000000   |                   |                    |                    |                    |                    |                    |                  | E7 |

| D8 | CCON<br>00x00000  | CMOD<br>00xxx000  | CCAPM0<br>x0000000 | CCAPM1<br>x0000000 | CCAPM2<br>x0000000 | CCAPM3<br>x0000000 | CCAPM4<br>x0000000 |                  | DF |

| D0 | PSW<br>00000000   | PSW 1<br>00000000 |                    |                    |                    |                    |                    |                  | D7 |

| C8 | T2CON<br>00000000 | T2MOD<br>xxxxxx00 | RCAP2L<br>00000000 | RCAP2H<br>00000000 | TL2<br>00000000    | TH2<br>00000000    |                    |                  | CF |

| C0 |                   |                   |                    |                    |                    |                    |                    |                  | C7 |

| B8 | IPL0<br>x0000000  | SADEN<br>00000000 |                    |                    |                    |                    |                    |                  | BF |

| В0 | P3<br>11111111    |                   |                    |                    |                    |                    |                    | IPH0<br>x0000000 | B7 |

| A8 | IE0<br>00000000   | SADDR<br>00000000 |                    |                    |                    |                    |                    |                  | AF |

| A0 | P2<br>11111111    |                   |                    |                    |                    |                    | WDTRST<br>xxxxxxxx |                  | A7 |

| 98 | SCON<br>00000000  | SBUF<br>xxxxxxxx  |                    |                    |                    |                    |                    |                  | 9F |

| 90 | P1<br>11111111    |                   |                    |                    |                    |                    |                    |                  | 97 |

| 88 | TCON<br>00000000  | TMOD<br>00000000  | TL0<br>00000000    | TL1<br>00000000    | TH0<br>00000000    | TH1<br>00000000    |                    |                  | 8F |

| 80 | P0<br>11111111    | SP<br>00000111    | DPL<br>00000000    | DPH<br>00000000    |                    |                    |                    | PCON<br>00xx0000 | 87 |

|    | 0/8               | 1/9               | 2/A                | 3/B                | 4/C                | 5/D                | 6/E                | 7/F              |    |

#### Table 2. 8XC151SA/SB Map and Reset Values

The following tables list the mnemonics, names, and addresses of the SFRs:

Table 3—Core SFRs

Table 4—I/O Port SFRs

Table 5-Serial I/O SFRs

Table 6-Timer/Counter and Watchdog Timer SFRs

Table 7-Programmable Counter Array (PCA) SFRs

#### Table 3. Core SFRs

| Mnemonic | Name                              | Address |

|----------|-----------------------------------|---------|

| ACC      | Accumulator                       | E0H     |

| В        | B Register                        | F0H     |

| PSW      | Program Status Word               | D0H     |

| PSW1     | Program Status Word 1             | D1H     |

| SP       | Stack Pointer                     | 81H     |

| DPTR     | Data Pointer (2 bytes)            | _       |

| DPL      | Low Byte of DPTR                  | 82H     |

| DPH      | High Byte of DPTR                 | 83H     |

| PCON     | Power Control                     | 87H     |

| IE0      | Interrupt Enable Control 0        | A8H     |

| IPH0     | Interrupt Priority Control High 0 | B7H     |

| IPL0     | Interrupt Priority Control Low 0  | B8H     |

#### Table 4. I/O Port SFRs

| Mnemonic | Name   | Address |

|----------|--------|---------|

| P0       | Port 0 | 80H     |

| P1       | Port 1 | 90H     |

| P2       | Port 2 | A0H     |

| P3       | Port 3 | вон     |

#### Table 5. Serial I/O SFRs

| Mnemonic | Name                | Address |

|----------|---------------------|---------|

| SCON     | Serial Control      | 98H     |

| SBUF     | Serial Data Buffer  | 99H     |

| SADEN    | Serial Address Mask | B9H     |

| SADDR    | Serial Address      | A9H     |

### 8XC151SA/SB HARDWARE DESCRIPTION

| Table 6. Timer/Counter and Watchdog Timer SFRS |                                    |         |  |  |  |  |  |  |

|------------------------------------------------|------------------------------------|---------|--|--|--|--|--|--|

| Mnemonic                                       | Name                               | Address |  |  |  |  |  |  |

| TL0                                            | Timer/Counter 0 Low Byte           | 8AH     |  |  |  |  |  |  |

| TH0                                            | Timer/Counter 0 High Byte          | 8CH     |  |  |  |  |  |  |

| TL1                                            | Timer/Counter 1 Low Byte           | 8BH     |  |  |  |  |  |  |

| TH1                                            | Timer/Counter 1 High Byte          | 8DH     |  |  |  |  |  |  |

| TL2                                            | Timer/Counter 2 Low Byte           | ССН     |  |  |  |  |  |  |

| TH2                                            | Timer/Counter 2 High Byte          | CDH     |  |  |  |  |  |  |

| TCON                                           | Timer/Counter 0 and 1 Control      | 88H     |  |  |  |  |  |  |

| TMOD                                           | Timer/Counter 0 and 1 Mode Control | 89H     |  |  |  |  |  |  |

| T2CON                                          | Timer/Counter 2 Control            | C8H     |  |  |  |  |  |  |

| T2MOD                                          | Timer/Counter 2 Mode Control       | С9Н     |  |  |  |  |  |  |

| RCAP2L                                         | Timer 2 Reload/Capture Low Byte    | САН     |  |  |  |  |  |  |

| RCAP2H                                         | Timer 2 Reload/Capture High Byte   | СВН     |  |  |  |  |  |  |

| WDTRST                                         | Watchdog Timer Reset               | A6H     |  |  |  |  |  |  |

### Table 6. Timer/Counter and Watchdog Timer SFRs

intel

## Table 7. Programmable Counter Array (PCA) SFRs

| Mnemonic | Name                                   | Address |

|----------|----------------------------------------|---------|

| CCON     | PCA Timer/Counter Control              | D8H     |

| CMOD     | PCA Timer/Counter Mode                 | D9H     |

| CCAPM0   | PCA Timer/Counter Mode 0               | DAH     |

| CCAPM1   | PCA Timer/Counter Mode 1               | DBH     |

| CCAPM2   | PCA Timer/Counter Mode 2               | DCH     |

| CCAPM3   | PCA Timer/Counter Mode 3               | DDH     |

| CCAPM4   | PCA Timer/Counter Mode 4               | DEH     |

| CL       | PCA Timer/Counter Low Byte             | E9H     |

| СН       | PCA Timer/Counter High Byte            | F9H     |

| CCAP0L   | PCA Compare/Capture Module 0 Low Byte  | EAH     |

| CCAP1L   | PCA Compare/Capture Module 1 Low Byte  | EBH     |

| CCAP2L   | PCA Compare/Capture Module 2 Low Byte  | ECH     |

| CCAP3L   | PCA Compare/Capture Module 3 Low Byte  | EDH     |

| CCAP4L   | PCA Compare/Capture Module 4 Low Byte  | EEH     |

| CCAP0H   | PCA Compare/Capture Module 0 High Byte | FAH     |

| CCAP1H   | PCA Compare/Capture Module 1 High Byte | FBH     |

| CCAP2H   | PCA Compare/Capture Module 2 High Byte | FCH     |

| ССАРЗН   | PCA Compare/Capture Module 3 High Byte | FDH     |

| CCAP4H   | PCA Compare/Capture Module 4 High Byte | FEH     |

8XC151SA/SB HARDWARE DESCRIPTION

Accumulator: ACC is the Accumulator register. The mnemonics for Accumulator-Specific instructions, however, refer to the Accumulator simply as A.

**B Register:** The B register is used during multiply and divide operations. For other instructions it can be treated as another scratch pad register.

Stack Pointer (SP): The Stack Pointer Register is 8 bits wide. It is incremented before data is stored during PUSH and CALL executions. The stack may reside anywhere in on-chip RAM. On reset, the Stack Pointer is initialized to 07H causing the stack to begin at location 08H.

**Data Pointer:** The Data Pointer (DPTR) consists of a high byte (DPH) and a low byte (DPL). Its intended function is to hold a 16-bit address, but it may be manipulated as a 16-bit register or as two independent 8-bit registers.

**Program Status Word:** The PSW and PSW1 registers contain program status information as detailed in PSW: Program Status Word Register on the following page.

**Ports 0 to 3 Registers:** P0, P1, P2, and P3 are the SFR latches of Port 0, Port 1, Port 2, and Port 3, respectively.

Timer Registers: Register pairs (TH0, TL0), (TH1, TL1), and (TH2, TL2) are the 16-bit count registers for Timer/Counters 0, 1, and 2 respectively. Control and status bits are contained in registers TCON and TMOD for Timers 0 and 1 and in registers T2CON and T2MOD for Timer 2. The register pair (RCAP2H, RCAP2L) are the capture/reload registers for Timer 2 in 16-bit capture mode or 16-bit auto-reload mode.

**Programmable Counter Array (PCA) Registers:** The 16-bit PCA timer/counter consists of registers CH and CL. Registers CCON and CMOD contain the control and status bits for the PCA. The CCAPMn (n = 0, 1, 2, 3, or 4) registers control the mode for each of the five PCA modules. The register pairs (CCAPnH, CCAPnL) are the 16-bit compare/capture registers for each PCA module.

Serial Port Registers: The Serial Data Buffer, SBUF, is actually two separate registers: a transmit buffer and a receive buffer register. When data is moved to SBUF, it goes to the transmit buffer where it is held for serial transmission. (Moving a byte to SBUF initiates the transmission). When data is moved from SBUF, it comes from the receive buffer. Register SCON contains the control and status bits for the Serial Port. Registers SADDR and SADEN are used to define the Given and the Broadcast addresses for the Automatic Address Recognition feature.

**Interrupt Registers:** The individual interrupt enable bits are in the IEO register. Priorities of interrupt can be set in the IPHO and IPLO registers.

**Power Control Register:** PCON controls the Power Reduction Modes. Idle and Power Down Modes.

**Watchdog Timer Reset:** WDTRST register is used to keep the watchdog timer from periodically resetting the part.

### PSW: Program Status Word Register

| PSW             |                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                        |                        |                                                                              |                                 | Re                             | Address:<br>set State:            | D0H<br>0000 0000B     |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------|---------------------------------|--------------------------------|-----------------------------------|-----------------------|--|

|                 |                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                        |                        | s bits that reflec<br>eneral-purpose f                                       |                                 |                                |                                   | ect the register      |  |

| CY              | AC                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                        | F0                     | RS1                                                                          | RS0                             | OV                             | UD                                | Р                     |  |

| Bit<br>Mnemonic |                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                        |                        |                                                                              | Function                        |                                |                                   |                       |  |

| CY              | Carry F                                                                                                                                                                                                                                                                                                               | Flag:                                                                                                                                                                                                                                                                                                                                  |                        |                                                                              |                                 |                                |                                   |                       |  |

|                 | MSB. I<br>carry f                                                                                                                                                                                                                                                                                                     | lt is se<br>lag is a                                                                                                                                                                                                                                                                                                                   | t by a su<br>also affe | by an addition in<br>btraction (SUB,<br>cted by some ro<br>, and the multipl | SUBB) if a bo<br>tate and shift | orrow is need<br>instructions, | led for the M<br>, logical bit ir | ISB. The nstructions, |  |

| AC              | Auxilla                                                                                                                                                                                                                                                                                                               | ry Car                                                                                                                                                                                                                                                                                                                                 | ry Flag:               |                                                                              |                                 |                                |                                   |                       |  |

|                 | The auxillary carry flag is affected only by instructions that address 8-bit operands. The AC flag is set if an arithmetic instruction with an 8-bit operand produces a carry out of b 13 (from addition) or a borrow into bit 3 (from subtraction). Otherwise it is cleared. This flag is useful for BCD arithmetic. |                                                                                                                                                                                                                                                                                                                                        |                        |                                                                              |                                 |                                |                                   |                       |  |

| F0              | Flag 0:                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                        |                        |                                                                              |                                 |                                |                                   |                       |  |

|                 | This ge                                                                                                                                                                                                                                                                                                               | eneral                                                                                                                                                                                                                                                                                                                                 | -purpose               | e flag is available                                                          | e to the user.                  |                                |                                   |                       |  |

| RS1:0           | Register Bank Select Bits 1 and 0:                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                        |                        |                                                                              |                                 |                                |                                   |                       |  |

|                 | These bits select the memory locations that comprise the active bank of the register file (registers $R0-R7$ ).                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                        |                        |                                                                              |                                 |                                |                                   |                       |  |

|                 | RS1                                                                                                                                                                                                                                                                                                                   | RS0                                                                                                                                                                                                                                                                                                                                    | Bank                   | Address                                                                      |                                 |                                |                                   |                       |  |

|                 | 0                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                      | 0                      | 00H-07H                                                                      |                                 |                                |                                   |                       |  |

|                 | 0                                                                                                                                                                                                                                                                                                                     | 1<br>0                                                                                                                                                                                                                                                                                                                                 | 1<br>2                 | 08H–0FH<br>10H–17H                                                           |                                 |                                |                                   |                       |  |

|                 | 1                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                      | 3                      | 18H-1FH                                                                      |                                 |                                |                                   |                       |  |

| OV              | Overflo                                                                                                                                                                                                                                                                                                               | ow Fla                                                                                                                                                                                                                                                                                                                                 | ıg:                    |                                                                              |                                 |                                |                                   |                       |  |

|                 | (i.e., if<br>comple                                                                                                                                                                                                                                                                                                   | This bit is set if an addition or subtraction of signed variables results in an overflow error (i.e., if the magnitude of the sum or difference is too great for the seven LSBs in 2's-complement representation). The overflow flag is also set if a multiplication product overflows one byte or if a division by zero is attempted. |                        |                                                                              |                                 |                                |                                   |                       |  |

| UD              | User-d                                                                                                                                                                                                                                                                                                                | lefined                                                                                                                                                                                                                                                                                                                                | I Flag:                |                                                                              |                                 |                                |                                   |                       |  |

|                 | This ge                                                                                                                                                                                                                                                                                                               | eneral                                                                                                                                                                                                                                                                                                                                 | -purpose               | e flag is available                                                          | e to the user.                  |                                |                                   |                       |  |

| Р               | Parity                                                                                                                                                                                                                                                                                                                | Bit:                                                                                                                                                                                                                                                                                                                                   |                        |                                                                              |                                 |                                |                                   |                       |  |

|                 | This bit indicates the parity if the accumulator. It is set if an odd number of bits in the accumulator are set. Otherwise, it is cleared. Not all instructions update the parity bit. The parity bit is set or cleared by instructions that change the contents of the accumulator (ACC, Register R11).              |                                                                                                                                                                                                                                                                                                                                        |                        |                                                                              |                                 |                                |                                   |                       |  |

## 8XC151SA/SB HARDWARE DESCRIPTION

| SW1 Address: 0D1 |                          |                                                                                                              |                |                 |                  |              |                  |  |  |  |  |

|------------------|--------------------------|--------------------------------------------------------------------------------------------------------------|----------------|-----------------|------------------|--------------|------------------|--|--|--|--|

| _                |                          | Reset State: 0000 0000B                                                                                      |                |                 |                  |              |                  |  |  |  |  |

| 7                |                          | 0                                                                                                            |                |                 |                  |              |                  |  |  |  |  |

| CY               | AC                       | F0                                                                                                           | RS1            | RS0             | OV               | Z            |                  |  |  |  |  |

| Bit<br>Mnemonic  |                          | Function                                                                                                     |                |                 |                  |              |                  |  |  |  |  |

| CY               | Carry Flag:              |                                                                                                              |                |                 |                  |              |                  |  |  |  |  |

|                  | Identical to             | the CY bit in                                                                                                | the PSW reg    | ister.          |                  |              |                  |  |  |  |  |

| AC               | Auxillary C              | arry Flag:                                                                                                   |                |                 |                  |              |                  |  |  |  |  |

|                  | Identical to             | the AC bit in                                                                                                | the PSW reg    | ister.          |                  |              |                  |  |  |  |  |

| Ν                | Negative F               | lag:                                                                                                         |                |                 |                  |              |                  |  |  |  |  |

|                  |                          | et if the resul<br>herwise it is c                                                                           |                | ogical or arith | metic operati    | on was neg   | ative, i.e., bit |  |  |  |  |

| RS1:0            | Register B               | ank Select Bi                                                                                                | ts 0 and 1:    |                 |                  |              |                  |  |  |  |  |

|                  | Identical to             | the RS1:0 bi                                                                                                 | ts in the PSW  | / register.     |                  |              |                  |  |  |  |  |

| OV               | Overflow F               | lag:                                                                                                         |                |                 |                  |              |                  |  |  |  |  |

|                  | Identical to             | the OV bit in                                                                                                | the PSW reg    | ister.          |                  |              |                  |  |  |  |  |

| Z                | Zero Flag:               |                                                                                                              |                |                 |                  |              |                  |  |  |  |  |

|                  | This flag is is cleared. | This flag is set if the result of the last logical or arithmetic operation is zero. Otherwise it is cleared. |                |                 |                  |              |                  |  |  |  |  |

| _                | Reserved:                |                                                                                                              |                |                 |                  |              |                  |  |  |  |  |

|                  | The value i              | read from this                                                                                               | bit is indeter | minate. Do n    | ot write a ''1'' | to this bit. |                  |  |  |  |  |

### 4.0 PORT STRUCTURES AND OPERATION

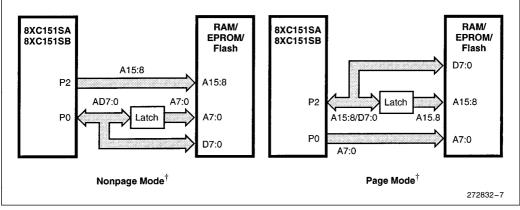

The C151SX uses input/output (I/O) ports to exchange data with external devices. In addition to performing general-purpose I/O, some ports are capable of external memory operations; others allow for alternate functions. All four C151SX I/O ports are bidirectional. Each port contains a latch, an output driver, and an input buffer. Port 0 and port 2 output drivers and input buffers facilitate external memory operations. Port 0 drives the lower address byte onto the parallel address bus, and port 2 drives the upper address byte onto the bus. In nonpage mode, the data is multiplexed with the lower address byte on port 0. In page mode, the data is multiplexed with the upper address byte on port 2. All port 1 and port 3 pins serve for both general-purpose I/O and alternative functions.

## 4.1 I/O Configurations

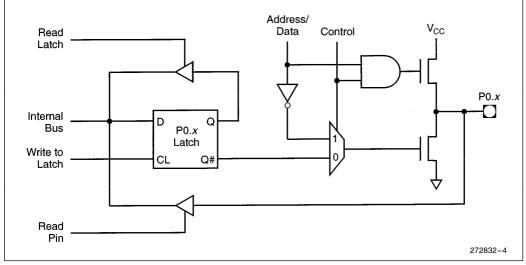

Each port SFR operates via type-D latches, as illustrated in Figure 3 for ports 1 and 3. A CPU "write to latch" signal initiates transfer of internal bus data into the type-D latch. A CPU "read latch" signal transfers the latched Q output onto the internal bus. Similarly, a "read pin" signal transfers the logical level of the port pin. Some port data instructions activate the "read latch" signal while others activate the "read pin" signal. Latch instructions are referred to as read-modifywrite instructions. Each I/O line may be independently programmed as input or output.

## 4.2 Port 1 and Port 3

Figure 3 shows the structure of ports 1 and 3, which have internal pullups. An external source can pull the pin low. Each port pin can be configured either for general-purpose I/O or for its alternate input or output function.

To use a pin for general-purpose output, set or clear the corresponding bit in the Px register (x = 1, 3). To use a pin for general-purpose input, set the bit in the Px register. This turns off the output driver FET.

To configure a pin for its alternate function, set the bit in the Px register. When the latch is set, the "alternate output function" signal controls the output level (Figure 3). The operation of ports 1 and 3 is discussed further in the "Quasi-bidirectional Port Operation" section.

## 4.3 Port 0 and Port 2

Ports 0 and 2 are used for general-purpose I/O or as the external address/data bus. Port 0, shown in Figure 4, differs from the other ports in not having internal pullups. Figure 5 shows the structure of port 2. An external source can pull a port 2 pin low.

To use a pin for general-purpose output, set or clear the corresponding bit in the Px register (x = 0, 2). To use a pin for general-purpose input set the bit in the Px register to turn off the output driver FET.

Figure 4. Port 0 Structure

#### V<sub>cc</sub> Address/Data Control Internal Read Pullup Latch P2.x Internal n Q D Bus P2.x Latch Write to CL Q# Latch Read Pin 272832-5

#### Figure 5. Port 2 Structure

When port 0 and port 2 are used for an external memory cycle, an internal control signal switches the outputdriver input from the latch output to the internal address/data line. Port 0 and port 2 are precluded from use as general purpose I/O ports when used as address/ data bus drivers. Port 0 internal pullups assist the logic-one output for memory bus cycles only. Except for these bus cycles, the pullup FET is off. All other port 0 outputs are open drain.

### 4.4 Read-Modify-Write Instructions

Some instructions read the latch data rather than the pin data. The latch based instructions read the data, modify the data, and then rewrite the latch. These are called "read-modify-write" instructions. Below is a complete list of these special instructions. When the destination operand is a port, or a port bit, these instructions read the latch rather than the pin:

| ANL         | (logical AND, e.g., ANL Pl, A)                               |

|-------------|--------------------------------------------------------------|

| ORL         | (logical OR, e.g., ORL P2, A)                                |

| XRL         | (logical EX-OR, e.g.,<br>XRL P3, A)                          |

| JBC         | (jump if bit = 1 and<br>clear bit, e.g.,<br>JBC Pl.1, LABEL) |

| CPL         | (complement bit, e.g.,<br>CPL P3.0)                          |

| INC         | (increment, e.g., INC<br>P2)                                 |

| DEC         | (decrement, e.g., DEC<br>P2)                                 |

| DJNZ        | (decrement and jump if<br>not zero, e.g.,<br>DJNZ P3, LABEL) |

| MOV PX.Y, C | (move carry bit to bit<br>Y of port X)                       |

| CLR PX.Y    | (clear bit Y of port X)                                      |

| SETB PX.Y   | (set bit Y of port X)                                        |

It is not obvious the last three instructions in this list are read-modify-write instructions. These instructions read the port (all 8 bits), modify the specifically addressed bit, and write the new byte back to the latch. These read-modify-write instructions are directed to the latch rather than the pin in order to avoid possible misinterpretation of voltage (and therefore, logic) levels at the pin. For example, a port bit used to drive the base of an external bipolar transistor cannot rise above the transistor's base-emitter junction voltage (a value lower than  $V_{IL}$ ). With a logic one written to the bit, attempts by the CPU to read the port at the pin are misinterpreted as logic zero. A read of the latch rather than the pin returns the correct logic-one value.

### 4.5 Quasi-Bidirectional Port Operation

Port 1, port 2, and port 3 have fixed internal pullups and are referred to as "quasi-bidirectional" ports. When configured as an input, the pin impedance appears as logic one and sources current in response to an external logic-zero condition. Port 0 is a "true bidirectional" pin. The pin floats when configured as input. Resets write logical one to all port latches. If logical zero is subsequently written to a port latch, it can be returned to input conditions by a logical one written to the latch. For additional electrical information, refer to the current 8XC151SA/SB datasheet.

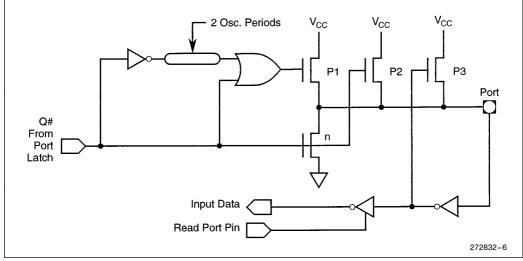

Figure 6. Internal Pullup Configurations

Logical zero-to-one transitions in port 1, port 2, and port 3 utilize an additional pullup to aid this logic transition (see Figure 6). This increases switch speed. The extra pullup briefly sources 100 times normal internal circuit current. The internal pullups are field-effect transistors rather than linear resistors. Pullups consist of three p-channel FET (pFET) devices. A pFET is on when the gate senses logical zero and off when the gate senses logical one. pFET #1 is turned on for two oscillator periods immediately after a zero-to-one transition in the port latch. A logic one at the port pin turns on pFET #3 (a weak pullup) through the inverter. This inverter and pFET pair form a latch to drive logic one. pFET #2 is a very weak pullup switched on whenever the associated nFET is switched off. This is traditional CMOS switch convention. Current strengths are  $\frac{1}{10}$ that of pFET #3.

### 4.6 Port Loading

Output buffers of port 1, port 2, and port 3 can each sink 1.6 mA at logic zero (see  $V_{OL}$  specifications in the 8XC151SA/SB datasheet). These port pins can be driven by open-collector and open-drain devices. Logic zero-to-one transitions occur slowly as limited current pulls the pin to a logic-one condition (Figure 6). A logic-zero input turns off pFET #3. This leaves only pFET #2 weakly in support of the transition. In external bus mode, port 0 output buffers each sink 3.2 mA at logic zero (see  $V_{OL1}$  in the 8XC151SA/SB datasheet). However, the port 0 pins require external pullups to drive external gate inputs. See the latest revision of the 8XC151SA/SB datasheet for complete electrical design information. External circuits must be designed to limit current requirements to these conditions.

## 4.7 Accessing External Memory

The external memory interface comprises the external bus (ports 0 and 2) and the bus control signals. Chip configuration bytes determine several interface options: page mode or nonpage mode for external code fetches; the address ranges for RD#, WR#, and PSEN#; and the number of external wait states. You can use these options to tailor the interface to your application. The external memory interface operates in either page mode and nonpage mode. Page mode provides increased performance by reducing the time for external code fetches. Page mode does not apply to code fetches from on-chip memory. The reset routine configures the C151SX for operation in page mode or nonpage mode according to bit 1 of configuration bytes UCONFIG0 (refer to Table 8). Figure 7 shows the structure of the external address bus for page and nonpage mode operation. P0 carries address A7:0 while P2 carries address A15:8. Data D7:0 is multiplexed with A7:0 on P0 in nonpage mode and with A15:8 on P2 in page mode.

†The descriptions of A15:8/P2.7:0 and AD7:0/P0.7:0 are for the nonpage-mode chip configuration (compatible with 44-pin PLCC MCS® 51 microcontrollers). If the chip is configured for page-mode operation, port 0 carries the lower address bits (A7:0), and port 2 carries the upper address bits (A15:8) and the data (D7:0).

### 8XC151SA/SB HARDWARE DESCRIPTION

## Table 8. User Configuration Byte UCONFIG0

| JConfig0        |            |                                     |                          |               |                | Address:       | FFF8H |  |  |  |

|-----------------|------------|-------------------------------------|--------------------------|---------------|----------------|----------------|-------|--|--|--|

| _               | WSa1#      | WSa0                                | # XALE#                  | _             | _              | Page#          | _     |  |  |  |

| MSB             |            |                                     | ·                        | •             |                |                | LSB   |  |  |  |

| Bit<br>Mnemonic |            |                                     |                          | Function      |                |                |       |  |  |  |

| WSa1#           | Wait State | Wait State Select for External Code |                          |               |                |                |       |  |  |  |

|                 | WSa1#      | WSa0#                               |                          | Descri        | ption          |                |       |  |  |  |

|                 | 1          | 1                                   | No Wait State            |               |                |                |       |  |  |  |

|                 | 1          | 0                                   | Insert 1 Code Wait State |               |                |                |       |  |  |  |

|                 | 0          | 1                                   | Insert 2 Code Wait State |               |                |                |       |  |  |  |

|                 | 0          | 0                                   | Insert 3 Code V          | Vait State    |                |                |       |  |  |  |

| XALE#           | Extended   | ALE                                 |                          |               |                |                |       |  |  |  |

|                 | XALE#      |                                     | Description              |               |                |                |       |  |  |  |

|                 | 1          |                                     | ALE pulse = 1            | Clock Period  |                |                |       |  |  |  |

|                 | 0          |                                     | ALE pulse = 3            | Clock Period  | (Additional 1  | Wait State)    |       |  |  |  |

| Page#           | Page Mod   | de Select                           |                          |               |                |                |       |  |  |  |

|                 | Page#      |                                     | Description              |               |                |                |       |  |  |  |

|                 | 1          |                                     | Non-Page Mod             | e (A15:8 on P | ort 2, A7:0/D  | 7:0 on Port 0) |       |  |  |  |

|                 | 0          |                                     | Page-Mode (A1            | 5:8/D7:0 on   | Port 2, A7:0 c | on Port 0)     |       |  |  |  |

## Table 9. User Configuration Byte UCONFIG1

| JConfig1        |           |             |                 |            |       | Address: | FFF9H |  |  |

|-----------------|-----------|-------------|-----------------|------------|-------|----------|-------|--|--|

| _               | _         | _           | _               | _          | WSb1# | WSb0#    | _     |  |  |

| MSB             |           | ·           |                 |            |       |          | LSB   |  |  |

| Bit<br>Mnemonic |           | Function    |                 |            |       |          |       |  |  |

| WSb1#           | Wait Stat | e Select fo | r External Data |            |       |          |       |  |  |

|                 | WSb1#     | WSb0#       | Descript        | ion        |       |          |       |  |  |

|                 | 1         | 1           | No Wait State   |            |       |          |       |  |  |

|                 | 1         | 0           | Insert 1 Data W | /ait State |       |          |       |  |  |

|                 | 0         | 1           | Insert 2 Data W | /ait State |       |          |       |  |  |

|                 | 0         | 0           | Insert 3 Data W | /ait State |       |          |       |  |  |

| Mode    | Buo Cyclo                    | Bus Activity   |                    |                     |  |  |  |

|---------|------------------------------|----------------|--------------------|---------------------|--|--|--|

| wode    | Bus Cycle                    | State 1        | State 2            | State 3             |  |  |  |

| Nonpage | Code Read                    | ALE            | RD#/PSEN#, Code In |                     |  |  |  |

| Mode    | Data Read (Note 2)           | ALE            | RD#/PSEN#          | Data In             |  |  |  |

|         | Data Write (Note 2)          | ALE            | WR#                | WR # High, Data Out |  |  |  |

| Page    | Code Read, Page Miss         | ALE            | RD#/PSEN#, Code In |                     |  |  |  |

| Mode    | Code Read, Page Hit (Note 3) | PSEN#, Code In |                    |                     |  |  |  |

|         | Data Read (Note 2)           | ALE            | RD#/PSEN#          | Data In             |  |  |  |

|         | Data Write (Note 2)          | ALE            | WR#                | WR # High, Data Out |  |  |  |

#### Table 10. Bus Cycle Definitions (No Wait States)

#### NOTES:

1. Signal timing implied by this table is approximate (idealized).

2. Data read (page mode) = data read (nonpage mode) and write (page mode) = write (nonpage mode) except that in page mode data appears on P2 (multiplexed with A15:0), whereas in nonpage mode data appears on P0 (multiplexed with A7:0).

3. The initial code read page hit bus cycle can execute only following a code read page miss cycle.

#### **4.7.1 BUS CYCLE DEFINITION**

Table 10 lists the types of external bus cycles. It also shows the activity on the bus for nonpage mode and page mode bus cycles with no wait states. There are three types of nonpage mode bus cycles: code read, data read, and data write. There are four types of page mode bus cycles: code read (page miss), code read (page hit), data read, and data write. The data read and data write cycles are the same for page mode and nonpage mode (except the multiplexing of D7:0 on ports 0 and 2). In nonpage mode, the external bus structure is the same as for MCS 51 microcontrollers. The upper address bits (A15:8) are on port 2, and the lower address bits (A7:0) are multiplexed with the data (D7:0) on port 0. External code read bus cycles execute in approximately two state times. See Table 10 and Figure 8. External data read bus cycles (Figure 9) and external write bus cycles (Figure 10) execute in approximately three state times. For the write cycle (Figure 10), a third state is appended to provide recovery time for the bus.

Figure 8. External Bus Cycle: Code Fetch, Nonpage Mode

## 8XC151SA/SB HARDWARE DESCRIPTION

## intel

Figure 9. External Bus Cycle: Data Read, Nonpage Mode

Figure 10. External Bus Cycle: Data Write, Nonpage Mode

Page mode increases performance by reducing the time for external code fetches. Under certain conditions the controller fetches an instruction from external memory in one state time instead of two. Page mode does not affect internal code fetches.

The first code fetch to a 256-byte "page" of memory always uses a two-state bus cycle. Subsequent successive code fetches to the same page (*page hits*) require only a one-state bus cycle. When a subsequent fetch is to a different page (*a page miss*) it again requires a two-state bus cycle. The following external code fetches are always page-miss cycles:

- the first external code fetch after a page rollover†

- the first external code fetch after an external data bus cycle

- the first external code fetch after powerdown or idle mode

- the first external code fetch after a branch, return, interrupt, etc.

Figure 11 shows the two types of external bus cycles for code fetches in page mode. The *page-miss* cycle is the same as a code fetch cycle in nonpage mode (except D7:0 is multiplexed with A15:8 on P2). For the *page-hit* cycle, the upper eight address bits are the same as for the preceding cycle. Therefore, ALE is not asserted, and the values of A15:8 are retained in the address latches. In a single state, the new values of A7:0 are placed on port 0, and memory places the instruction byte on port 2. Notice that a page hit reduces the available address access time by one state. Therefore, faster memories may be required to support page mode.

The bus cycles for data reads and data writes in page mode are identical to those for nonpage mode, except for the different signals on ports 0 and 2.

<sup>†</sup>During a sequence of page hits, PSEN # remains low until the end of the last page-hit cycle.

### Figure 11. External Bus Cycle: Code Fetch, Page Mode

Figure 12. External Bus Cycle: Data Read, Page Mode

Figure 13. External Bus Cycle: Data Write, Page Mode

#### 4.7.2 EXTERNAL BUS CYCLES WITH WAIT STATES

The C151SX can be configured to add wait states to the external bus cycles by extending the RD#/WR#/ PSEN# pulses or by extending the ALE pulse. Configuration bites WAS1:0# and WSB1:0# specify 0, 1, 2, or 3 wait states for RD#/WR#/PSEN#. The XALE# configuration bit specifies 0 or 1 wait state for ALE. You can also configure the chip to use both types of wait states. Accesses to on-chip code and data memory always use zero wait states.

Figure 14. External Bus Cycle: Data Write with One WR# Wait State (Nonpage Mode)

Figure 15. External Bus Cycle: Code Fetch with One ALE Wait State (Nonpage Mode)

Figure 15 shows the nonpage mode code fetch external bus cycle with ALE extended. The wait state extends the bus cycle from two states to three. For read and write external bus cycles, the extended ALE extends the bus cycle from three states to four.

## 4.7.3 PORT 0 AND PORT 2 FOR STATES IN NON-PAGE AND PAGE MODE

In nonpage mode the port pins have the same signals as those on the 8XC51FX. For an external memory instruction using a 16-bit address, the port pins carry address and data bits during the bus cycle. However, if the instruction uses an 8-bit address (e.g., MOVX@Ri), the contents of P2 are driven onto the pins. These pin signals can be used to select 256-bit pages in external memory. During a bus cycle, the CPU always writes FFH to P0, and the former contents of P0 are lost. A bus cycle does not change the contents of P2. When the bus is idle, the port 0 pins are held at high impedance, and the contents of P2 are driven onto the port 2 pins.

In a page-mode bus cycle, the data is multiplexed with the upper address byte on port 2. However, if the instruction uses an 8-bit address (e.g., MOVX@Ri), the contents of P2 are driven onto the pins when data is not on the pins. These logic levels can be used to select 256bit pages in external memory. During bus idle, the port 0 and port 2 pins are held at high impedance.

## 5.0 TIMERS/COUNTERS

The C151SX has three 16-bit Timer/Counters: Timer 0, Timer 1, and Timer 2. Each consists of two 8-bit registers, THx and TLx, (x = 0, 1, and 2). All three can be configured to operate either as timers or event counters.

In the Timer function, the TLx register is incremented every machine cycle. Thus one can think of it as counting machine cycles. Since a machine cycle consists of 12 oscillator periods, the count rate is  $\frac{1}{12}$  of the oscillator frequency.

In the Counter function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin—T0, T1, or T2. In this function, the external input is sampled during S5P2 of every machine cycle. When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register during S3P1 of the cycle following the one in which the transition was detected. Since it takes 2 machine cycles (24 oscillator periods) to recognize a 1-to-0 transition, the maximum count rate is  $\frac{1}{24}$  of the oscillator frequency. There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it should be held for at least one full machine cycle.