# **Intel® 82371AB (PIIX4)**

**Specification Update**

**April 1999**

**Notice:** The Intel® 82371AB (PIIX4) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this Specification Update.

Order Number: 297738-011

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® 82371AB (PIIX4) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

\*Third-party brands and names are the property of their respective owners.

Copyright © Intel Corporation 1997, 1998, 1999

2

| Revision History             |    |

|------------------------------|----|

| Preface                      |    |

| Specification Changes        | 10 |

| Errata                       | 13 |

| Specification Clarifications | 23 |

| Documentation Changes        | 34 |

# **Revision History**

| Rev. | Draft/Changes                                                                                                         |         |  |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|

| -001 | Initial Release                                                                                                       | Oct. 97 |  |  |  |  |

| -002 | Added PIIX4 Errata #11.                                                                                               | Dec. 97 |  |  |  |  |

| -003 | Added Specification Change #2, Errata #12 and #13, and Documentation Change #6.                                       | Mar. 98 |  |  |  |  |

| -004 | Added Specification Change #3, Errata #14, Specification Clarifications #18 and #19, Documentation Changes #7 and #8. | Apr. 98 |  |  |  |  |

| -005 | Added Errata #15 and Specification Clarification #20.                                                                 | Jun. 98 |  |  |  |  |

| -006 | Added Specification Change #4, Specification Clarifications #21-24 and Documentation Change #9.                       | Jul. 98 |  |  |  |  |

| -007 | Added Errata #16.                                                                                                     | Aug. 98 |  |  |  |  |

| -008 | Added Specification Changes #5 - #7.                                                                                  | Oct. 98 |  |  |  |  |

| -009 | Added Specification Change #8 and Errata's #17–19.                                                                    | Feb. 99 |  |  |  |  |

| -010 | Added Specification Change #9 and Errata #20                                                                          | Mar. 99 |  |  |  |  |

| -011 | Added Specification Change #10 and Errata #21                                                                         | Apr. 99 |  |  |  |  |

This document is an update to the specifications contained in the Intel® 82371AB PIIX4 Datasheet, Revision 1.0, Intel 82371AB (PIIX4) PCI ISA IDE Xcelerator Timing Specification order number (273135). It is intended for hardware system manufacturers and software developers of applications operating systems or tools. It contains Specification Changes, Errata, Specification Clarifications, and Documentation Changes.

# **Nomenclature**

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in the next release of the specifications.

Errata are design defects or errors. Errata may cause the Intel® 82371AB PIIX4, behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in the next release of the specifications.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These changes will be incorporated in the next release of the specifications.

# Component Identification via Programming Interface

The Intel® 82371AB PIIX4 may be identified by the following register contents:

| Stepping            | Vendor ID <sup>1</sup> | Device ID <sup>2</sup> | Revision Number <sup>3</sup>      |

|---------------------|------------------------|------------------------|-----------------------------------|

| PIIX4 A-0, A-1, B-0 | 8086h                  | 7110h                  | See Documentation Changes section |

#### NOTES:

- 1. The Vendor ID corresponds to bits 15-0 of the Vendor ID Register located at offset 00-01h in the PCI function 0 configuration space.

- 2. The Device ID corresponds to bits 15-0 of the Device ID Register located at offset 02-03h in the PCI function 0 configuration space.

- 3. The Revision Number correspond to bits 7-0 of the Revision ID Register located at offset 08h in the PCI function 0 configuration space.

# **Component Marking Information**

The Intel® 82371AB PIIX4 may be identified by the following component marking:

| Stepping  | S-Spec | Top Marking      | Notes                             |

|-----------|--------|------------------|-----------------------------------|

| PIIX4 A-0 |        | FW82371AB Q518ES | Engineering Sample, FM Test       |

| PIIX4 A-0 |        | FW82371AB Q519ES | Engineering Sample, T3 Test       |

| PIIX4 A-1 |        | FW82371AB Q532ES | Engineering Sample, FM Test       |

| PIIX4 A-1 |        | FW82371AB Q533ES | Engineering Sample, T3, Burn in   |

| PIIX4 B-0 |        | FW82371AB Q534ES | Engineering Sample, FM Test       |

| PIIX4 B-0 |        | FW82371AB Q535ES | Engineering Sample, T3, Burn in   |

| PIIX4 B-0 | SL23P  | FW82371AB SL23P  | Production                        |

| PIIX4 B-0 | SL2KM  | FW82371AB SL23P  | Production, Multiple FPO per Reel |

# **Summary Table of Changes**

The following table indicates the Specification Changes, Errata, Specification Clarifications or Documentation Changes, which apply to the listed Intel® 82371AB PIIX4 steppings. Intel intends to fix some of the errata in a future stepping of the component and to account for the other outstanding issues through documentation or Specification Changes as noted. This table uses the following notations:

# **Codes Used in Summary Table**

X: Erratum, Specification Change or Clarification that applies to this stepping.

Doc: Document change or update that will be implemented.

Fix: This erratum is intended to be fixed in a future stepping of the component.

Fixed: This erratum has been previously fixed.

NoFix There are no plans to fix this erratum.

(No mark) or (Blank Box): This erratum is fixed in listed stepping or specification change does not

apply to listed stepping.

Shaded: This item is either new or modified from the previous version of the

document.

| NO. | A0 | <b>A1</b> | В0 | PLANS | SPECIFICATION CHANGES                |

|-----|----|-----------|----|-------|--------------------------------------|

| 1   | Х  | Х         | Х  | DOC   | INTPN Register Not Implemented       |

| 2   | X  | Х         | Х  | DOC   | Aliased NMI Enable bit               |

| 3   | Х  | Х         | Х  | DOC   | IRQ9OUT# is active level HI          |

| 4   | X  | Х         | Х  | DOC   | CLKRUN# Re-Assertion                 |

| 5   | X  | Х         | Х  | DOC   | CNTB Granularity                     |

| 6   | Х  | Х         | Х  | DOC   | CPU Stop Clcok Exit Behavior         |

| 7   | Х  | Х         | Х  | DOC   | IDE Data Hold (t115b) Change         |

| 8   | X  | Х         | Х  | DOC   | Vcc Specification Change             |

| 9   | Х  | Х         | Х  | DOC   | INTLN Register Not Implemented       |

| 10  | Χ  | X         | X  | DOC   | USB Host Controller Supports USB 1.1 |

| NO. | Α0 | <b>A1</b> | В0 | PLANS | ERRATA                                                                                |

|-----|----|-----------|----|-------|---------------------------------------------------------------------------------------|

| 1   | Х  | Х         | Х  | NoFix | Burst Events may cause LVL2 or LVL3 register reads to be missed                       |

| 2   | Х  | Х         | Х  | NoFix | PCI accesses to External PCI-based IDE Devices will not cause Power Management Events |

| 3   | Х  | Х         | Х  | NoFix | General Purpose Outputs default to incorrect values                                   |

| 4   |    |           | Х  | NoFix | USB Bandwidth Reclamation Errata                                                      |

| 5   | Х  | Х         | Х  | NoFix | STPCLK# Deassertion Time                                                              |

| 6   | Χ  | Χ         | Х  | NoFix | Device Trap                                                                           |

| 7   | Х  | Х         | Х  | NoFix | USB Rise / Fall Time Matching                                                         |

| 8   | Х  | Х         | Х  | NoFix | System Resume on USB OC# Assertion                                                    |

| 9   | Х  | Х         | Х  | NoFix | PCI Arbiter Advances when PC/PCI ISA Master Gets Retried by the Host Controller       |

| 10  | Х  | Х         | Х  | NoFix | Bus Master IDE Timeout                                                                |

| 11  | Χ  | Χ         | Х  | NoFix | USB-PCI Latency                                                                       |

| 12  | Х  | Х         | Х  | NoFix | Device Monitor 9 and access to IO locations 62/66h                                    |

| 13  | Х  | Х         | Х  | NoFix | USB Resume from Selective Suspend                                                     |

| 14  | Х  | Х         | Х  | NoFix | IRQ9OUT# is active HI                                                                 |

| 15  | Х  | Х         | Х  | NoFix | IDE Prefetch                                                                          |

| 16  | Х  | Х         | Х  | NoFix | SMI# Timing                                                                           |

| 17  | Х  | Х         | Х  | NoFix | ISA Verify followed by PCPCI DMA                                                      |

| 18  | Х  | Х         | Х  | NoFix | C3 Power State/BMIDE & Type-F DMA Livelock Errata                                     |

| 19  | Х  | Х         | Х  | NoFix | USB Dribble Errata                                                                    |

| 20  | Х  | Х         | Х  | NoFix | ACPI Timer Errata                                                                     |

| 21  | Х  | Х         | Х  | NoFix | Daylight Savings Time Errata                                                          |

| NO. | Α0 | <b>A</b> 1 | В0 | PLANS | SPECIFICATION CLARIFICATIONS                          |

|-----|----|------------|----|-------|-------------------------------------------------------|

| 1   | Х  | Х          | Х  | DOC   | SUSA#, SUSB#, and SUSC# State Transition During Reset |

| 2   | Х  | Х          | Х  | DOC   | CONFIG[1] Definition                                  |

| 3   | Х  | Х          | Х  | DOC   | IRQ8# Routing                                         |

| 4   | Х  | Х          | Х  | DOC   | IRQ9 Routing                                          |

| 5   | Х  | Х          | Χ  | DOC   | SERIRQ Sample Phase                                   |

| 6   | Х  | Х          | Х  | DOC   | RI# Pulse Width Requirement                           |

| 7   | Х  | Х          | Х  | DOC   | Diode Requirement for Vref Sequencing Circuit         |

| 8   | Х  | Х          | Х  | DOC   | SMI# Generation from APMC Write                       |

| 9   | Х  | Х          | Х  | DOC   | Power Button Override                                 |

| NO. | Α0 | A1 | В0 | PLANS | SPECIFICATION CLARIFICATIONS                                            |

|-----|----|----|----|-------|-------------------------------------------------------------------------|

| 10  | Х  | Х  | Х  | DOC   | RTC Status Bit Clarification                                            |

| 11  | Х  | Х  | Х  | DOC   | SCI_EN Bit Clarification                                                |

| 12  | Х  | Х  | Х  | DOC   | Thermal Override Initiates Throttling Even in Clock Control State       |

| 13  | Х  | Х  | Х  | DOC   | No Disabling Break Events During A Burst                                |

| 14  | Х  | Х  | Х  | DOC   | Unrouting a PIRQ                                                        |

| 15  | Х  | Х  | Х  | DOC   | IDE Device Detection                                                    |

| 16  | Х  | Х  | Х  | DOC   | Physical Region Descriptor Alignment                                    |

| 17  | Х  | Х  | Х  | DOC   | RTC Index Register Read                                                 |

| 18  | Х  | Х  | Х  | DOC   | GPI[1] Minimum Assertion                                                |

| 19  | Х  | Х  | Х  | DOC   | RSMRST# Behavior                                                        |

| 20  | Х  | Х  | Х  | DOC   | SM Bus Busy Bit Behavior                                                |

| 21  | Х  | Х  | Х  | DOC   | GPI14 for Device 5 Can Cause IO Trap SMI#                               |

| 22  | Х  | Х  | Х  | DOC   | XDIR# Assertion                                                         |

| 23  | Х  | Х  | Х  | DOC   | Correction to USB Bandwidth Reclamation Errata Workaround               |

| 24  | Х  | Х  | Х  | DOC   | Do Not Use 4-Clock Serial IRQ Start Frame Width When CLKRUN# is Enabled |

| NO. | Α0 | <b>A1</b> | В0 | PLANS | DOCUMENTATION CHANGES                                            |

|-----|----|-----------|----|-------|------------------------------------------------------------------|

| 1   | Х  | Х         | Х  |       | PCI Revision ID Register Values                                  |

| 2   | Х  | Х         | Х  | DOC   | Interval Timer for IRQ0                                          |

| 3   | Х  | Х         | Х  | DOC   | Bus Master Activity for Burst Events                             |

| 4   | Х  | Χ         | Х  | DOC   | IRQ9 and IRQ9OUT# Pin Locations                                  |

| 5   | Х  | Х         | Х  | DOC   | PIO0 Timing Values                                               |

| 6   | Х  | Χ         | Х  | DOC   | Sleep and Deep Sleep for Pentium®II processors only              |

| 7   | Х  | Х         | Х  | DOC   | SMI# Minimum Deassertion Time                                    |

| 8   | Х  | Х         | Х  | DOC   | Datasheet t37 Correction                                         |

| 9   | Х  | Х         | Х  | DOC   | Corrections to Simplified Block Diagram, Table 55, and Figure 34 |

# Specification Changes

# 1. INTPN Register Not Implemented

The PIIX4 Datasheet section 7.1.9 specified that the INTPN register indicates the PCI interrupt pin PIRQA# is used for routing Serial Interrupts. However, Serial Interrupts are hardwired to IRQ9. This register is not implemented.

This change applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 Datasheet.

# 7.1.9 INTPN—INTERRUPT PIN (FUNCTION 3)

Address Offset: 3Dh

Default Value: 00h

Attribute: Read only

This register indicates that PCI interrupt pin PIRQA# is used for the Power Management module.

| Bit | Description     |

|-----|-----------------|

| 7:0 | Not Implemented |

#### 2. Aliased NMI Enable bit

The PIIX4 Datasheet, section 4.2.5.3, Real Time Clock Extended Index Register (IO), bit 7 description changes from Reserved to Aliased NMI Enable. This bit must always reflect the state of the NMI Enable bit, NMIEN[7] in IO space 70h.

### 3. IRQ9OUT# is Active Level HI

The PIIX4 Datasheet, and Datasheet Addendum, in several places identifies pin F3 (IRQ9OUT#/GPO29) as IRQ9OUT being active level LO. When IRQ9OUT functionality is selected, the IRQ9OUT is active level HI, not active level LO. The name of this pin is changed to IRQ9OUT/GPO29.

### 4. CLKRUN# Re-Assertion

The PIIX4 Datasheet on page 210, section 11.2.3, states if no other device in the system denies the request to stop before the 5<sup>th</sup> PCI clock, then the PiiX4 asserts the PCI\_STP#. Any device must deny the request to stop before the 4<sup>th</sup> PCI clock.

# 5. CNTB Granularity

The PIIX4 Datasheet, section 7.1.12, defines the Count B (Function 3) Register functionality. CNTB[5] currently indicates that when this bit is set that the fast burst timer granularity is 1uS. This is incorrect, the granularity, when CNTB[5] is set is 8uS.

This change applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

# 7.1.12 CNTB—Count b (FUNCTION 3)

Address Offset: 48-4Bh

Default Value: 00h

Attribute: Read/Write

| Bit | Description                                                                                                                                                                                     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | <b>Processor PLL Lock Resolution (CPU_SEL) - R/W.</b> Selects the clock resolution used for the fast burst timer when it is used to count the processor's PLL lock time. 0= 1mS granularity. 1= |

|     | 8uS granularity.                                                                                                                                                                                |

# 6. CPU Stop Clock Exit Behavior

The PIIX4 Datasheet, section 11.2.2, page 209, describes the behavior when the processor is leaving the STOP CLOCK STATE. The first sentence in the third and forth bullets are incorrect.

The phrase "PiiX4 waits for the processor PLL to start and lock (about 1mS + 32khz period) then negates the SUS\_STAT1# signal {4}." Is inaccurate. This sentence will be replaced by "PiiX4 waits for the processor PLL to start and lock (about CPU\_LCK time + 32 khz period) then negates the SUS\_STAT1# signal {4}."

The sentence "PIIX4 waits up to 2-32khz periods and then negates the STPCLK# signal {5}." Is inaccurate. This sentence will be replaced by "PiiX4 waits 2-3 32khz periods (if SLEEP\_EN=0), or 3-5 32khz periods (if SLEEP\_EN=1) and then negates the STPCLK# signal {5}."

This change applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

# 7. IDE Data Hold (t115b) Change

The 82371AB (PIIX4) PCI ISA IDE Xcelerator Timing Specification, in Table 8 (PCI BUS IDE Timings) defines t115b as an 8nS min specification. This is specification is changed to 7nS min to meet ATA Specification data hold requirements.

# 8. Vcc Specification Change

The 82371AB (PIIX4) PCI ISA IDE Xcelerator Timing Specifications Document identifies the VCC range as 3.3v +/- .3V. This specification is changed to 3.3V +/- 5% for both the PIIX4 and the PIIX4E.

# 9. INTLN Register Not Implemented

The PIIX4 Datasheet specified that the INTLN register contains interrupt information concerning the power management module. However, this register is not implemented and is RESERVED.

This change applies to all steppings of the PIIX4 and PIIX4E and will be incorporated into the next revision of the datasheets.

# 10. USB Host Controller Supports USB 1.1

The PIIX4 Datasheet specifies that the USB Host Controller is USB supports the USB Revision 1.0 Specification. The USB Host Controller in the PIIX4 is USB Revision 1.1 compliant.

This change applies to all steppings of the PIIX4 and PIIX4E and will be incorporated into the next revision of the datasheet.

# Errata

### 1. Burst Events May Cause LVL2 or LVL3 Register Reads to be Missed

**Problem:** Burst events that occur after Burst Enable bit (BST\_EN) has been set and before the Processor Level 2

(LVL2) or Processor Level 3 (LVL3) register read may cause the LVL2 or LVL3 read to be missed.

**Implication:** When the above conditions occur, the system will not transition into the Level 2 or Level 3 clock control

condition as intended but will remain at full speed

**Workaround:** Software must ensure that no external burst events are active when placing the system into a LVL2 or

LVL3 state. To ensure this, prior to LVL2 or Software must ensure that no external burst events are active when placing the system into a LVL2 or LVL3 state. To ensure this, prior to LVL2 or LVL3 register read, only the Device 3 idle timer should be enabled as a burst event. The device 3 idle timer is then enabled with all reload events disabled. The LVL2 or LVL3 register read is performed placing the system into a LVL2 or LVL3 clock control condition. The Device 3 idle timer will then generate a burst event upon expiration. During this first burst, the desired burst events are then enabled. The system then

functions as expected.

**Status:** This will not be fixed in PIIX4. This was incorporated into the PIIX4 datasheet as a change to the

specification.

2. PCI accesses to External PCI-based IDE Devices will not cause Power Management Events

**Problem:** PCI accesses to external IDE devices on the PCI bus do not generate power management events (Idle

timer reloads, global standby timer reloads, burst timer reloads, I/O traps).

**Implication:** Power management of external PCI-based IDE devices must use other means to monitor the activity of

those devices.

Workaround: System BIOS should use the following methods to monitor external PCI-based IDE devices:

1. If there is a need to monitor accesses to the IDE controller to keep the global standby timer from expiring, then the IRQs should be enabled (GRLD\_EN\_IRQ) as a reload event for the global standby timer.

- 2. If there is a need to monitor an external IDE controller for idleness, use the following algorithm:

- a. Disable the external IDE controller. Set the PIIX4 to trap on the IDE access and enable the internal IDE controller.

- b. When the SMI is generated, the idle timer can be started, the internal IDE controller disabled, and the instruction redone to the external IDE controller. The IDE device is then assumed to be active during idle timer count down.

- c. When the idle timer times out, an SMI is generated and the PIIX4 should again be set to trap, the external IDE device disabled, and the idle timer started.

- d. If the idle timer times out before the trap occurs, then the external IDE controller is idle and can be put into a lower power mode. The PIIX4 is then set up to trap as in 3. below.

- e. If the trap occurs first, the IDE device is not idle. The BIOS then returns to step b. above

- 3. If there is a need to perform I/O trapping on an external IDE controller, set the PIIX4 to trap on the IDE access and enable the PIIX4 internal IDE controller. When the SMI is generated, the internal IDE controller can be disabled, the external controller enabled, and the I/O cycle restarted.

Status:

This will not be fixed in PIIX4. This was incorporated into the PIIX4 Datasheet as a change to the specification.

#### 3. **General Purpose Outputs default to Incorrect Values**

Problem:

The General Purpose Output register (Power Management Base + 34h,35h,36h,37h) incorrectly defaults to 7FFFBFFh instead of 00000000h.

| Register<br>Bits<br>(GP0 #) | Actual Default<br>Value | Comments   |

|-----------------------------|-------------------------|------------|

|                             |                         |            |

| 31                          | 0                       | No GPO[31] |

|                             |                         |            |

| 30:15                       | 1                       |            |

|                             |                         |            |

| 14                          | 0                       |            |

|                             |                         |            |

| 13:0                        | 1                       |            |

**Implication:** Systems designs which depend on GPO value at reset or depend on default values of 0h will not work correctly.

Workaround: System designers should be aware of the new default values. For dedicated GPOs or multiplexed GPOs which default to GPO, and which require a specific value at reset, inverters may need to added or removed from the system design. For GPOs which are multiplexed with other signals but which default to a non-GPO signal, the BIOS must ensure that the proper value is written into the GPO register prior to enabling the signal as a GPO.

Status:

This will not be fixed in PIIX4. This was incorporated into the PIIX4 Datasheet as a change to the specification.

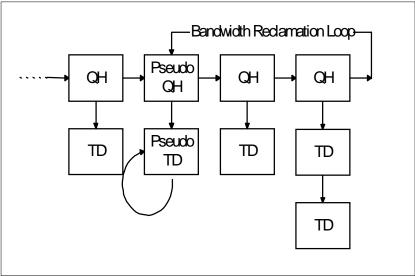

#### 4. **USB Bandwidth Reclamation Errata**

Problem:

This errata affects data transfers in conjunction with a UHCI driver utilizing bandwidth reclamation. In a data structure which implements bandwidth reclamation, when all the queue heads have their terminate bit set (empty QH's), the USB subsystem will be unable to read a new frame pointer and will continuously loop through the bandwidth reclamation queue heads. The effect of the errata is that the USB subsystem will continue to send out Start Of Frame packets but transfer no data. On the PCI bus the PIIX4 will continuously read the queue heads within the bandwidth reclamation loop. For additional information on PIIX4 host controller operation refer to the Universal Host Controller Interface (UHCI) Design Guide (order number 297650).

**Implication:** The USB host controller stops transferring data on the USB bus. The non-USB functions in the system will continue to operate normally.

Workaround: When using bandwidth reclamation, the UHCI driver should insert a pseudo queue head with a pseudo transfer descriptor within the bandwidth reclamation loop. The PIIX4 will fetch this queue head and transfer descriptor on every frame, but will not transfer any data and will never be terminated. The following bits must be properly set to implement the workaround:

# TD LINK POINTER (DWORD 0: 00-03h)

The Link Pointer (LP=bits [31:4]) must be set to point to itself.

The Depth/Breadth Select bit (Vf=bit 2) must be set to 0 indicating that the PIIX4 should execute breadth first.

The QH/TD Select (Q=bit 1) must be set to 0 indicating it is a TD.

The Terminate bit (T=bit 0) must be set to 0 indicating that the link pointer field is valid.

# TD CONTROL AND STATUS (DWORD 1: 04-07h)

The Active status bit (bit 23) must be left unset at 0 indicating that the PIIX4 should not execute this TD.

### QUEUE HEAD LINK POINTER (DWORD 0: 00-03h)

The Queue Head Link Pointer (QHLP=bits [31:4]) must be set to point to the pseudo TD.

The QH/TD Select (Q=bit 1) must be set to 1 indicating it is a QH.

The Terminate bit (T=bit 0) must be set to 0 indicating that the link pointer field points to a valid TD.

#### Status:

- This errata will not be fixed in PIIX4.

- This errata will be incorporated into the next revision of the PIIX4 Datasheet as a specification change.

- Intel is working with Microsoft to incorporate the workaround into their UHCI driver.

- Microsoft will make this workaround available in the Beta 1 release of Memphis.

- Microsoft will provide a fix to the OSR2.1 (Detroit) release. OEMs/IHVs should contact Microsoft for the fix distribution plans.

#### 5. STPCLK# Deassertion Time

**Problem:** Under certain conditions the PIIX4 can deassert STPCLK# for a short time. A short deassertion of

STPCLK# can cause the CPU to miss the STPCLK# transition. If the CPU misses the transition the

PIIX4 will continue to assert STPCLK# indefinitely.

**Implication:** The system will hang if the PIIX4 holds STPCLK# asserted indefinitely.

Workaround: The 87% thermal duty cycle (THRM\_DTY) in the CNTB register, and the 87% throttle duty cycle

(THTL\_DTY) in the PCNTRL register is no longer supported. These bit positions are now reserved. System BIOS must also disable system clock control before the PIIX4 begins thermal throttling.

If the THRM\_EN bit is set and the SCI\_EN bit is cleared, an SMI# is generated by the PIIX4 upon assertion of the THRM# signal. The SMI# handler has 2 seconds to disable all system clock control functionality before the PIIX4 begins thermal throttling.

If the THRM\_EN bit is set and the SCI\_EN bit is set, an SCI is generated by the PIIX4 upon assertion of the THRM# signal. The interrupt handler has 2 seconds to disable all system clock control functionality before the PIIX4 begins thermal throttling.

**Status:** This will not be fixed on PIIX4. This will be incorporated into the PIIX4 datasheet as a change to the

specification.

### 6. Device Trap

**Problem:** When the PIIX4 has the Device Trap logic enabled for Devices 0-13, it forwards the I/O access cycles

for the device to the EIO/ISA and IDE Bus.

**Implication:** Accesses to devices in a powered down state could cause unpredictable results.

Workaround: Upon a powerdown event for devices 0-3 (IDE) the SMI handler must save the IDE register settings in

CMOS, disable IORDY, and set PIO transfers for compatible timings. Upon a powerup event for

devices 0-3, the SMI handler must restore all original IDE register settings.

Upon a powerdown event for all other devices (using EIO), the SMI handler must disable the EIO decode and enable the trap logic for that device. Upon a powerup event, the SMI handler must enable

the EIO decode and disable the trap logic.

**Status:** This will not be fixed on PIIX4. This will be incorporated into the PIIX4 datasheet as a change to the

specification.

7. USB Rise/Fall Time Matching

**Problem:** The USB Specification defines a Rise / Fall Time Matching (TRFM) which is calculated by dividing Rise

Time by Fall Time (T<sub>R</sub> / T<sub>F</sub>). The specification for a full speed device is 90% minimum and 110%

maximum. Simulation shows that the PIIX4 does not meet this specification.

**Implication:** None, USB functionality is unaffected because the PIIX4 does meet the required output signal crossover

voltage specifications (VcRs).

Workaround: None required.

Status: This will not be fixed on PIIX4. This will be incorporated into the PIIX4 datasheet as a change to the

specification.

8. System Resume on USB OC# Assertion

**Problem:** In POS, an oscillating CLK48 and an OC# assertion cause the USB\_STS bit to be set triggering a system

resume. Typically systems turn off the CLK48 signal in POS which prevents the system resume. However, after entering POS there is a short period of time as CLK48 turns off where it still oscillates.

An assertion of OC# before CLK48 completely stops can cause a system resume.

Implication: In POS, an oscillating CLK48 and an OC# assertion cause the USB\_STS bit to be set triggering a system

resume. Typically systems turn off the CLK48 signal in POS which prevents the system resume. However, after entering POS there is a short period of time as CLK48 turns off where it still oscillates.

An assertion of OC# before CLK48 completely stops can cause a system resume.

Workaround: None.

**Status:** This will not be fixed on PIIX4. This will be incorporated into the PIIX4 datasheet as a change to the

specification.

9. PCI Arbiter Advances when PC/PCI ISA Master Gets Retried by the Host

Controller

**Problem:** When a PC/PCI ISA master cycle gets retried (delayed transaction) by the host controller, the PIIX4 PCI

Arbiter advances to a pending PCI master (USB or IDE). Affects 440BX-PIIX4-MoonISA Docking

platforms.

**Implication:** The 440BX host controller will delay transaction (retry) a PC/PCI ISA master cycle (PIIX4 DMA

controller in cascade mode) from PCI to DRAM. When the PIIX4 detects the retry, it will do a passive release on the PHLD# signal and allow another PCI master (440BX Arbiter) to acquire the bus. Following the passive release, the PIIX4 will un-intentionally advance its PCI arbiter to a pending PCI master request (USB or IDE). The 440BX expects to the next cycle from PIIX4 to be the delayed transaction cycle and will retry any other cycle (USB or IDE). The PIIX4 arbiter will stay on the USB or IDE bus master device until the delay transaction timeout in the 440BX. After the timeout the 440BX

drops the data possibly resulting in a system hang.

Workaround: None.

**Status:** This will not be fixed on PIIX4. This will be incorporated into the PIIX4 datasheet as a change to the

specification.

#### 10. Bus Master IDE Timeout

**Problem:** During an IDE DMA write, the PIIX4 IDE controller will invalidate its FIFO if the IDE device deasserts

its DREQ signal for greater than 1us. During the FIFO invalidation, the PIIX4 does not prevent a FIFO

fill from PCI.

Implication: In Bus Master IDE (BMIDE) mode, the PCI interface is prefetching data. If this prefetched data gets

inserted into the IDE FIFO (during a FIFO invalidation due to DREQ deassertion > 1us) the IDE controller will lock up. Any future reassertion of the DREQ signal will not be acknowledged by the PIIX4 IDE controller. BMIDE transactions will not complete on either the primary or secondary

channel.

Workaround: If the controller locks up, the BMIDE driver must timeout, reset the PIIX4 Start/Stop Bus Master bit, and

retry the transfer. Note that this errata does not occur using PIO mode or Ultra DMA/33 mode.

**Status:** This will not be fixed on PIIX4. This will be incorporated into the PIIX4 Datasheet as a change to the

specification.

### 11. USB-PCI Latency

**Problem:** Under certain circumstances, PIIX4 will start an isochronous USB transfer when there is not enough time

to successfully complete the transaction.

Implication: This failure only occurs when some PCI devices introduce large (>15usec) latencies on the PCI bus in

combination with the USB transfer. In this situation, the USB port shuts down and requires the user to unplug the device, then plug it back in to get the device operational again. The rest of the system will

continue to operate normally.

Workaround: In all cases found to date, the software drivers of the PCI devices causing large delays can be modified to

reduce the latency to less than 15usec. When the PCI delays are reduced to this level the isochronous

USB transfers will operate normally.

**Status:** There are currently no plans to fix this erratum.

#### 12. Device Monitor 9 and access to IO locations 62/66h

**Problem:** 1. If the Device 9 Idle Enable (IDL EN DEV9), Burst Reload Enable (BRLD EN DEV9), or Global

Reload Enable (GRLD\_EN\_DEV9) bits are set; the idle, burst, or global standby timer will reload for

I/O accesses to ISA Legacy addresses 62 or 66h, regardless of the Generic Decode Monitor Enable bit

setting (GDEC\_MON\_DEV9).

2. If Device 9 Trap Enable bit (TRP\_EN\_DEV9) is set, the PiiX4 enables generation of a trap SMI for accesses to ISA Legacy addresses 62 or 66h regardless of the Generic Decode Monitor Enable bit setting (GDEC\_MON\_DEV9) and the value of the Programmable Base Address and Programmable Mask

register settings (BASE\_DEV9 & MASK\_DEV9)

**Implication:** 1. Device 9 cannot be used as a monitor for I/O device addresses exclusive of 62 and 66h.

2. GPI4 cannot be used exclusively to reload the idle, burst, or global standby timers because accesses to ISA Legacy addresses 62 or 66h will also reload the times.

NOTE: GPI4 is still available as a General Purpose Input.

Workaround: None. If a generic I/O device monitor exclusive of I/O address 62 and 66h is needed, then use Device 10, if it is available.

Status: This will not be fixed in the PIIX4.

#### 13. **USB Resume from Selective Suspend**

A USB resume sequence signaled by a downstream device, from the PIIX4, may not be properly detected by the PiiX4 if the USB clock is running and the USB port is in a Selective Suspend mode. A combination of VCRS level and device speed (HS/LS) may allow the PIIX4 to detect a SE1 level on a USB clock edge which the PiiX4 resume detect hardware cannot recognize.

Symptoms include either HC responds to downstream J to K transition by driving K state, but does not set PORTSC[Resume\_Detect], or the HC does not respond to downstream J to K transition by driving K state back onto the cable. These symptoms will manifest themselves as either the PIRQD interrupt will not assert and not interrupt or wake the system, or polling of PORTSC will never return a detect response and the K state will remain driven by the HC and locked up.

Problem:

**Implication:** If the system is in a state where USB clocks are running, such as normal or LVL3 power managed states, and the USB port is in Selective Suspend mode, a resume attempt initiated by the USB device, such as a keyboard, may not be detected and the suspended port may not resume. This failure to resume will prevent normal operation of the affected USB device, and if in a power managed state where USB clocks are still running, the system may not be awaken. In this case, the user will have to awaken the system another way and may have to un-plug and re-install the USB device to get it to work.

- Workaround: 1. Ensure that USB peripheral devices do not support remote wake-up (peripheral workaround), or

- 2. Do not use the Selective Suspend feature of the PiiX4, use only Global Suspend (OS workaround).

Status: This will not be fixed in the PIIX4.

#### IRQ9OUT# is Active HI 14.

Problem: The signal identified as IRQ9OUT#/GPO29, pin F3, is not active level LO, it is active level HI, when

APIC Chip Select (XBCS[8]) is set.

Implication: This signal is typically used in Dual Processor capable systems and is connected to an IOAPIC. If the

IOAPIC input is programmed for level LO, and SCI's or SM Bus events in the PiiX4 are programmed to be reported on IRQ9OUT, devices using these will not be recognized by the IOAPIC and will not work

correctly.

**Workaround:** Program the appropriate input of the IOAPIC to active level HI.

This will not be fixed in the PIIX4. This will be incorporated into the PIIX4 datasheet as a Specification Status:

Change.

#### 15. IDE Prefetch

**Problem:** While executing a PIO IDE Read Sector(s) or Read Multiple command with PIO pre-fetching enabled, a

read of a non-Data Register (such as ALT STATUS Register) may cause the PIIX4 PIO pre-fetch

counter to increment, incorrectly since it should only increment on data transfers.

**Implication:** The incorrect count causes the PIIX4 to confuse sector boundaries, resulting in invalid data being placed

in memory. This erratum was observed during validation testing executing special test software. No reports from internal testing or customer testing on production systems (i.e. without special test software) have been attributed to this errata to date. Intel customers should perform there own risk analysis on this

errata and determine the most appropriate work around for their systems.

**Workaround:** The work around for this errata is to not perform Non-Data register reads while an IDE PIO transfer is

taking place. In cases where this errata has been seen, an interrupt (IRQn or SMI) has been used to enter the code from which the ALT STATUS read occurs. Code which is not directly involved in the IDE transfer should not perform the ALT STATUS read to check status of IDE transfers. An alternative for PIIX4 based systems is to use IDE device idle timer to detect IDE activity. Another work around is to

disable IDE PIO prefetching.

**Status:** This will not be fixed in the PIIX4. This will be incorporated into the PIIX4 datasheet as a Specification

Change. An additional paper titled "82371FB PIIX, 82371SB PIIX3, 82371AB PIIX4, 82371EB PIIX4E IDE PREFETCH ERRATA DESCRIPTION is available from Intel, which describes this errata and risk analysis in greater detail. Intel is releasing this information to various operating system, BIOS vendors, and other software developers to allow them to analyze their code base and to minimize the

potential for future software programs to trigger this errata.

# 16. SMI# Timing

**Problem:** When the PIIX4 asserts STPCLK# at the same time that it traps an I/O cycle, the SMI# assertion may be

delayed until 5 PCI clocks after STPCLK# is deasserted. If this occurs, the Pentium® II processor will not recognize the SMI on the intended I/O instruction boundary and subsequent instructions will be executed prior to the intended SMI code execution. If the I/O restart feature of the processor is used, this could cause the processor to restart the wrong instruction, resulting in undefined processor behavior. Software in which the instruction that follow the trapped I/O instruction is dependent on a result returned by the I/O Trap SMI routine, may not execute correctly. PIIX4 I/O trap SMI includes device traps and

APM register write traps (0B2h).

**Implication:** The errata condition can occur in Pentium® II processor/PiiX4 systems that use I/O Trap SMI with

STPCLK# throttling enabled. The observed effect of the erratum is a system hang, although it may also

result in indeterminate code behavior which could cause data corruption.

**Workaround:** The I/O Trap SMI with I/O Restart feature should be disabled if STPCLK# throttling is used. For

applications where the I/O restart is not used, a dummy I/O instruction should follow the trapped I/O instruction to ensure that the I/O trap SMI handler will be called before the result of that handler is required. The system designer should review any I/O Trap SMI implementations for impact based on

their specific code execution sequence.

**Status:** There are currently no plans to fix this erratum.

17. ISA Verify followed by PCPCI DMA

**Problem:** The PIIX4E upon completion of an ISA Verify Mode cycle that reaches Terminal Count (TC), will not

transition an internal TC signal from the TC state to the Idle state.

**Implication:** In a PIIX4E system, if a PCPCI DMA cycle follows an ISA DMA Verify cycle that reaches terminal

count, with no other DMA, ISA Master or ISA Refresh cycles between them, the PIIX4E will assert the TC signal on the first data transfer of the PCPCI DMA cycle. This results in an incomplete data transfer.

Workaround: None.

**Status:** There are currently no plans to fix this erratum.

18. C3 Power State/BMIDE & Type-F DMA Livelock Errata

**Problem:** The PIIX4E does not always correctly reflect BMIDE and Type-F DMA activity on the BMSTS bit in

the Power Management Status Register (PMSTS) of PIIX4 Function 3.

**Implication:** The Operating System will think that it is safe to enter a C3 state and will then disable the arbiter and

then perform a PLVL3 register read to enter the C3 state, causing LIVELOCK to occur and resulting in a

system hang.

Workaround: In the OS power management code (ACPI.SYS) include a test of the BMIDE status register in code that

does the entry to C3. If a BMIDE transfer is in progress, do not enter C3. In the OS initialization code, mDISABLE Type-F DMA is BIOS indicates C3 support. If BIOS indicates that C3 is not supported,

leave Type-F DMA enabled.

**Status:** This will not be fixed in the PIIX4E. This will be incorporated into the PIIX4/PIIX4E datashet as a

change to the specification. This should be corrected for in ACPI aware operating systems. Contact your

Operating System vendor forn schedule and release information.

19. USB Dribble Errata

**Problem:** A USB receive packet with a bitstuff following then transmission of CRC, coupled with a dribble bit due

to prop delays through cables and HUBs may be incorrectly interpreted by the USB host controller state

machine as a poorly formed EOP.

**Implication:** The host controller response to this is a non acknowledge with a CRC/Timeout status communicated to

the software. If this condition persists the error count associated with this packet will be exceeded and an interrupt can be generated to software. This will stall the USB device. Current software reports a device error to the user via a pop up window. Another implication is that the installed base may have limited

USB expandablility via HUBs.

**Workaround:** There are two possible workarounds.

1. Hardware: Try plugging the USB device into a USB port closer to the root hub.

2. Software: Detect the CRC/Timeout error and count exceeded and attempt to requeue the packets while changing the length of the packets. Changing the length of the packets will change the CRC and thus potentially (likely) remove the combination of the two events causing the failure.

**Status:** This will not be fixed in the PIIX4E. This will be fixed in future implementations of the UHCI host controller.

20. ACPI Timer Errata

**Problem:** The power management timer may return improper result when read. Although the timer value settles

properly after incrementing, while incrementing there is a 3nS window every 69.8nS where the timer value is indeterminate (a 4.2% chance that the data will be incorrect when read). As a result, the ACPI

free running count up timer specification is violated due to erroneous reads.

Implication: System hangs due to the "inaccuracy" of the timer when used by software for time critical events and

delays.

**Workaround:** Read the register twice and compare.

**Status:** This will not be fixed in the PIIX4 or PIIX4E.

21. Daylight Savings Time Errata

**Problem:** If the last Sunday in October is the 30th or 31st, and the daylight savings enable bit in the PiiX4 is set,

the PiiX4 will not correctly adjust the time back one hour from 1:59:59 to 1:00:00am.

**Implication:** The system time may not be correct after the daylight savings time change. The first manifestation of this

will be on October 31st 1999.

Workaround: 1) If using Microsoft Windows 95/98 or Windows NT4.0 operating systems, leave the system on and the

operating system running at 1:59:59am on the last Sunday of October. Some operating systems will correctly detect the time change and correct the PIIX4's CMOS time settings. 2) After the daylight savings fallback occurs, change the time manually, using either an operating system date/time function, or the BIOS setup. 3) Contact your system provider to see if there is a BIOS update available that

corrects this condition.

**Status:** This will not be fixed in the PIIX4. It will be corrected in future chipset implementations.

# Specification Clarifications

# 1. CONFIG[1] Definition

Section 2.1.12 of the PIIX4 datasheet defines the CONFIG [1] signal. In addition to controlling the polarity of INIT and CPURST, this signal also controls the latching of NMI, SMI#, INTR, and INIT. In a Pentium® Processor based system (CONFIG[1]=0) NMI, SMI#, INTR, and INIT flow unlatched to the processor in all power managed states. In a Pentium® Pro Processor based system (CONFIG[1]=1) NMI, SMI#, INTR, and INIT will be latched when STPCLK# is asserted, and held for 5 PCICLKs after STPCLK# is deasserted.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

2.1.12 Other System and Test Signals

| Name      | Туре | Description  CONFIGURATION SELECT 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CONFIG[1] | I    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|           |      | This input signal is used to select the type of microprocessor is being used in the system. If CONFIG[1] = 0, the system contains a Pentium microprocessor. If CONFIG[1] = 1, the system contains a Pentium Pro microprocessor. CONFIG[1] is used to control the polarity of the INIT and CPURST signals and the latching of NMI, SMI#, INTR, and INIT. If CONFIG[1]=1, INIT# and CPURST# are active low and NMI, SMI#, INTR, INIT# flow unlatched to the processor. If CONFIG[1]=0, INIT and CPURST and active high and NMI, SMI#, INTR, and INIT will be latched when STPCLK# is asserted, and held for 5 PCICLKs after STPCLK# is deasserted. |  |

# 2. SUSA#, SUSB# and SUSC# State Transition during RESET

After a hard reset (a write to CF9h bit 2, with bit 1 set to 1) SUSA#, SUSB#, SUSC# immediately transition low for three to four RTC clocks.

In many system designs, these signals control the various power planes. If the assertion of these signals do not affect the state of PWROK from the power supply circuitry, the hard reset completes normally with a system reboot. If the assertion of these signals cause the power supply circuitry to deassert PWROK, the PIIX4 will reset and power-up the system like it was performing a cold boot. In both cases the system reboots.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

# 3. IRQ8# Routing

The RTC interrupt is connected to ISA IRQ8#, and is internally routed within the PIIX4. If the internal RTC is enabled (bit 0 of the RTCCFG is set ), the PIIX4's IRQ8# pin should be programmed as a general-purpose input, GPI[6] (by setting bit 14 of the PIIX4's General Configuration Register). However, if an external APIC is used, the PIIX4's IRQ8# becomes an output and must not be programmed as a general-purpose input. The table below summarizes the PIIX4's IRQ8# pin configuration depending on different usage of the RTC and APIC.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

IRQ8# configuration with different scenarios

| t don domigaration than amorotic domains |              |               |                                        |  |  |

|------------------------------------------|--------------|---------------|----------------------------------------|--|--|

| Internal RTC                             | External RTS | External APIC | PIIX4's IRQ Should be<br>Selected as * |  |  |

| Used                                     | Not used     | Not used      | GPI[6] (input)                         |  |  |

| Used                                     | Not used     | Used          | IRQ8# (output)                         |  |  |

| Not used                                 | Used         | Not used      | IRQ8# (input)                          |  |  |

| Not used                                 | Used         | Used          | IRQ8# (input)                          |  |  |

<sup>\*</sup> Bit 14 of the PIIX4's GENCFG register will determine the configuration of PIIX4's IRQ8# pin.

# 4. IRQ9 Routing

SCI interrupts, SMBus interrupts and PIRQs can be routed to IRQ9. Any time an SCI, SMB or PIRQ is programmed to use the internal 8259's IRQ9, the PIIX4 will ignore the ISA IRQ9 and the interrupts will behave like level triggered interrupts. The table below describes the implications of the different routing options.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

| SCI<br>Interrupt | SMBus<br>Interrupt | PIRQ | ISA IRQ9                                | Result                                      |  |

|------------------|--------------------|------|-----------------------------------------|---------------------------------------------|--|

| 0                | 0                  | 0    | 0                                       | No Interrupt                                |  |

| 0                | 0                  | 0    | 1                                       | ISA IRQ9 used (edge or level)               |  |

| 0                | 0                  | 1    | Х                                       | ISA IRQ lost, level mode only, non-shared   |  |

| 0                | 1                  | 0    | Х                                       | X ISA IRQ lost, level mode only, non-shared |  |

| 0                | 1                  | 1    | X ISA IRQ lost, level mode only, shared |                                             |  |

| 1                | 0                  | 0    | Х                                       | ISA IRQ lost, level mode only, non-shared   |  |

| 1                | 0                  | 1    | Х                                       | ISA IRQ lost, level mode only, shared       |  |

| 1                | 1                  | 0    | X ISA IRQ lost, level mode only, shared |                                             |  |

| 1                | 1                  | 1    | X ISA IRQ lost, level mode only, shared |                                             |  |

**NOTE:** 0 = IRQ9 not used by that function

1 = IRQ9 used by that function

non-shared = IRQ9 not shared internally between functions

shared = IRQ9 shared internally between functions

# 5. SERIRQ Sampling Phase

When referring to the state of the SERIRQ signal the verbiage in section 8.7.1 of the datasheet uses the words active and low interchangeably as well as the words inactive and high. This text has been changed to only use the words low and high when referring to the state of the SERIRQ signal. The PIIX4's 8259 logic determines if the corresponding interrupt on the SERIRQ signal is active or inactive.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

#### 8.7.1 Protocol

Serial interrupt information is transferred using three types of frames: a Start Frame, one or more IRQ Data frames, and one Stop frame. There are also two modes of operation: Quiet Mode and Continuous Mode.

Quiet (Active) Mode

To indicate an interrupt, the peripheral brings the SERIRQ signal low for one clock, and then tri-states the signal. This brings all the state machines from IDLE to the ACTIVE states.

PIIX4 then takes control of the SERIRQ signal by driving it low on the next clock, and continues driving it low for 3–7 clocks more (programmable). Thus, the total number of clocks low will be 4–8. After those clocks, PIIX4 drives SERIRQ high for one clock and then tri-state the signal.

#### Continuous (Idle) Mode

In this mode, PIIX4 initiates the START frame, rather than the peripherals. Typically, this is done to update IRQ status (acknowledges). PIIX4 drives SERIRQ low for 4–8 clocks. This is the default mode after reset, and can be used to enter the Quiet mode.

#### **Data Frame**

Once the Start frame has been initiated, all of the serial interrupt peripherals must start counting frames based on the rising edge of SERIRQ. Each of the IRQ/DATA frames has exactly 3 phases of 1 clock each: a Sample phase, a Recovery Phase, and a Turn-around phase.

During the Sample phase, the device drives SERIRQ low if the state of the corresponding interrupt is low. If the state of the corresponding interrupt is high the devices should not drive the SERIRQ signal. It will remain high due to pull-up resistors. The PIIX4's 8259 logic determines if the logic level on the SERIRQ signal is active or inactive.

During the other two phases (Turn around and Recovery), no device should drive the SERIRQ signal. The IRQ/DATA frames have a specific order and usage, as shown in Table 26.

If an SMI# is activated on frame 3, PIIX4 drives its EXTSMI# signal active. This then generates an SMI# to the microprocessor, if enabled.

# 6. RI# Pulse Width Requirement

Section 11.4.2 of the PIIX4 datasheet specifies a 2 RTC pulse width requirement for GPI1, IRQ[15:9,7:3,1], and USB resume events. This list should also include RI#.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

"The GPI1, EXTSMI#, IRQ[15:9,7:3,1], and USB resume events must be active for a minimum of 64 µs (approximately 2 TC clock periods) for the resume to be recognized."

# 7. Diode Requirement for Vref Sequencing Circuit

Figure 2, in section 2.3, of the PIIX4 datasheet provides an example Vref Sequencing Circuit. Included in this circuit is a diode. The datasheet does not explicitly state that this diode should be a Schottky diode.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

#### 8. SMI# Generation from APMC Write

In order to generate an SMI# by reading from the APMC Register it is necessary to enable both the APMC\_EN bit as well as the IOSE bit. The datasheet section 4.2.6.1, 7.1.3, and 7.1.16 does not state that it is necessary to set the IOSE bit.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

#### 4.2.6.1 APMC—Advanced Power Management Control Port (IO)

I/O Address: 0B2h Default Value: 00h

Attribute: Read/Write

This register passes data (APM Commands) between the OS and the SMI handler. In addition, writes can generate an SMI. PIIX4 operation is not effected by the data in this register.

| Bit | Description                                                                                                                                                                                                                                                                                                            |  |  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|     | APM Control Port (APMC). Writes to this register store data in the APMC Register and reads return the last data written. In addition, writes generate an SMI, if the APMC_EN bit (PCI function 3, offset 58h, bit 25) and the IOSE bit (PCI function 3, offset 04h, bit 0) are set to 1. Reads do not generate an SMI. |  |  |

#### 7.1.3 PCICMD—PCI COMMAND REGISTER (FUNCTION 3)

Address Offset: 04–05h

Default Value: 00h

Attribute: Read/Write

This register controls access to the I/O space registers

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0   | I/O Space Enable (IOSE). 1=Enable. 0=Disable. This bit controls the access to the SMBus I/O space registers whose base address is described in the SMBus Base Address register. If this bit is set, access to the SMBus IO registers is enabled. The base register for the I/O registers must be programmed before this bit is set. When disabled, all IO accesses associated with SMBus Base Address are disabled. This bit must be set to enable SMI# generation from a write to the APMC register. This bit functions independent of the state of Function 3 Power Management IO Space Enable (PMIOSE) bit (PMREGMISC register, bit 0). |  |  |  |

# 7.1.16 DEVACTB—DEVICE ACTIVITY B (FUNCTION 3)

Address Offset: 58–5Bh Default Value: 00h

Attribute: Read/Write

This register contains the Clock Event and Global Timer Reload enables for IRQs, PCI access, PME events, Video.

| Bit | Description                                                                                                                             |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

|     | <b>APMC Enable (APMC_EN)</b> — <b>R/W.</b> 1=Enable generation of SMI# when APMC register is written to and SMI# is enabled. 0=Disable. |  |  |

# 9. Power Button Override

Section 7.2.1 of the PIIX4 datasheet defines the Power Button Override Status. When the PWRBTN# signal has been continuously asserted for greater than 4 seconds, the PIIX4 automatically transitions the system into the soft off state and clears the PWRBTN\_STS bit. However, if the status bit of any resume event is set at the time of an override, the PIIX4 will transition to the soft off state and immediately resume. If PWROK is deasserted, the power button override logic will not function.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

#### 7.2.1 PMSTS—POWER MANAGEMENT STATUS REGISTER (IO)

I/O Address: Base + (00h)

Default Value: 00h

Attribute: Read/Write

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | Power Button Override Status(PWRBTNOR_STS)—R/WC. 1=Power Button Override has been signaled. 0=Power Button Override has not been signaled. This bit is set when Power Button Override has been enabled and the PWRBTN# signal has been continuously asserted for greater than 4 seconds. PIIX4 automatically transitions the system into the soft off state and clears the PWRBTN_STS bit. If the status bit of any resume event is set at the time of a power button override, the PIIX4 will transition to the soft off state and immediately resume. If PWROK is deasserted, the Power Button Override logic will not function. This bit is only set by hardware and can only be reset by writing a one to this bit position. |

#### 10. RTC Status Bit Clarification

Section 7.2.1 of the PIIX4 datasheet defines the RTC status bit. The RTC\_EN bit in the PMEN register (base + 02h, bit 10) gates the setting of the RTC\_STS bit. RTC\_EN must be set in order to set the RTC\_STS bit upon an RTC alarm.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

# 7.2.1 PMSTS—POWER MANAGEMENT STATUS REGISTER (IO)

I/O Address: Base + (00h)

Default Value: 00h

**Attribute:** Read/Write

| Bit | Description                                                                                                                                                                                                                                                                         |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 10  | RTC Status (RTC_STS)—R/WC. 1=RTC alarm has been signaled. 0=RTC alarm has not been signaled. This bit is set when the internal RTC asserts its IRQ8 signal and the RTC_EN bit is set. This bit is only set by hardware and can only be reset by writing a one to this bit position. |  |

# 11. SCI\_EN Bit Clarification

Section 7.2.3 of the PIIX4 datasheet defines the SCI enable bit. The SCI\_EN bit in the PMCNTRL register enables the generation of SCI from 4 sources; PWRBTN#, LID, THRM#, and GPI1#. If this bit is enabled and the individual enable bits from these sources are set (PWRBTN\_EN, LID\_EN, THRM\_EN, and GPI\_EN), an SCI is generated. If this bit is disabled and the individual enable bits from these sources are set, an SMI# is generated. Note that there are two sources of SCI (BIOS\_RLS, TMROF\_STS) that are not controlled by this register. To disable SCI from these sources, their respective enable bits (GBL\_EN, TMROF\_EN) must be disabled.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

#### 7.2.3 PMCNTRL—POWER MANAGEMENT CONTROL REGISTER (IO)

$\begin{tabular}{ll} I/O \ Address: & Base + (04h) \\ Default \ Value: & 0000h \\ Attribute: & Read/Write \\ \end{tabular}$

| Bit | Description                                                                                                                                                                                                                                       |  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0   | <b>SCI Enable(SCI_EN)—R/W.</b> 1=Enable generation of SCI upon setting of PWRBTN_STS, LID_STS, THRM_STS, or GPI_STS bits. 0=Disable. Note that this register does not disable SCI generation from the Power Management Timer or BIOS Release bit. |  |  |

# 12. Thermal Override Initiates Throttling Even in Clock Control State

If THRM# is asserted for more than 2 seconds while the PIIX4 is in a Stop Grant state, the PIIX4 will still initiate STPCLK# throttling. Once THRM# is deasserted the PIIX4 will return to the clock control state.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

# 13. No Disabling Burst Events During A Burst

Burst events cause the reload of a Burst timer, which begins to count down from its loaded value. While the timer is counting, the system returns to full clock operation. Once the burst timer expires, the system automatically returns to the clock controlled state. PIIX4 provides 2 different burst timers, a fast burst timer (which generates a short count) and a slow burst timer (which generates a longer count). If burst events are disabled during a burst, the PIIX4 will enter the clock controlled state after the burst timer expires and will not be able to break out.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

# 14. Unrouting a PIRQ

Section 8.6.8, Interrupt Steering of the PiiX4 datasheet states how to route a PIRQx# to a IRQx, but does not state a suggested procedure for unrouting. The paragraph below will be added at the end of this section.

Before unrouting a PIRQx# from an IRQx, ensure that the mask is enabled for that IRQ and that the corresponding ELCR is set back to edge mode. When the IRQx is unmasked an interrupt will likely be generated which should be treated as any other spurious interrupt.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

#### 15. IDE Device Detection

Values read from an unpopulated, floating IDE port are indeterminate. To avoid falsely detecting a busy drive, OEMs should follow the platform design recommendations for detecting an IDE device.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

# 16. Physical Region Descriptor Alignment

Section 9.4, The Physical Region Descriptor Format inaccurately specifies that the Descriptor Table (DT) must be aligned on a 64-Kbyte boundary.

The Physical Region Descriptor Table must be aligned on a Dword boundary. However, the DT must never cross a 64Kbyte boundary. For the case where a 64 Kbyte DT is required, then it must be aligned on a 64 Kbyte boundary.

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

# 17. RTC Index Register Read

Section 6.1.14 does not clearly document the steps for reading the RTC Index Register. The following algorithm should be followed before reading the RTC Index Register:

- 1. Disable Alternate Access mode (funct 0, B0h, bit 5)

- 2. Set the RTC Index Read Enable bit (RTCIREN)

- 3. Read the RTC Index register (70h) (bits [6:0] provide RTC Index value, bit 7 is indeterminate)

- 4. Disable the RTC Index Read Enable bit

- 5. Enable Alternate Access mode

- 6. Read the RTC Index register (bit 7 is the NMI enable bit, bits [6:0] are indeterminate)

- 7. Disable Alternate Access mode (funct 0, B0h, bit 5)

This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

# 18. **GPI[1] Minimum Assertion**

Section 7.2.5 does not clearly document the required behavior for GPI\_STS. The following description will be added to the description for GPSTS[9] (GPI\_STS). GPI[1]# must be asserted for a minimum of 2 PCI Clocks during runtime, or 2 RTC Clocks during suspend for GPI\_STS to be set.

#### 19. RSMRST# Behavior

The PIIX4 Datasheet, section 2.1.10 identifies the signal description of the Power Management Signals. The following should be added to the description of RSMRST#.

It will reset the SM Bus Host and Slave controllers in the suspend well and will assert SUS[A:C]#. The assertion of SUS[A-C]# will generally initiate the deassertion of PWROK. RSMRST# assertion will then generally reset the entire system.

# 20. SMBus Busy Bit Behavior

30

In a polling environment, when reading the SMBus Host Status Register, the Host BUSY bit may appear to indicate a premature transaction completion. Though the Host BUSY bit accurately tracks the SMBus activity, there can be some delay between setting the start bit within the SMBus Controller and the transaction actually starting. Immediate polling of the Host Status Register BUSY bit may indicate that the SMBus is NOT busy, but the reason is because it hasn't started yet. Therefore, the suggested usage model for non-BIOS implementations should be to use an interrupt or SMI to indicate when the transaction is complete. The interrupt is guaranteed to follow the completion of the transaction because the interrupt is an "AND" with the Interrupt Enable Bit and the Host Status Bit. This clarification applies to all steppings of the PIIX4 and will be incorporated into the next revision of the PIIX4 datasheet.

To clarify this behavior, the following changes to the PIIX4 datasheet are required:

In the PIIX4 datasheet, Page 148, Section 7.3.1. SMBHSTSTS - SMBUS HOST STATUS REGISTER, Bit 1 and Bit 0 should be changed to read:

# 7.3.1 SMBHSTSTS—SMBUS HOST STATUS REGISTER (IO)

I/O Address: Base + (00h)

Default Value: 00h

**Attribute:** Read/Write

This register provides status information concerning the SMBus controller host interface.

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7:5 | Reserved.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |