# SDRAM Serial Presence Detect (SPD) Data Structure (168- and SO-144 DIMM)

**Intel Specification**

**REVISION 1.2**

Nov, 1997 1 of 27 Revision 1.2

THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE.

No other license, express or implied, by estoppel or otherwise, to any other intellectual property rights is granted herein.

Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to implementation of information in this specification. Intel does not warrant or represent that such implementation(s) will not infringe such rights.

I2C is a two-wire communications bus/protocol developed by Philips. Implementations of the I2C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

\* Other brands and names are the property of their respective owners.

Copyright Intel Corporation, 1996

Nov, 1997 2 of 27 Revision 1.2

# **Changes:**

#### Revision 1.2 adds:

Bytes 126, 127: Additional Information for "backward compatibility"

Bytes 93-94: Manufacturing Date Code Bytes 30-33: Additional Timing Information

Byte 5: Changed the nomenclature from Bank to Row on the DIMM to remove

confusion of Rows vs. Banks on a DIMM

#### Revision 1.1 adds comments to clarify several Bytes:

Bytes 3-4: Note added to clarify address row/column 1/16 rollup useage. Bytes 5,17: Note added to clarify Module, SDRAM Device bank useage.

Bytes 23-26: Note added to clarify timing1/16ns rollup useage.

Nov, 1997 3 of 27 Revision 1.2

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                    |                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| CHANGE HISTORY                                                                                                                                                                                                                                                                       | 3                               |

| LIST OF TABLES                                                                                                                                                                                                                                                                       | 4                               |

| LIST OF FIGURES                                                                                                                                                                                                                                                                      | 4                               |

| 1.0 INTRODUCTION                                                                                                                                                                                                                                                                     | 5                               |

| 2.0 SDRAM MODULE PERFORMANCE GRADES                                                                                                                                                                                                                                                  | 5                               |

| 3.0 EEPROM COMPONENT SPECIFICATIONS                                                                                                                                                                                                                                                  | 6                               |

| 4.0 SERIAL PRESENCE DETECT EEPROM DATA                                                                                                                                                                                                                                               | 11                              |

|                                                                                                                                                                                                                                                                                      |                                 |

|                                                                                                                                                                                                                                                                                      |                                 |

| LIST OF TABLES                                                                                                                                                                                                                                                                       |                                 |

| TABLE 1: EEPROM COMPONENT A.C. TIMING PARAMETERS TABLE 2: SERIAL PRESENCE DETECT DATA FORMAT                                                                                                                                                                                         | 8<br>13                         |

| LIST OF FIGURES                                                                                                                                                                                                                                                                      |                                 |

| FIGURE 1: EEPROM COMPONENT A.C. TIMING PARAMETERS FIGURE 2: EEPROM DATA VALIDITY FIGURE 3: EEPROM START AND STOP CONDITIONS FIGURE 4: EEPROM ACKNOWLEDGE FIGURE 5: EEPROM BYTE WRITE OPERATION FIGURE 6: EEPROM PAGE WRITE OPERATION FIGURE 7: EEPROM CURRENT ADDRESS READ OPERATION | 9<br>10<br>10<br>10<br>11<br>11 |

| FIGURE 8: EEPROM RANDOM READ OPERATION FIGURE 9: EEPROM SEQUENTIAL READ OPERATION                                                                                                                                                                                                    | 11<br>11<br>12                  |

#### 1.0 Introduction

This specification defines the Serial Presence Detect (SPD) electrical and Data Structure requirements for Synchronous DRAM Dual In-Line Memory Modules (SDRAM DIMMs) and Small-outline Memory Modules (SO-DIMM). These SDRAM DIMMs are intended for use as main memory installed on personal computer, **work-station, and/or server** motherboards.

This specification largely follows the JEDEC defined 168-pin and SO-144 SDRAM DIMM SPD specs as of July 1996. *Changes in process are currently shown in italics.*

#### 2.0 SDRAM Module Performance Grades

Three performance grades are defined in the SPD matrix:

CAS Latency x highest latency, lowest performance

CAS Latency x-1 2nd highest latency

CAS Latency x-2 3rd highest latency, highest performance (may restrict freq)

This is a relative series of three latencies, CL x being the most commonly available at this speed grade.

The performance grade of the module is determined by the read data access time (Tac), and RAS cycle time (Trc) supported by the SDRAM components.

Latency numbers in the sequence will depend on the speeds which are supported by the module.

Nov, 1997 5 of 27 Revision 1.2

# 3.0 EEPROM Component Specifications

The Serial Presence Detect function is implemented using a 2048 bit EEPROM component. This nonvolatile storage device contains data programmed by the DIMM manufacturer that identifies the module type and various SDRAM organization and timing parameters. System read/write operations to the EEPROM device occur via a standard I<sup>2</sup>C bus using the DIMM's SCL (clock) and SDA (data) signals, together with SA(2:0) which provide the EEPROM Device Address. If the EEPROM device has a Write Protect input pin, it must be tied in the non-write protect state on the DIMM PCB. The EEPROM device selected by the DIMM manufacturer must use the SA(2:0) device address signals. The EEPROM must operate with a V<sub>CC</sub> of 3.0 Vdc to 3.6 Vdc.

**Table 1: EEPROM Component Absolute Maximum Ratings**

| Parameter                         | Range             |

|-----------------------------------|-------------------|

| All Input or Output Voltages with | +4.6V to -0.3V    |

| Respect to Ground                 |                   |

| Ambient Storage Temperature       | -40 °C to +100 °C |

**Table2: EEPROM Component Operating Conditions**

| Parameter                     | Range            |

|-------------------------------|------------------|

| Ambient Operating Temperature | 0 °C to $+70$ °C |

| Positive Power Supply         | 3.0V to 3.6V     |

Table 3: EEPROM Component A.C. and D.C. Characteristics

| Symbol            | Parameter                   | Test Conditions                    | Min                   | Max                   | Units |

|-------------------|-----------------------------|------------------------------------|-----------------------|-----------------------|-------|

| $I_{CCA}$         | Active Power Supply Current | $f_{SCL} = 100 \text{ kHz}$        |                       | 5.0                   | mA    |

| $I_{SB}$          | Standby Current             | $V_{IN} = GND \text{ or } V_{CC}$  |                       | 100                   | uA    |

| $I_{LI}$          | Input Leakage Current       | $V_{IN} = GND \text{ or } V_{CC}$  |                       | 10                    | uA    |

| $I_{LO}$          | Output Leakage Current      | $V_{OUT} = GND \text{ to } V_{CC}$ |                       | 10                    | uA    |

| $V_{ m IL}$       | Input Low Voltage           |                                    | -0.3                  | V <sub>CC</sub> X 0.3 | V     |

| $V_{\mathrm{IH}}$ | Input High Voltage          |                                    | V <sub>CC</sub> X 0.7 |                       | V     |

| $V_{OL}$          | Output Low Voltage          | $I_{OL} = 3.0 \text{ mA}$          |                       | 0.4                   | V     |

Nov, 1997 6 of 27 Revision 1.2

| Parameter                          | Min                                                                                                                                                                                                                                                                                                                                                                                                                  | Max                                                                                                                                                                                                                                                                                                                                                                                                                       | Units                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL Clock Frequency                |                                                                                                                                                                                                                                                                                                                                                                                                                      | 80                                                                                                                                                                                                                                                                                                                                                                                                                        | kHz                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Noise Supression Time Constant at  |                                                                                                                                                                                                                                                                                                                                                                                                                      | 100                                                                                                                                                                                                                                                                                                                                                                                                                       | ns                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SCL, SDA inputs                    |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SCL Low to SDA Data Out Valid      | 0.3                                                                                                                                                                                                                                                                                                                                                                                                                  | 7.0                                                                                                                                                                                                                                                                                                                                                                                                                       | us                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Time the Bus Must Be Free before a | 6.7                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                           | us                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| New Transmission Can Start         |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Start Condition Hold Time          | 4.5                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                           | us                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Clock Low Time                     | 6.7                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                           | us                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Clock High Time                    | 4.5                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                           | us                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Start Condition Setup Time         | 6.7                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                           | us                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| (for a Repeated Start Condition)   |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Data In Hold Time                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                           | us                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Data In Setup Time                 | 500                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                         | ns                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SDA and SCL Rise Time              |                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                         | us                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SDA and SCL Fall Time              |                                                                                                                                                                                                                                                                                                                                                                                                                      | 300                                                                                                                                                                                                                                                                                                                                                                                                                       | ns                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Stop Condition Setup Time          | 6.7                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                           | us                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Data Out Hold Time                 | 300                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Write Cycle Time                   |                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                        | ms                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                    | SCL Clock Frequency Noise Supression Time Constant at SCL, SDA inputs SCL Low to SDA Data Out Valid Time the Bus Must Be Free before a New Transmission Can Start Start Condition Hold Time Clock Low Time Clock High Time Start Condition Setup Time (for a Repeated Start Condition) Data In Hold Time Data In Setup Time SDA and SCL Rise Time SDA and SCL Fall Time Stop Condition Setup Time Data Out Hold Time | SCL Clock Frequency Noise Supression Time Constant at SCL, SDA inputs  SCL Low to SDA Data Out Valid 0.3 Time the Bus Must Be Free before a New Transmission Can Start Start Condition Hold Time 4.5 Clock Low Time 6.7 Clock High Time 4.5 Start Condition Setup Time (for a Repeated Start Condition) Data In Hold Time 0 Data In Setup Time SDA and SCL Rise Time Stop Condition Setup Time 6.7 Data Out Hold Time 300 | SCL Clock Frequency Noise Supression Time Constant at SCL, SDA inputs SCL Low to SDA Data Out Valid O.3 Time the Bus Must Be Free before a New Transmission Can Start Start Condition Hold Time Clock Low Time Clock High Time 4.5 Start Condition Setup Time (for a Repeated Start Condition) Data In Hold Time  Data In Setup Time SDA and SCL Rise Time SDA and SCL Fall Time Stop Condition Setup Time 6.7 Data Out Hold Time 300 |

**Note**: The write cycle time ( $t_{WR}$ ) is the time from a valid stop condition of a write sequence to the end of the EEPROM internal erase/program cycle. During the write cycle, the EEPROM bus interface circuits are disabled, SDA remains high due to pull-up resistor, and the EEPROM does not respond to its slave address.

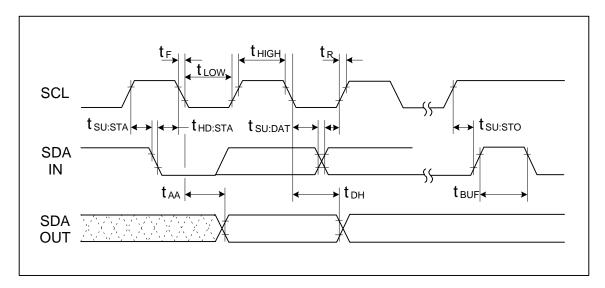

Figure 2: EEPROM Component A.C. Timing Parameters

Nov, 1997 7 of 27 Revision 1.2

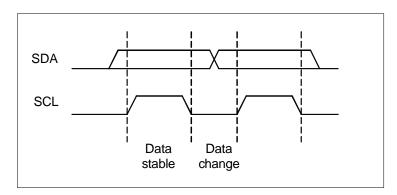

Figure 3: EEPROM Data Validity

Figure 4: EEPROM Start and Stop conditions

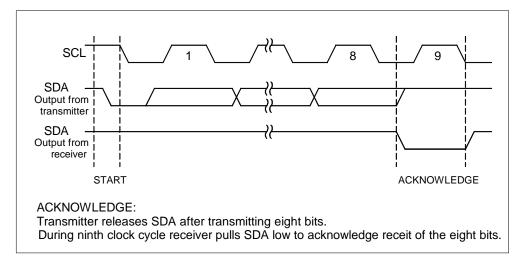

Figure 5: EEPROM Acknowledge

Nov, 1997 8 of 27 Revision 1.2

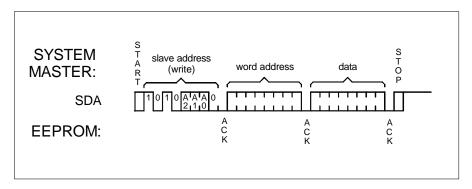

Figure 6: EEPROM Byte Write Operation

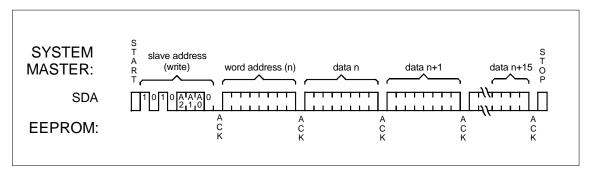

Figure 7: EEPROM Page Write Operation

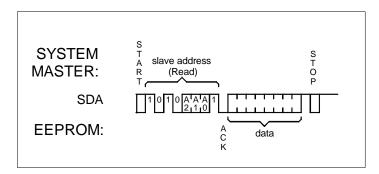

Figure 8: EEPROM Current Address Read Operation

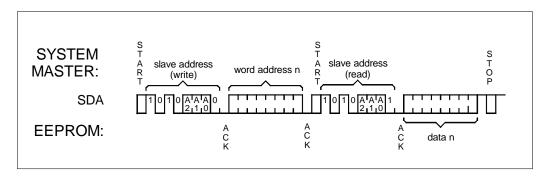

Figure 9: EEPROM Random Read Operation

Nov, 1997 9 of 27 Revision 1.2

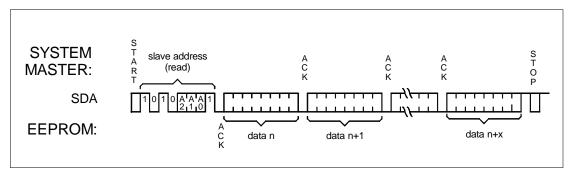

Figure 10: EEPROM Sequential Read Operation

Nov, 1997 10 of 27 Revision 1.2

# 4.0 Serial Presence Detect EEPROM Data

**Table 5: Serial Presence Detect Data Format**

| Byte Number | Function                                                             | Required/<br>Optional |

|-------------|----------------------------------------------------------------------|-----------------------|

| 0           | Defines # of bytes written into serial memory at module manufacturer | Required              |

| 1           | Total # of bytes of SPD memory device                                | Required              |

| 2           | Fundamental memory type (FPM, EDO, SDRAM) from Appendix A            | Required              |

| 3           | # of row addresses on this assembly (includes Mixed-size Row addr)   | Required              |

| 4           | # Column Addresses on this assembly (includes Mixed-size Col addr)   | Required              |

| 5           | # Module Rows on this assembly                                       | Required              |

| 6           | Data Width of this assembly                                          | Required              |

| 7           | Data Width continuation                                              | Required              |

| 8           | Voltage interface standard of this assembly                          | Required              |

| 9           | SDRAM Cycle time, <i>CL=X</i> (highest CAS latency)                  | Required              |

| 10          | SDRAM Access from Clock (highest CAS latency)                        | Required              |

| 11          | DIMM Configuration type (non-parity, ECC)                            | Required              |

| 12          | Refresh Rate/Type                                                    | Required              |

| 13          | Primary SDRAM Width                                                  | Required              |

| 14          | Error Checking SDRAM width                                           | Required              |

| 15          | Minimum Clock Delay Back to Back Random Column Address               | Required*             |

| 16          | Burst Lengths Supported                                              | Required*             |

| 17          | # of Banks on Each SDRAM Device                                      | Required*             |

| 18          | CAS# Latencies Supported                                             | Required*             |

| 19          | CS# Latency                                                          | Required*             |

| 20          | Write Latency SDRAM Module Attributes                                | Required*             |

| 21          | SDRAM Device Attributes: General                                     | Required*             |

| 22<br>23    | Min SDRAM Cycle time at <b>CL X-1</b> (2nd highest CAS latency)      | Required*             |

| 24          | SDRAM Access from Clock at <b>CL X-1</b> (2nd highest CAS latency)   | Required*             |

| 25          | Min SDRAM Cycle time at CL X-2 (3rd highest CAS latency)             | Optional*             |

| 26          | Max SDRAM Access from Clock at CL X-2 (3nd highest CAS latency)      | Optional*             |

| 27          | Min Row Precharge Time (Trp)                                         | Required*             |

| 28          | Min Row Active to Row Active (Trrd)                                  | Required*             |

| 29          | Min RAS to CAS Delay (Trcd)                                          | Required*             |

| 30          | Minimum RAS Pulse Width (Tras)                                       | Required*             |

| 31          | Density of each row on module (mixed, non-mixed sizes)               | Required              |

| 32-61       | Superset Information (may be used in future)                         |                       |

| 62          | SPD Data Revision Code                                               | Required              |

| 63          | Checksum for bytes 0-62                                              | Required              |

| 64-71       | Manufacturer's JEDEC ID code per JEP-108E                            | Optional              |

| 72          | Manufacturing Location                                               | Optional              |

| 73-90       | Manufacturer's Part Number                                           | Optional              |

| 91-92       | Revision Code                                                        | Optional              |

| 93-94       | Manufacturing Date                                                   | Optional              |

| 95-98       | Assembly Serial Number                                               | Optional              |

| 99-125      | Manufacturer Specific Data                                           | Optional              |

| 126         | Intel specification frequency                                        | Required              |

| 127         | Intel Specification CAS# Latency support                             | Required              |

| 128+        | Unused storage locations                                             |                       |

Notes: Required/Optional\* (bold\*) are SDRAM only bytes

Nov, 1997 11 of 27 Revision 1.2

#### Byte 0 - Number of Bytes used by Module Manufacturer (General)

This field describes the total number of bytes used by the module manufacturer for the SPD data and any (optional) specific supplier information. The byte count includes the fields for all required and optional data.

| Number of bytes | Hex Value |

|-----------------|-----------|

| Undefined       | 00        |

| 1               | 01        |

| 2               | 02        |

| 3               | 03        |

|                 |           |

| 128             | 80        |

|                 |           |

| 254             | FE        |

| 255             | FF        |

#### **Byte 1 - Total SPD Memory Size (General)**

This field describes the total size of the serial memory used to hold the Serial Presence Detect data.

| Serial Memory Size | Hex Value |

|--------------------|-----------|

| RFU                | 00        |

| 2 Bytes            | 01        |

| 4 Bytes            | 02        |

| 8 Bytes            | 03        |

| 16 Bytes           | 04        |

| 32 Bytes           | 05        |

| 64 Bytes           | 06        |

| 128 Bytes          | 07        |

| 256 Bytes          | 08        |

| 512 Bytes          | 09        |

| 1024 Bytes         | 0A        |

| 2048 Bytes         | 0B        |

| 4096 Bytes         | 0C        |

| 8192 Bytes         | 0D        |

#### **Byte 2 - Memory Type (General)**

This field describes the fundamental memory type implemented on the module.

| Memory Type | Hex Value |

|-------------|-----------|

| EDO         | 02        |

| SDRAM       | 04        |

|             |           |

**Note for Bytes 3-4:** Bytes 3-4 show a roll-up value for Hex 1, 2, 3 (i.e., 1row/16rows). For SDRAM devices over duration of REV 1 in Byte 62 (SPD Jedec Rev level), values of 1-3rows/cols are not expected, and Hex equivalent is 16-18rows/columns. Jedec Byte 62 would change rev level if values of 1-3 row/col become available.

Nov, 1997 12 of 27 Revision 1.2

#### Byte 3 - Number of Row Address Bits (SDRAM specific)

This field describes the number of row address bits in the SDRAM array. Note: the number of row address bits does not include the bank selects (BA0, BA1). If the module has only one bank OR if the module has two banks of the same size and organization, then bits 3:0 describe the number of row address bits, and bits 7:4 are 0. If the module has two banks with different size/organization, then bits 3:0 describe the row addressing for bank 1 and bits 7:4 decribe the row addressing for bank 2.

| Number of Row Addr bits | Bits 3:0 Hex Value |

|-------------------------|--------------------|

| Undefined               | 0                  |

| 1/16                    | 1                  |

| 2/17                    | 2                  |

|                         |                    |

| 7                       | 7                  |

| 8                       | 8                  |

| 9                       | 9                  |

| 10                      | Α                  |

| 11                      | В                  |

|                         | •                  |

| 14                      | ш                  |

| 15                      | F                  |

| Number of Row Addr bits | Bits 7:4 Hex Value |

|-------------------------|--------------------|

| Undefined               | 0                  |

| 1/16                    | 1                  |

| 2/17                    | 2                  |

|                         |                    |

| 7                       | 7                  |

| 8                       | 8                  |

| 9                       | 9                  |

| 10                      | Α                  |

| 11                      | В                  |

|                         |                    |

| 14                      | E                  |

| 15                      | F                  |

#### BYTE 4 - Number of Column Address Bits (SDRAM specific)

This field describes the number of column address bits in the SDRAM array. Note: the number of column address bits does not include the bank selects (BA0, BA1), or the AutoPrecharge bit. If the module has only one bank OR if the module has two banks of the same size and organization, then bits 3:0 describe the number of column address bits, and bits 7:4 are 0. If the module has two banks with different size/organization, then bits 3:0 describe the column addressing for bank 1 and bits 7:4 decribe the column addressing for bank 2.

| Number of Col Addr bits | Bits 3:0 Hex Value |

|-------------------------|--------------------|

| Undefined               | 0                  |

| 1/16                    | 1                  |

| 2/17                    | 2                  |

|                         |                    |

| 7                       | 7                  |

| 8                       | 8                  |

| 9                       | 9                  |

| 10                      | Α                  |

| 11                      | В                  |

| 12                      | С                  |

| 13                      | D                  |

| 14                      | Е                  |

| 15                      | F                  |

| Number of Col Addr bits | Bits 7:4 Hex Value |

|-------------------------|--------------------|

| Undefined               | 0                  |

| 1/16                    | 1                  |

| 2/17                    | 2                  |

|                         |                    |

| 7                       | 7                  |

| 8                       | 8                  |

| 9                       | 9                  |

| 10                      | А                  |

| 11                      | В                  |

| 12                      | С                  |

| 13                      | D                  |

| 14                      | E                  |

| 15                      | F                  |

#### **BYTE 5 - Number of Module Rows**

This field describes the number of rows of SDRAM components on the module. Byte 17 applies to SDRAM device banks (a module with 2 rows could have devices with 2-16 internal banks).

| Number of Banks | Hex Value |

|-----------------|-----------|

| Undefined       | 00        |

| 1               | 01        |

| 2               | 02        |

| 3               | 03        |

|                 |           |

| 254             | FE        |

| 255             | FF        |

#### **BYTES 6 & 7 - Module Data Width**

This field describes the data width on the SDRAM module. Bit 0 of byte 6 is the LSB and Bit 7 of byte 7 is the MSB.

| Module Data Width | Byte 7 (Hex) | Byte 6 (Hex) |

|-------------------|--------------|--------------|

| Undefined         | 00           | 00           |

| 1                 | 00           | 01           |

| 2                 | 00           | 02           |

| 3                 | 00           | 03           |

|                   |              |              |

| 32                | 00           | 20           |

|                   |              |              |

| 36                | 00           | 24           |

|                   |              |              |

| 64                | 00           | 40           |

|                   |              |              |

| 72                | 00           | 48           |

|                   |              |              |

| 80                | 00           | 50           |

| ·                 |              |              |

| 128               | 00           | 80           |

|                   |              |              |

| 144               | 00           | 90           |

|                   |              |              |

| 160               | 00           | A0           |

|                   |              |              |

| 256               | 01           | 00.          |

#### **BYTE 8 - Module Interface Signal Levels**

This field describes the SDRAM module signal voltage interface.

| Voltage Interface | Hex Value |

|-------------------|-----------|

| 5.0 Volt/TTL      | 00        |

| LVTTL             | 01        |

| HSTL 1.5          | 02        |

| SSTL 3.3          | 03        |

| SSTL 2.5          | 04        |

| TBD               | 05        |

| TBD               | 06        |

|                   |           |

| New Table         | FF        |

#### **BYTE 9 - SDRAM Cycle time (highest CAS latency)**

This field defines the total minimum cycle time (clock period) for the SDRAM. For example if the SDRAMs support CAS latency of 3, 2 and 1 (as indicated in byte 18), this byte defines Tclk for CAS latency 3. The byte is broken into two nibbles: the high order nibble (bits 4 through 7) designate the cycle time to a granularity of 1 ns; the value presented by the low order nibble has a granularity of 1/10 ns and is added to the value of the higher nibble.

#### **BYTE 10 - SDRAM Access time from Clock (highest CAS latency)**

This field defines the maximum clock to data out for the SDRAM (Tac). For example if the SDRAMs support CAS latency of 3, 2 and 1 (as indicated in byte 18), this byte defines Tac for CAS latency 3. The byte is broken into two nibbles: the high order nibble (bits 4 through 7) designate the cycle time to a granularity of 1 ns; the value presented by the low order nibble has a granularity of 1/10 ns and is added to the value of the higher nibble.

#### **BYTE 11 - Module Configuration Type**

This field defines the module's error detection and correction scheme.

| Error Detect/Correct | Hex Value |

|----------------------|-----------|

| None                 | 00        |

| Parity               | 01        |

| ECC                  | 02        |

| TBD                  | 03        |

| TBD                  | 04        |

| TBD                  | 05        |

| TBD                  | 06        |

|                      |           |

| TBD                  | FF        |

#### **BYTE 12 - Refresh Rate/Type**

This field defines the module's refresh rate and type.

| Refresh Period        | Bit 7, Self Refresh<br>Flag | Bits 6-0 (hex) |

|-----------------------|-----------------------------|----------------|

| Normal (15.625 us)    | 0                           | 00             |

| Reduced (.25x)3.9 us  | 0                           | 01             |

| Reduced (.5x) 7.8 us  | 0                           | 02             |

| Extended (2x) 31.3 us | 0                           | 03             |

| Extended (4x) 62.5 us | 0                           | 04             |

| Extended (8x) 125 us  | 0                           | 05             |

| TBD                   | 0                           | 06             |

| TBD                   | 0                           | 07             |

| TBD                   | 0                           | 08             |

| TBD                   | 0                           | 09             |

|                       |                             |                |

|                       | Self Refresh                |                |

| Normal (15.625 us)    | 1                           | 00             |

| Reduced (.25x)3.9 us  | 1                           | 01             |

| Reduced (.5x) 7.8 us  | 1                           | 02             |

| Extended (2x) 31.3 us | 1                           | 03             |

| Extended (4x) 62.5 us | 1                           | 04             |

| Extended (8x) 125 us  | 1                           | 05             |

| TBD                   | 1                           | 06             |

| TBD                   |                             |                |

| TBD                   |                             |                |

|                       |                             |                |

| TBD                   | 1                           | 7F             |

#### **BYTE 13 - SDRAM Width (Primary SDRAM)**

Bits 6:0 of this byte define the data width of the primary SDRAM components used on the module. The primary SDRAM is that which is used for data. Examples of primary (data) SDRAM widths are x4, x8, x16, x32. Bit 7 of this byte is a flag which indicates that a 2nd bank on the module has a primary SDRAM width of 2X that of the first bank. If the module has two banks with the same Primary SDRAM width, then bit 7 remains as "0".

| Primary SDRAM Component Data Width | Bits 6:0 Hex Value |

|------------------------------------|--------------------|

| Undefined                          | 00                 |

| 1                                  | 01                 |

| 2                                  | 02                 |

| 3                                  | 03                 |

| 4                                  | 04                 |

|                                    |                    |

| 8                                  | 08                 |

|                                    |                    |

| 16                                 | 10                 |

|                                    |                    |

| 32                                 | 20                 |

|                                    |                    |

| 127                                | 7F                 |

| Bank Configuration      | Bits 7 Value |

|-------------------------|--------------|

| No Bank 2 -OR-          |              |

| Bank 2 uses same width  | 0            |

| Primary SDRAM as Bank 1 |              |

| Bank 2 Primary SDRAM is |              |

| 2X the width of Bank 1  | 1            |

#### **BYTE 14 - Error Checking SDRAM Width**

If the module incorporates error checking and if the primary data SDRAM does not include these bits; i.e. there are separate error checking SDRAMs, then the error checking SDRAM's width is expressed in this byte. Examples of error checking SDRAM widths include x4, x8, x16.

Bits 6:0 of this byte define the data width of the Error Checking SDRAM components used on the module. Bit 7 is a flag which indicates that a 2nd bank on the module has Error Checking SDRAM width. of 2X that of the first bank. If the module has two banks with the same Error Checking SDRAM width, then bit 7 remains as "0".

| Error Checking SDRAM<br>Component Data Width | Bits 6:0 Hex Value |

|----------------------------------------------|--------------------|

| Undefined                                    | 00                 |

| 1                                            | 01                 |

| 2                                            | 02                 |

| 3                                            | 03                 |

| 4                                            | 04                 |

| 5                                            | 05                 |

| 6                                            | 06                 |

| 7                                            | 07                 |

| 8                                            | 08                 |

|                                              |                    |

| 16                                           | 10                 |

|                                              |                    |

| 32                                           | 20                 |

|                                              |                    |

| 127                                          | 7F                 |

| Bank Configuration        | Bits 7 Value |

|---------------------------|--------------|

| No Bank 2 -OR-            |              |

| Bank 2 uses same width EC | 0            |

| SDRAM as Bank 1           |              |

| Bank 2 EC SDRAM is 2X     | ,            |

| the width of Bank 1       | 1            |

BYTE 15 - SDRAM Device Attributes, Min Clock Delay for Back to Back Random Column Addresses

| Number of Clocks | Hex Value |

|------------------|-----------|

| Undefined        | 00        |

| 1                | 01        |

| 2                | 02        |

| 3                | 03        |

| 4                | 04        |

| 5                | 05        |

| 6                | 06        |

|                  |           |

| 255              | FF        |

|                  |           |

Nov, 1997 17 of 27 Revision 1.2

#### BYTE 16 - SDRAM Device Attributes, Burst Lengths Supported

This byte defines various burst lengths supported. If the burst length is supported, then the corresponding bit is "1"

| Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3        | Bit 2        | Bit 1        | Bit 0        |

|--------------|-------|-------|-------|--------------|--------------|--------------|--------------|

| Burst Length | TBD   | TBD   | TBD   | Burst Length | Burst Length | Burst Length | Burst Length |

| = Page       |       |       |       | = 8          | = 4          | = 2          | = 1          |

| 1 or 0       | 0     | 0     | 0     | 1 or 0       | 1 or 0       | 1 or 0       | 1 or 0       |

#### BYTE 17 - SDRAM Device Attributes, Number of Banks on SDRAM Device

This byte defines the number of banks internal to the SDRAM devices for each row of the DIMMs.

| Number of Device Banks | Hex Value |

|------------------------|-----------|

| Resvd.                 | 00        |

| 1                      | 01        |

| 2                      | 02        |

| 3                      | 03        |

| 4                      | 04        |

| 5                      | 05        |

|                        |           |

|                        |           |

| 256                    | FF        |

#### **BYTE 18 - SDRAM Device Attributes, CAS Latency**

This byte defines which CAS latencies are supported. If the bit is "1" then that CAS Latency is supported.

| Bit 7  | Bit 6       | Bit 5       | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0       |

|--------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| TBD    | CAS         |

|        | Latency = 7 | Latency = 6 | Latency = 5 | Latency = 4 | Latency = 3 | Latency = 2 | Latency = 1 |

| 1 or 0 | 1 or 0      | 1 or 0      | 1 or 0      | 1 or 0      | 1 or 0      | 1 or 0      | 1 or 0      |

#### **BYTE 19 - SDRAM Device Attributes, CS Latency**

This byte defines which CS latencies are acceptable for the Module. If the bit is "1" then that CS Latency is supported.

| Bit 7  | Bit 6      | Bit 5      | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      |

|--------|------------|------------|------------|------------|------------|------------|------------|

| TBD    | CS Latency |

|        | = 6        | = 5        | = 4        | = 3        | = 2        | = 1        | = 0        |

| 1 or 0 | 1 or 0     | 1 or 0     | 1 or 0     | 1 or 0     | 1 or 0     | 1 or 0     | 1 or 0     |

#### **BYTE 20 - SDRAM Device Attributes, WE Latency**

This byte defines which CS latencies are acceptable for the Module. If the bit is "1" then that WE Latency is supported.

| Bit 7  | Bit 6      | Bit 5      | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      |

|--------|------------|------------|------------|------------|------------|------------|------------|

| TBD    | WE Latency |

|        | = 6        | = 5        | = 4        | = 3        | = 2        | = 1        | = 0        |

| 1 or 0 | 1 or 0     | 1 or 0     | 1 or 0     | 1 or 0     | 1 or 0     | 1 or 0     | 1 or 0     |

Nov, 1997 18 of 27 Revision 1.2

#### **BYTE 21 - SDRAM Module Attributes**

This byte defines various aspects of the module. If the aspect is TRUE, then the corresponding bit is "1".

| Bit 7 | Bit 6     | Bit 5        | Bit 4      | Bit 3    | Bit 2       | Bit 1      | Bit 0    |

|-------|-----------|--------------|------------|----------|-------------|------------|----------|

| TBD   | Redundant | Differential | Registered | Buffered | On-Card     | Registered | Buffered |

|       | Row Addr  | Clock Input  | DQMB       | DQMB     | PLL (Clock) | Address/   | Address/ |

|       |           |              | Inputs     | Inputs   |             | Control    | Control  |

|       |           |              | -          | -        |             | Inputs *   | Inputs * |

| 0     | 1 or 0    | 1 or 0       | 1 or 0     | 1 or 0   | 1 or 0      | 1 or 0     | 1 or 0   |

<sup>\*</sup> Address, RAS, CAS, WE, CKE, S

#### **BYTE 22 - SDRAM Device Attributes, General**

This byte defines various aspects of the SDRAMs on the module. If the aspect is TRUE, then the corresponding bit is "1".

| Bit 7 | Bit 6 | Bit 5                                        | Bit 4                                        | Bit 3                            | Bit 2                        | Bit 1                          | Bit 0                               |

|-------|-------|----------------------------------------------|----------------------------------------------|----------------------------------|------------------------------|--------------------------------|-------------------------------------|

| TBD   | TBD   | Upper Vcc<br>tolerance:<br>0 = 10%<br>1 = 5% | Lower Vcc<br>tolerance:<br>0 = 10%<br>1 = 5% | Supports<br>Write1/Read<br>Burst | Supports<br>Precharge<br>All | Supports<br>Auto-<br>Precharge | Supports<br>Early RAS#<br>Precharge |

| 0     | 0     | 1 or 0                                       | 1 or 0                                       | 1 or 0                           | 1 or 0                       | 1 or 0                         | 1 or 0                              |

Vcc Tolerance refers to the voltage range under which the SDRAMs operate to the timings specified in the SPD bytes 9, 10, 23-30.

**Note for Bytes 23-24:** Bytes 23-24 show a roll-up value for Hex 1, 2, 3 (i.e., 1ns/16ns). For SDRAM devices over duration of REV 1 in Byte 62 (SPDedec Rev level), values of 1-3ns are not expected, and Hex equivalent is 16-18nsJedec Byte 62 will change rev level when values of 1-3 ns become available.

#### BYTE 23 - SDRAM Cycle time (2nd highest CAS latency)

This field defines the minimum cycle time (clock period) for the SDRAM when operating at its 2nd highest CAS latency. For example if the SDRAMs support CAS latency of 3, 2 and 1 ( as indicated in byte 18), this byte defines clk for CAS latency 2. The byte is broken into two nibbles: the high order nibble (bits 4 through 7) designate the cycle time to a granularity of 1 ns; the value presented by the low order nibble has a granularity of 1/10 ns and is added to the value of the higher nibble.

| Nanoseconds | Bits 7-4 Hex Value |

|-------------|--------------------|

| Undefined   | 0                  |

| 1ns / 16ns  | 1                  |

| 2ns / 17ns  | 2                  |

| 3ns / 18 ns | 3                  |

| 4           | 4                  |

|             | •                  |

| 15          | F                  |

| 1/10 nanoseconds | Bits 3-0 Hex Value |

|------------------|--------------------|

| 0                | 0                  |

| 1                | 1                  |

| 2                | 2                  |

| 3                | 3                  |

| 4                | 4                  |

|                  |                    |

| 9                | 9                  |

<sup>\*\*</sup> Redundant addressing implies the use of SDRAMs having the same address depth (e.g. 4Mx4 mixed with 4Mx16) in the same 8-byte quad word, but having different RAS/CAS addressing and/or different numbers of device banks. Actual implementation is not yet determined.

#### BYTE 24 - SDRAM Access from Clock (2nd highest CAS latency)

This field defines the maximum clock to data out for the SDRAMT(ac) when operating at its 2nd highest CAS latency. For example if the SDRAMs support CAS latency of 3, 2 and 1( as indicated in byte 18), this byte defines ac for CAS latency 2. The byte is broken into two nibbles: the high order nibble (bits 4 through 7) designate the cycle time to a granularity of 1 ns; the value presented by the low order nibble has a granularity of 1/10 ns and is added to the value of the higher nibble.

| Nanoseconds | Bits 7-4 Hex Value |

|-------------|--------------------|

| Undefined   | 0                  |

| 1ns / 16ns  | 1                  |

| 2ns / 17ns  | 2                  |

| 3ns / 18 ns | 3                  |

| 4           | 4                  |

|             |                    |

| 15          | F                  |

| 1/10 nanoseconds | Bits 3-0 Hex Value |

|------------------|--------------------|

| 0                | 0                  |

| 1                | 1                  |

| 2                | 2                  |

| 3                | 3                  |

| 4                | 4                  |

|                  |                    |

| 9                | 9                  |

#### BYTE 25 - SDRAM Cycle time (3rd highest CAS latency)

This field defines the minimum cycle time (clock period) for the SDRAM when operating at its 3rd highest CAS latency. For example if the SDRAMs support CAS latency of 3, 2 and 1 ( as indicated in byte 18), this byte define clk for CAS latency 1. The byte is broken into two sections: the 6 high order bits (bits 7:2) designate the cycle time to a granularity of 1 ns; the value presented by bits 1:0 has a granularity of 1/4 ns and is added to the value of the higher nibble.

| Nanoseconds | Bits 7-2     |

|-------------|--------------|

|             | Binary Value |

| Undefined   | 000000       |

| 1ns         | 000001       |

| 2ns         | 000010       |

| 3ns         | 000011       |

| 4           | 000100       |

|             |              |

| 63          | 111111       |

| 1/4 nanoseconds | Bits 1-0<br>binary value |

|-----------------|--------------------------|

| 0               | 00                       |

| 1               | 01                       |

| 2               | 10                       |

| 3               | 11                       |

#### BYTE 26 - SDRAM Access from Clock (3rd highest CAS latency)

This field defines the maximum clock to data out for the SDRAMs (ac) when operated at its 3rd highest CAS latency. For example if the SDRAMs support CAS latency of 3, 2 and 1( as indicated in byte 18), this byte defines ac for CAS latency 1. The byte is broken into two sections: the 6 high order bits (bits 7:2) designate the access time to a granularity of 1 ns; the value presented by bits 1:0 has a granularity of 1/4 ns and is added to the value of the higher nibble.

| Nanoseconds | Bits 7-2     |

|-------------|--------------|

|             | Binary Value |

| Undefined   | 000000       |

| 1ns         | 000001       |

| 2ns         | 000010       |

| 3ns         | 000011       |

| 4           | 000100       |

|             |              |

| 63          | 111111       |

|             |              |

| 1/4 nanoseconds | Bits 1-0     |

|-----------------|--------------|

|                 | Binary Value |

| 0               | 00           |

| 1               | 01           |

| 2               | 10           |

| 3               | 11           |

#### **BYTE 27 - Minimum Row Precharge Time**

This byte defines the precharge to activate minimum (Trp) using 1ns granularity.

| Precharge Minimum | Bits 7-0<br>Hex Value |  |  |

|-------------------|-----------------------|--|--|

| undefined         | 00                    |  |  |

| 1 ns              | 01                    |  |  |

| 2 ns              | 02                    |  |  |

|                   | •                     |  |  |

| 30 ns             | 1E                    |  |  |

|                   |                       |  |  |

| 45 ns             | 2D                    |  |  |

|                   |                       |  |  |

| 255 ns            | FF                    |  |  |

#### **BYTE 28 - Row Active to Row Active Min**

This byte defines the minimum row activate to row activate delayr(d) using 1 ns granularity.

| Act to Act Minimum | Bits 7-0<br>Hex Value |

|--------------------|-----------------------|

| undefined          | 0                     |

| 1 ns               | 1                     |

| 2 ns               | 2                     |

|                    |                       |

| 30 ns              | 1E                    |

|                    |                       |

| 45 ns              | 2D                    |

|                    |                       |

| 255 ns             | FF                    |

# **BYTE 29 - RAS to CAS Delay Min**

This byte defines the minimum RAS to CAS delay (rcd) using 1ns granularity.

| RAS to CAS Delay<br>Minimum | Bits 7-0<br>Hex Value |

|-----------------------------|-----------------------|

| undefined                   | 0                     |

| 1 ns                        | 1                     |

| 2 ns                        | 2                     |

|                             | •                     |

| 30 ns                       | 1E                    |

|                             |                       |

| 45 ns                       | 2D                    |

|                             |                       |

| 255 ns                      | FF                    |

#### **BYTE 30 - Minimum RAS Pulse Width**

This byte defines the minimum activate torrecharge time (Tras) using 1 ns granularity.

| Activate to Precharge<br>Minimum | Bits 7-0<br>Hex Value |  |  |

|----------------------------------|-----------------------|--|--|

| undefined                        | 0                     |  |  |

| 1 ns                             | 1                     |  |  |

| 2 ns                             | 2                     |  |  |

|                                  |                       |  |  |

| 60 ns                            | 3C                    |  |  |

|                                  |                       |  |  |

| 75 ns                            | 4B                    |  |  |

|                                  |                       |  |  |

| 90 ns                            | 5A                    |  |  |

|                                  |                       |  |  |

| 255 ns                           | FF                    |  |  |

#### **BYTE 31 - Density of Each Row on Module**

This byte describes the memory capacity of each physical row on the DIMM module.. This byte will have at least one bit set to a "1" to represent at least one row's size. If there is more than one row on the module (as represented in Byte 5) and they have the same size, then only one bit in this field is set. If the module has more than one row of different sizes then more than one bit will be set. For example:

| # Banks | Size of Row 1 | Size of Row 2 | Byte 31 contents |

|---------|---------------|---------------|------------------|

| 1       | 32MByte       | N/A           | 0000 1000        |

| 2       | 32MByte       | 32MByte       | 0000 1000        |

| 2       | 32MByte       | 16MByte       | 0000 1100        |

|     |    | Bit 7    | Bit 6   | Bit 5    | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

|-----|----|----------|---------|----------|---------|---------|---------|--------|--------|

| Siz | ze | 512MByte | 256MByt | 128MByte | 64MByte | 32MByte | 16MByte | 8MByte | 4MByte |

|     |    |          | е       |          |         |         |         |        |        |

| N/  | Υ  | 0        | 0       | 1 or 0   | 1 or 0  | 1 or 0  | 1 or 0  | 1 or 0 | 1 or 0 |

# BYTE 32 - 35 - Input setup and Hold time (Under JEDEC Committee Ballot no. JC42.5-97-119)

Definition of these bytes are in JEDEC Ballot process. The proposed data structure is as defined:

| Bit 7                 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1    | Bit 0   |

|-----------------------|--------|--------|--------|--------|--------|----------|---------|

| Positive/<br>Negative | Setup  | Time   | in ns  | Setup  | Time   | in tenth | of a ns |

| 1 or 0                | 1 or 0 | 1 or 0 | 1 or 0 | 1 or 0 | 1 or 0 | 1 or 0   | 1 or 0  |

Bit 7 = 0 defines a positive setup timev.r.t. the clock

Bit 7 = 1 defines a negative setup timew.r.t the clock

Bit 6-4 = Defines the setup time in ns.

Bit 3-0= Defines the setup time in tenth of a ns.

Nov, 1997 22 of 27 Revision 1.2

Some encoded values in the table:

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Comment |

|-------|-------|-------|-------|-------|-------|-------|-------|---------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0 ns    |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0.1 ns  |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0.2 ns  |

|       |       | •     | •     |       |       |       |       |         |