# intel®

## Intel<sup>®</sup> Celeron<sup>™</sup> Processor Specification Update

Release Date: March 1999

Order Number: 243748-013

The Intel<sup>®</sup> Celeron<sup>™</sup> processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this Specification Update.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> Celeron<sup>™</sup> processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

The Specification Update should be publicly available following the last shipment date for a period of time equal to the specific product's warranty period. Hardcopy Specification Updates will be available for one (1) year following End of Life (EOL). Web access will be available for three (3) years following EOL.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725 or by visiting Intel's website at <a href="http://www.intel.com">http://www.intel.com</a>

Copyright © Intel Corporation 1999.

\* Third-party brands and names are the property of their respective owners.

## CONTENTS

| REVISION HISTORY                                    | V  |

|-----------------------------------------------------|----|

| PREFACE                                             | vi |

| Specification Update for Intel® Celeron™ Processors | 1  |

| GENERAL INFORMATION                                 | 3  |

| ERRATA                                              |    |

| DOCUMENTATION CHANGES                               |    |

| SPECIFICATION CLARIFICATIONS                        |    |

| SPECIFICATION CHANGES                               |    |

|                                                     |    |

## intel

## **REVISION HISTORY**

| Date of Revision | Version | Description                                                                                                                                                                                                                         |  |  |  |  |  |

|------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| April 1998       | -001    | This document is the first Specification Update for the Intel <sup>®</sup><br>Celeron <sup>™</sup> processor.                                                                                                                       |  |  |  |  |  |

| May 1998         | -002    | Added Errata 24 through 28.                                                                                                                                                                                                         |  |  |  |  |  |

| June 1998        | -003    | Updated S-spec Table. Updated Summary Table of Changes.<br>Updated Erratum 2 and 26. Added Errata 29 and 30. Added<br>Documentation Changes 7 through 12. Added Specification<br>Clarification 6 and 7.                             |  |  |  |  |  |

| July 1998        | -004    | Updated S-spec Table. Added Documentation Changes 13 through<br>16. Added Specification Clarifications 7 through 12. Added<br>Specification Change 1.                                                                               |  |  |  |  |  |

| August 1998      | -005    | Updated Summary Table of Changes. Changed numbering in order<br>to maintain consistency with other product Specification Updates.<br>Updated Errata 6 and 38. Added Errata 56 through 59. Updated<br>Specification Clarification 5. |  |  |  |  |  |

| September 1998   | -006    | Updated S-spec table. Updated Erratum 56. Added Errata 60 through 62.                                                                                                                                                               |  |  |  |  |  |

| October 1998     | -007    | Implemented new numbering nomenclature. Updated Errata C1 and C27. Added Errata C37 through C39. Added Specification Clarification C15. Added Specification Change C2.                                                              |  |  |  |  |  |

| November 1998    | -008    | Updated Erratum C23. Added Erratum C40. Updated Documentation<br>Change C10. Added Documentation Changes C17 and C18. Added<br>Specification Change C3.                                                                             |  |  |  |  |  |

| December 1998    | -009    | Added the Intel Celeron Processor (PPGA) markings. Added the mB0 stepping to the Processor Identification Information table and the Table of Changes. Added Errata C41 and C42.                                                     |  |  |  |  |  |

| December 1998    | -010    | Updated Identification Information table                                                                                                                                                                                            |  |  |  |  |  |

| January 1999     | -011    | Added Erratum C3AP. Added Documentation Changes C19 and C20. Updated Processor Identification Information table.                                                                                                                    |  |  |  |  |  |

| February 1999    | -012    | Updated Processor Identification Information table.                                                                                                                                                                                 |  |  |  |  |  |

| March 1999       | -013    | Updated Processor Markings, Summary Table of Changes,<br>Documentation Changes, Specification Clarifications, and<br>Specification Changes sections. Added Specification Change C1.                                                 |  |  |  |  |  |

## PREFACE

This document is an update to the specifications contained in the *Pentium*<sup>®</sup> *II Processor Developer's Manual* (Order Number 243502), *Intel<sup>®</sup> Celeron™ Processor* datasheet (Order Number 243658), and the *Intel Architecture Software Developer's Manual, Volumes 1, 2, and 3* (Order Numbers 243190, 243191, and 243192, respectively). It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools. It contains Specification Changes, Errata, Specification Clarifications, and Documentation Changes.

#### Nomenclature

**S-Spec Number** is a five digit code used to identify products. Products are differentiated by their unique characteristics, e.g., core speed, L2 cache size, package type, etc. as described in the processor identification information table. Care should be taken to read all notes associated with each S-Spec number.

Specification Changes are modifications to the current published specifications for the Intel<sup>®</sup> Celeron<sup>™</sup> processor. These changes will be incorporated in the next release of the appropriate document(s).

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in the next release of the appropriate document(s).

**Documentation Changes** include errors (including typographical) or omissions from the current published specifications. These changes will be incorporated in the next release of the specifications.

**Errata** are design defects or errors. Errata may cause the Intel Celeron processor's behavior to deviate from published specifications. Hardware and software designed to be used with any given processor stepping must assume that all errata documented for that processor stepping are present on all devices unless otherwise noted.

### Identification Information

Complete identification information of the Intel Celeron processor can be found in the *Intel Processor Identification and the CPUID Instruction* application note (Order Number 241618).

Specification Update for Intel® Celeron™ Processors

## **GENERAL INFORMATION**

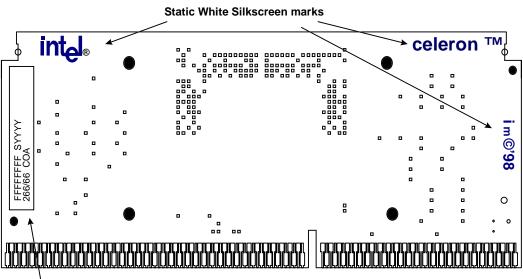

## Intel<sup>®</sup> Celeron<sup>™</sup> Processor and Boxed Intel<sup>®</sup> Celeron<sup>™</sup> Processor Markings (S.E.P. Package)

#### Dynamic laser mark area

NOTES:

- SYYYY = S-spec Number.

- FFFFFFF = FPO # (Test Lot Traceability #).

- COA = Country of Assembly.

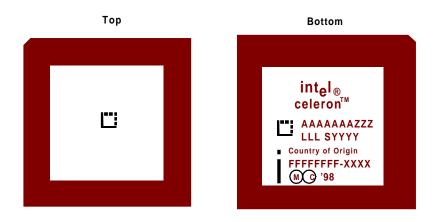

#### Intel<sup>®</sup> Celeron<sup>™</sup> Processor and Boxed Intel<sup>®</sup> Celeron<sup>™</sup> Processor Markings (PPGA Package)

#### NOTES:

- AAAAAAA = Product Code

- ZZZ = Processor Speed (MHz)

- LLL = Integrated Level-Two Cache Size (in Kilobytes)

- SYYYY = S-Spec Number

- FFFFFFFF-XXXX = Assembly Lot Tracking Number

2-D Matrix Mark Intel UCC# Order Code (Product - speed) S Number Lot Number (date, factory)

## intel

|        | -                | 100                 |              |                         |                     |       |

|--------|------------------|---------------------|--------------|-------------------------|---------------------|-------|

| S-Spec | Core<br>Stepping | L2 Size<br>(Kbytes) | CPUID        | Speed (MHz)<br>Core/Bus | Package<br>Revision | Notes |

| SL2SY  | dA0              | 0                   | 0650h        | 266/66                  | SEPP Rev. 1         | 4     |

| SL2YN  | dA0              | 0                   | 0650h        | 266/66                  | SEPP Rev. 1         | 1, 4  |

| SL2YP  | dA0              | 0                   | 0650h        | 300/66                  | SEPP Rev. 1         | 4     |

| SL2Z7  | dA0              | 0                   | 0650h        | 300/66                  | SEPP Rev. 1         | 1, 4  |

| SL2TR  | dA1              | 0                   | 0651h        | 266/66                  | SEPP Rev. 1         | 4     |

| SL2QG  | dA1              | 0                   | 0651h        | 266/66                  | SEPP Rev. 1         | 1, 4  |

| SL2X8  | dA1              | 0                   | 0651h        | 300/66                  | SEPP Rev. 1         | 4     |

| SL2Y2  | dA1              | 0                   | 0651h        | 300/66                  | SEPP Rev. 1         | 1, 4  |

| SL2Y3  | dB0              | 0                   | 0652h        | 266/66                  | SEPP Rev. 1         | 1, 4  |

| SL2Y4  | dB0              | 0                   | 0652h        | 300/66                  | SEPP Rev. 1         | 1, 4  |

| SL2WM  | mA0              | 128                 | 0660h        | 300A/66                 | SEPP Rev. 1         | 3, 4  |

| SL32A  | mA0              | 128                 | 0660h        | 300A/66                 | SEPP Rev. 1         | 1, 4  |

| SL2WN  | mA0              | 128                 | 0660h        | 333/66                  | SEPP Rev. 1         | 3, 4  |

| SL32B  | mA0              | 128                 | 0660h        | 333/66                  | SEPP Rev. 1         | 1, 4  |

| SL376  | mA0              | 128                 | 0660h        | 366/66                  | SEPP Rev. 1         | 4     |

| SL37Q  | mA0              | 128                 | 0660h 366/66 |                         | SEPP Rev. 1         | 1, 4  |

| SL39Z  | mA0              | 128                 | 0660h        | 400/66                  | SEPP Rev. 1         | 4     |

| SL37V  | mA0              | 128                 | 0660h        | 400/66                  | SEPP Rev. 1         | 1, 4  |

| SL35Q  | mB0              | 128                 | 0665h        | 300A/66                 | PPGA                | 2, 4  |

| SL36A  | mB0              | 128                 | 0665h        | 300A/66                 | PPGA                | 4     |

| SL35R  | mB0              | 128                 | 0665h        | 333/66                  | PPGA                | 2, 4  |

| SL36B  | mB0              | 128                 | 0665h        | 333/66                  | PPGA                | 4     |

| SL36C  | mB0              | 128                 | 0665h        | 366/66                  | PPGA                | 4     |

| SL35S  | mB0              | 128                 | 0665h        | 366/66                  | PPGA                | 2, 4  |

| SL3A2  | mB0              | 128                 | 0665h        | 400/66                  | PPGA                | 4     |

| SL37X  | mB0              | 128                 | 0665h        | 400/66                  | PPGA                | 2, 4  |

#### Intel<sup>®</sup> Celeron<sup>™</sup> Processor Identification Information

#### NOTES:

1. This is a boxed Intel<sup>®</sup> Celeron<sup>™</sup> processor with an attached fan heatsink.

2. This is a boxed Intel Celeron processor with an unattached fan heatsink.

3. This part also ships as a boxed Intel Celeron processor with an attached fan heatsink.

4. This processor has a maximum  $T_{\mbox{CASE}}$  of 85  $^{\circ}\mbox{C}.$

#### Summary Table of Changes

The following table indicates the Specification Changes, Errata, Specification Clarifications, or Documentation Changes which apply to the Intel Celeron processors. Intel intends to fix some of the errata in a future stepping of the component, and to account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

#### CODES USED IN SUMMARY TABLE

| X:                        | Specification Change, Erratum, Specification Clarification, or Documentation Change applies to the given processor stepping. |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Doc:                      | Intel intends to update the appropriate documentation in a future revision.                                                  |

| Fix:                      | This erratum is intended to be fixed in a future stepping of the component.                                                  |

| Fixed:                    | This erratum has been previously fixed.                                                                                      |

| NoFix:                    | There are no plans to fix this erratum.                                                                                      |

| (No mark) or (blank box): | This item is fixed in or does not apply to the given stepping.                                                               |

| AP:                       | APIC related erratum.                                                                                                        |

| SUB:                      | This column refers to errata on the Intel <sup>®</sup> Celeron <sup>™</sup> processor substrate.                             |

| Shaded:                   | This erratum is either new or modified from the previous version of the document.                                            |

Some of Intel's Specification Updates will be undergoing a numbering methodology change to reduce confusion when referring to errata which affect a specific product. Each Specification Update item will be prefixed with a capital letter to distinguish the product it refers to. The key below details the letters which will be used for the current Intel microprocessor Specification Updates:

- A = Pentium<sup>®</sup> II processor

- B = Mobile Pentium II processor

- C = Intel<sup>®</sup> Celeron<sup>™</sup> processor

- D = Pentium<sup>®</sup> II Xeon<sup>™</sup> processor

- E = Pentium<sup>®</sup> III processor

- G = Pentium<sup>®</sup> III Xeon<sup>™</sup> processor

The Specification Updates for the Pentium<sup>®</sup> processor, Pentium Pro processor, and other Intel products will not be implementing such a convention at this time.

## intel

#### INTEL<sup>®</sup> CELERON<sup>™</sup> PROCESSOR SPECIFICATION UPDATE

| NO. | dA0 | dA1 | dB0 | mA0 | mB0 | SUB | Plans | ERRATA                                                                                                                   |  |

|-----|-----|-----|-----|-----|-----|-----|-------|--------------------------------------------------------------------------------------------------------------------------|--|

| C1  | x   | Х   | Х   | Х   | Х   |     | NoFix | FP Data Operand Pointer may be incorrectly<br>calculated after FP access which wraps 64-Kbyte<br>boundary in 16-bit code |  |

| C2  | Х   | Х   | Х   | Х   | Х   |     | NoFix | Differences exist in debug exception reporting                                                                           |  |

| C3  | х   | Х   | Х   | Х   | Х   |     | NoFix | Code fetch matching disabled debug register may<br>cause debug exception                                                 |  |

| C4  | Х   | Х   | Х   | Х   | Х   |     | NoFix | FP inexact-result exception flag may not be set                                                                          |  |

| C5  | Х   | Х   | Х   | Х   | Х   |     | NoFix | BTM for SMI will contain incorrect FROM EIP                                                                              |  |

| C6  | х   | Х   | Х   | Х   | Х   |     | NoFix | I/O restart in SMM may fail after simultaneous MCE                                                                       |  |

| C7  | х   | Х   | Х   | Х   | Х   |     | NoFix | Branch traps do not function if BTMs are also enabled                                                                    |  |

| C8  | х   | Х   | Х   | Х   | Х   |     | NoFix | Machine check exception handler may not always<br>execute successfully                                                   |  |

| C9  | Х   | Х   | Х   | Х   | Х   |     | NoFix | LBER may be corrupted after some events                                                                                  |  |

| C10 | х   | Х   | х   | Х   | Х   |     | NoFix | BTMs may be corrupted during simultaneous L1 cache line replacement                                                      |  |

| C11 | х   | Х   |     | Х   | Х   |     | Fix   | Potential early deassertion of LOCK# during split-<br>lock cycles                                                        |  |

| C12 | Х   | Х   | Х   | Х   | Х   |     | NoFix | A20M# may be inverted after returning from SMM and Reset                                                                 |  |

| C13 | х   | Х   |     |     |     |     | Fix   | Reporting of floating-point exception may be<br>delayed                                                                  |  |

| C14 | х   | Х   | х   | Х   | Х   |     | NoFix | Near CALL to ESP creates unexpected EIP address                                                                          |  |

| C15 | Х   | Х   |     |     |     |     | Fix   | Built-in self test always gives nonzero result                                                                           |  |

| C16 | Х   | Х   |     | Х   | Х   |     | Fix   | THERMTRIP# may not be asserted as specified                                                                              |  |

| C17 | х   |     |     |     |     |     | Fixed | Cache state corruption in the presence of page<br>A/D-bit setting and snoop traffic                                      |  |

| C18 | х   |     |     |     |     |     | Fixed | Snoop cycle generates spurious machine check exception                                                                   |  |

| C19 | х   | Х   |     |     |     |     | Fixed | MOVD/MOVQ instruction writes to memory<br>prematurely                                                                    |  |

| C20 | Х   | Х   | Х   | Х   | Х   |     | NoFix | Memory type undefined for nonmemory operations                                                                           |  |

| C21 | Х   | Х   |     |     |     |     | Fixed | Bus protocol conflict with optimized chipsets                                                                            |  |

| C22 | Х   | Х   | Х   | Х   | Х   |     | NoFix | FP Data Operand Pointer may not be zero after power on or Reset                                                          |  |

| C23 | Х   | Х   | Х   | Х   | Х   |     | NoFix | MOVD following zeroing instruction can cause incorrect result                                                            |  |

#### INTEL® CELERON™ PROCESSOR SPECIFICATION UPDATE

| NO.  | dA0 | dA1 | dB0 | mA0 | mB0 | SUB | Plans | ERRATA                                                                                                |  |

|------|-----|-----|-----|-----|-----|-----|-------|-------------------------------------------------------------------------------------------------------|--|

| C24  | х   | Х   | Х   | Х   | Х   |     | NoFix | Premature execution of a load operation prior to<br>exception handler invocation                      |  |

| C25  | х   | Х   | х   | Х   | Х   |     | NoFix | Read portion of RMW instruction may execute twice                                                     |  |

| C26  | Х   | Х   | Х   | Х   | Х   |     | Fix   | Test pin must be high during power up                                                                 |  |

| C27  | х   | Х   | Х   | Х   | Х   |     | Fix   | Intervening writeback may occur during locked transaction                                             |  |

| C28  | Х   | Х   | Х   | Х   | х   |     | NoFix | MC2_STATUS MSR has model-specific error code<br>and machine check architecture error code<br>reversed |  |

| C29  | Х   | Х   | Х   | Х   | Х   |     | NoFix | MOV with debug register causes debug exception                                                        |  |

| C30  | Х   | Х   | Х   | Х   | Х   |     | NoFix | Upper four PAT entries not usable with Mode B or<br>Mode C paging                                     |  |

| C31  | х   | Х   | х   |     |     |     | Fixed | Incorrect memory type may be used when MTRRs are disabled                                             |  |

| C32  | Х   | Х   | Х   | Х   |     |     | Fixed | Misprediction in program flow may cause<br>unexpected instruction execution                           |  |

| C33  | х   | Х   | х   | Х   | Х   |     | NoFix | Data Breakpoint Exception in a Displacement<br>Relative Near Call May Corrupt EIP                     |  |

| C34  | Х   | Х   | Х   | Х   | Х   |     | NoFix | System bus ECC not functional with 2:1 ratio                                                          |  |

| C35  | х   | Х   | х   | Х   |     |     | Fixed | Fault on REP CMPS/SCAS operation may cause incorrect EIP                                              |  |

| C36  | х   | Х   | Х   | Х   | Х   |     | NoFix | RDMSR and WRMSR to invalid MSR may not<br>cause GP fault                                              |  |

| C37  | х   | Х   | Х   | Х   | Х   |     | NoFix | SYSENTER/SYSEXIT instructions can implicitly<br>load null segment selector to SS and CS registers     |  |

| C38  | х   | Х   | Х   | Х   | Х   |     | NoFix | PRELOAD followed by EXTEST does not load<br>boundary scan data                                        |  |

| C39  | Х   | Х   | Х   | Х   | Х   |     | NoFix | Far jump to new TSS with D-bit cleared may cause system hang                                          |  |

| C40  | х   | Х   | х   |     |     |     | Fixed | Incorrect chunk ordering may prevent execution of the machine check exception handler after BINIT#    |  |

| C41  | х   | Х   | Х   | Х   |     |     | Fixed | UC Write May be Reordered Around a Cacheable Write                                                    |  |

| C42  | Х   | Х   | Х   | Х   | Х   |     | NoFix | Resume Flag May Not be Cleared After Debug Exception                                                  |  |

| C1AP | Х   | Х   | Х   | Х   | Х   |     | NoFix | APIC access to cacheable memory causes<br>SHUTDOWN                                                    |  |

| C2AP | Х   | Х   | Х   | Х   | Х   |     | NoFix | Write to mask LVT (programmed as EXTINT) will not deassert outstanding interrupt                      |  |

| C3AP | Х   | Х   | Х   | Х   | Х   |     | NoFix | Misaligned locked access to APIC space results in<br>hang                                             |  |

intel

#### INTEL® CELERON™ PROCESSOR SPECIFICATION UPDATE

| NO. | dA0 | dA1 | dB0 | mA0 | mB0 | SUB | Plans | SPECIFICATION CLARIFICATIONS |

|-----|-----|-----|-----|-----|-----|-----|-------|------------------------------|

| C1  | Х   | Х   | Х   | Х   | Х   |     | Doc   | PWRGOOD inactive pulse width |

| NO. | dA0 | dA1 | dB0 | mA0 | mB0 | SUB | Plans | SPECIFICATION CHANGES                  |

|-----|-----|-----|-----|-----|-----|-----|-------|----------------------------------------|

| C1  | Х   | Х   | Х   | Х   | Х   |     | Doc   | Non-GTL+ Output Leakage Current Change |

## intel

## ERRATA

#### C1. FP Data Operand Pointer May Be Incorrectly Calculated After FP Access Which Wraps 64-Kbyte Boundary in 16-Bit Code

**PROBLEM:** The FP Data Operand Pointer is the effective address of the operand associated with the last noncontrol floating-point instruction executed by the machine. If an 80-bit floating-point access (load or store) occurs in a 16-bit mode other than protected mode (in which case the access will produce a segment limit violation), the memory access wraps a 64-Kbyte boundary, and the floating-point environment is subsequently saved, the value contained in the FP Data Operand Pointer may be incorrect.

**IMPLICATION:** A 32-bit operating system running 16-bit floating-point code may encounter this erratum, under the following conditions:

- The operating system is using a segment greater than 64 Kbytes in size.

- An application is running in a 16-bit mode other than protected mode.

- An 80-bit floating-point load or store which wraps the 64-Kbyte boundary is executed.

- The operating system performs a floating-point environment store (FSAVE/FNSAVE/FSTENV/FNSTENV) after the above memory access.

- The operating system uses the value contained in the FP Data Operand Pointer.

Wrapping an 80-bit floating-point load around a segment boundary in this way is not a normal programming practice. Intel has not currently identified any software which exhibits this behavior.

**WORKAROUND:** If the FP Data Operand Pointer is used in an OS which may run 16-bit floating-point code, care must be taken to ensure that no 80-bit floating-point accesses are wrapped around a 64-Kbyte boundary.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

### C2. Differences Exist in Debug Exception Reporting

**PROBLEM:** There exist some differences in the reporting of code and data breakpoint matches between that specified by previous Intel processors' specifications and the behavior of the Pentium II processor, as described below:

#### CASE 1:

The first case is for a breakpoint set on a MOVSS or POPSS instruction, when the instruction following it causes a debug register protection fault (DR7.gd is already set, enabling the fault). The processor reports delayed data breakpoint matches from the MOVSS or POPSS instructions by setting the matching DR6.bi bits, along with the debug register protection fault (DR6.bd). If additional breakpoint faults are matched during the call of the debug fault handler, the processor sets the breakpoint match bits (DR6.bi) to reflect the breakpoints matched by both the MOVSS or POPSS breakpoint and the debug fault handler call. The Pentium II processor only sets DR6.bd in either situation, and does not set any of the DR6.bi bits.

#### CASE 2:

In the second breakpoint reporting failure case, if a MOVSS or POPSS instruction with a data breakpoint is followed by a store to memory which crosses a 4-Kbyte page boundary, the breakpoint information for the MOVSS or POPSS will be lost. Previous processors retain this information across such a page split.

#### CASE 3:

If they occur after a MOVSS or POPSS instruction, the INT *n*, INTO, and INT3 instructions zero the DR6.Bi bits (bits B0 through B3), clearing pending breakpoint information, unlike previous processors.

#### CASE 4:

If a data breakpoint and an SMI (System Management Interrupt) occur simultaneously, the SMI will be serviced via a call to the SMM handler, and the pending breakpoint will be lost.

#### CASE 5:

When an instruction which accesses a debug register is executed, and a breakpoint is encountered on the instruction, the breakpoint is reported twice.

**IMPLICATION:** When debugging or when developing debuggers for an Intel Celeron processor-based system, this behavior should be noted. Normal usage of the MOVSS or POPSS instructions (i.e., following them with a MOV ESP) will not exhibit the behavior of cases 1-3. Debugging in conjunction with SMM will be limited by case 4.

**WORKAROUND:** Following MOVSS and POPSS instructions with a MOV ESP instruction when using breakpoints will avoid the first three cases of this erratum. No workaround has been identified for cases 4 or 5.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C3. Code Fetch Matching Disabled Debug Register May Cause Debug Exception

**PROBLEM:** The bits L0-3 and G0-3 enable breakpoints local to a task and global to all tasks, respectively. If one of these bits is set, a breakpoint is enabled, corresponding to the addresses in the debug registers DR0-DR3. If at least one of these breakpoints is enabled, any of these registers are *disabled* (i.e., Ln and Gn are 0), and RWn for the disabled register is 00 (indicating a breakpoint on instruction execution), normally an instruction fetch will not cause an instruction-breakpoint fault based on a match with the address in the disabled register(s). However, if the address in a disabled register matches the address of a code fetch which also results in a page fault, an instruction-breakpoint fault will occur.

**IMPLICATION:** While debugging software, extraneous instruction-breakpoint faults may be encountered if breakpoint registers are not cleared when they are disabled. Debug software which does not implement a code breakpoint handler will fail, if this occurs. If a handler is present, the fault will be serviced. Mixing data and code may exacerbate this problem by allowing disabled data breakpoint registers to break on an instruction fetch.

WORKAROUND: The debug handler should clear breakpoint registers before they become disabled.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

### C4. FP Inexact-Result Exception Flag May Not Be Set

**PROBLEM:** When the result of a floating-point operation is not exactly representable in the destination format (1/3 in binary form, for example), an inexact-result (precision) exception occurs. When this occurs, the PE bit (bit 5 of the FPU status word) is normally set by the processor. Under certain rare conditions, this bit may not be set when this rounding occurs. However, other actions taken by the processor (invoking the software exception handler if the exception is unmasked) are not affected. This erratum can only occur if the floating-point operation which causes the precision exception is immediately followed by one of the following instructions:

- FST m32real

- FST m64real

- FSTP m32real

- FSTP m64real

- FSTP m80real

- FIST m16int

- FIST m32int

- FISTP m16int

- FISTP m32int

- FISTP m64int

Note that even if this combination of instructions is encountered, there is also a dependency on the internal pipelining and execution state of both instructions in the processor.

**IMPLICATION:** Inexact-result exceptions are commonly masked or ignored by applications, as it happens frequently, and produces a rounded result acceptable to most applications. The PE bit of the FPU status word may not always be set upon receiving an inexact-result exception. Thus, if these exceptions are unmasked, a floating-point error exception handler may not recognize that a precision exception occurred. Note that this is a "sticky" bit, i.e., once set by an inexact-result condition, it remains set until cleared by software.

**WORKAROUND:** This condition can be avoided by inserting two NOP instructions between the two floating-point instructions.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C5. BTM for SMI Will Contain Incorrect FROM EIP

**PROBLEM:** A system management interrupt (SMI) will produce a Branch Trace Message (BTM), if BTMs are enabled. However, the FROM EIP field of the BTM (used to determine the address of the instruction which was being executed when the SMI was serviced) will not have been updated for the SMI, so the field will report the same FROM EIP as the previous BTM.

**IMPLICATION:** A BTM which is issued for an SMI will not contain the correct FROM EIP, limiting the usefulness of BTMs for debugging software in conjunction with System Management Mode (SMM).

WORKAROUND: None identified at this time.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C6. I/O Restart in SMM May Fail After Simultaneous MCE

**PROBLEM:** If an I/O instruction (IN, INS, REP INS, OUT, OUTS, or REP OUTS) is being executed, and if the data for this instruction becomes corrupted, the Intel Celeron processor will signal a machine check exception (MCE). If the instruction is directed at a device which is powered down, the processor may also receive an assertion of SMI#. Since MCEs have higher priority, the processor will call the MCE handler, and the SMI# assertion will remain pending. However, upon attempting to execute the first instruction of the MCE handler, the SMI# will be recognized and the processor will attempt to execute the SMM handler. If the SMM handler is completed successfully, it will attempt to restart the I/O instruction, but will not have the correct machine state, due to the call to the MCE handler.

**IMPLICATION:** A simultaneous MCE and SMI# assertion may occur for one of the I/O instructions above. The SMM handler may attempt to restart such an I/O instruction, but will have corrupted state due to the MCE handler call, leading to failure of the restart and shutdown of the processor.

**WORKAROUND:** If a system implementation must support both SMM and MCEs, the first thing the SMM handler code (when an I/O restart is to be performed) should do is check for a pending MCE. If there is an MCE pending, the SMM handler should immediately exit via an RSM instruction and allow the machine check exception handler to execute. If there is not, the SMM handler may proceed with its normal operation.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

## C7. Branch Traps Do Not Function If BTMs Are Also Enabled

**PROBLEM:** If branch traps or branch trace messages (BTMs) are enabled alone, both function as expected. However, if both are enabled, only the BTMs will function, and the branch traps will be ignored.

**IMPLICATION:** The branch traps and branch trace message debugging features cannot be used together.

WORKAROUND: If branch trap functionality is desired, BTMs must be disabled.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C8. Machine Check Exception Handler May Not Always Execute Successfully

**PROBLEM:** An asynchronous machine check exception (MCE), such as a BINIT# event, which occurs during an access that splits a 4-Kbyte page boundary may leave some internal registers in an indeterminate state. Thus, MCE handler code may not always run successfully if an asynchronous MCE has occurred previously.

**IMPLICATION:** An MCE may not always result in the successful execution of the MCE handler. However, asynchronous MCEs usually occur upon detection of a catastrophic system condition that would also hang the processor. Leaving MCEs disabled will result in the condition which caused the asynchronous MCE instead causing the processor to enter shutdown. Therefore, leaving MCEs disabled may not improve overall system behavior.

**WORKAROUND:** No workaround which would guarantee successful MCE handler execution under this condition has been identified.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

### C9. LBER May Be Corrupted After Some Events

**PROBLEM:** The last branch record (LBR) and the last branch before exception record (LBER) can be used to determine the source and destination information for previous branches or exceptions. The LBR contains the source and destination addresses for the last branch or exception, and the LBER contains similar information for the last branch taken before the last exception. This information is typically used to determine the location of a branch which leads to execution of code which causes an exception. However, after a catastrophic bus condition which results in an assertion of BINIT# and the re-initialization of the buses, the value in the LBER may be corrupted. Also, after either a CALL which results in a fault or a software interrupt, the LBER and LBR will be updated to the same value, when the LBER should not have been updated.

**IMPLICATION:** The LBER and LBR registers are used only for debugging purposes. When this erratum occurs, the LBER will not contain reliable address information. The value of LBER should be used with caution when

debugging branching code; if the values in the LBR and LBER are the same, then the LBER value is incorrect. Also, the value in the LBER should not be relied upon after a BINIT# event.

WORKAROUND: None identified at this time.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C10. BTMs May Be Corrupted During Simultaneous L1 Cache Line Replacement

**PROBLEM:** When Branch Trace Messages (BTMs) are enabled and such a message is generated, the BTM may be corrupted when issued to the bus by the L1 cache if a new line of data is brought into the L1 data cache simultaneously. Though the new line being stored in the L1 cache is stored correctly, and no corruption occurs in the data, the information in the BTM may be incorrect due to the internal collision of the data line and the BTM.

**IMPLICATION:** Although BTMs may not be entirely reliable due to this erratum, the conditions necessary for this boundary condition to occur have only been exhibited during focused simulation testing. Intel has currently not observed this erratum in a system level validation environment.

WORKAROUND: None identified at this time.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

### C11. Potential Early Deassertion of LOCK# During Split-Lock Cycles

**PROBLEM**: During a split-lock cycle there are four bus transactions: 1st ADS# (a partial read), 2nd ADS# (a partial read), 3rd ADS# (a partial write), and the 4th ADS# (a partial write). Due to this erratum, LOCK# may deassert one clock after the 4th ADS# of the split-lock cycle instead of after the 4th RS# assertion corresponding to the 4th ADS# has been sampled. The following sequence of events are required for this erratum to occur:

- 1. A lock cycle occurs (split or nonsplit).

- 2. Five more bus transactions (assertion of ADS#) occur.

- A split-lock cycle occurs and BNR# toggles after the 3rd ADS# (partial write) of the split-lock cycle. This in turn delays the assertion of the 4th ADS# of the split-lock cycle. BNR# toggling at this time could most likely happen when the bus is set for an IOQ depth of 2.

When all of these events occur, LOCK# will be deasserted in the next clock after the 4th ADS# of the split-lock cycle.

**IMPLICATION:** This may affect chipset logic which monitors the behavior of LOCK# deassertion.

WORKAROUND: None identified at this time.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C12. A20M# May Be Inverted After Returning From SMM and Reset

**PROBLEM:** This erratum is seen when software causes the following events to occur:

- 1. The assertion of A20M# in real address mode.

- 2. After entering the 1-Mbyte address wrap-around mode caused by the assertion of A20M#, there is an assertion of SMI# intended to cause a Reset or remove power to the processor. Once in the SMM handler,

software saves the SMM state save map to an area of nonvolatile memory from which it can be restored at some point in the future. Then software asserts RESET# or removes power to the processor.

3. After exiting Reset or completion of power-on, software asserts SMI# again. Once in the SMM handler, it then retrieves the old SMM state save map which was saved in event 2 above and copies it into the current SMM state save map. Software then asserts A20M# and executes the RSM instruction. After exiting the SMM handler, the polarity of A20M# is inverted.

**IMPLICATION:** If this erratum occurs, A20M# will behave with a polarity opposite from what is expected (i.e., the 1-Mbyte address wrap-around mode is enabled when A20M# is deasserted, and does not occur when A20M# is asserted).

**WORKAROUND:** Software should save the A20M# signal state in nonvolatile memory before an assertion of RESET# or a power down condition. After coming out of Reset or at power on, SMI# should be asserted again. During the restoration of the old SMM state save map described in event 3 above, the entire map should be restored, except for bit 5 of the byte at offset 7F18h. This bit should retain the value assigned to it when the SMM state save map was created in event 3. The SMM handler should then restore the original value of the A20M# signal.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

## C13. Reporting of Floating-Point Exception May Be Delayed

**PROBLEM:** The Intel Celeron processor normally reports a floating-point exception for an instruction when the next floating-point or MMX<sup>™</sup> technology instruction is executed. The assertion of FERR# and/or the INT 16 interrupt corresponding to the exception may be delayed until the floating-point or MMX technology instruction *after* the one which is expected to trigger the exception, if the following conditions are met:

- 1. A floating-point instruction causes an exception.

- 2. Before another floating-point or MMX<sup>™</sup> technology instruction, any one of the following occurs:

- a. A subsequent data access occurs to a page which has not been marked as accessed, or

- b. Data is referenced which crosses a page boundary, or

- c. A possible page-fault condition is detected which, when resolved, completes without faulting.

- 3. The instruction causing event 2 above is followed by a MOVQ or MOVD store instruction.

**IMPLICATION:** This erratum only affects software which operates with floating-point exceptions unmasked. Software which requires floating-point exceptions to be visible on the next floating-point or MMX technology instruction, and which uses floating-point calculations on data which is then used for MMX technology instructions, may see a delay in the reporting of a floating-point instruction exception in some cases. Note that mixing floating-point and MMX technology instructions in this way is not recommended.

**WORKAROUND:** Inserting a WAIT or FWAIT instruction (or reading the floating-point status register) between the floating-point instruction and the MOVQ or MOVD instruction will give the expected results. This is already the recommended practice for software.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

### C14. Near CALL to ESP Creates Unexpected EIP Address

**PROBLEM:** As documented, the CALL instruction saves procedure linking information in the procedure stack and jumps to the called procedure specified with the destination (target) operand. The target operand specifies the address of the first instruction in the called procedure. This operand can be an immediate value, a general purpose register, or a memory location. When accessing an absolute address indirectly using the stack pointer

#### INTEL® CELERON™ PROCESSOR SPECIFICATION UPDATE

(ESP) as a base register, the base value used is the value in the ESP register before the instruction executes. However, when accessing an absolute address directly using ESP as the base register, the base value used is the value of ESP *after* the return value is pushed on the stack, not the value in the ESP register *before* the instruction executed.

**IMPLICATION:** Due to this erratum, the processor may transfer control to an unintended address. Results are unpredictable, depending on the particular application, and can range from no effect to the unexpected termination of the application due to an exception. Intel has observed this erratum only in a focused testing environment. Intel has not observed any commercially available operating system, application, or compiler that makes use of or generates this instruction.

**WORKAROUND:** If the other seven general purpose registers are unavailable for use, and it is necessary to do a CALL via the ESP register, first push ESP onto the stack, then perform an *indirect* call using ESP (e.g., CALL [ESP]). The saved version of ESP should be popped off the stack after the call returns.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C15. Built-in Self Test Always Gives Nonzero Result

**PROBLEM:** The Built-in Self Test (BIST) of the Intel Celeron processor does not give a zero result to indicate a passing test. Regardless of pass or fail status, bit 6 of the BIST result in the EAX register after running BIST is set.

**IMPLICATION:** Software which relies on a zero result to indicate a passing BIST will indicate BIST failure.

WORKAROUND: Mask bit 6 of the BIST result register when analyzing BIST results.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C16. THERMTRIP# May Not Be Asserted as Specified

**PROBLEM:** THERMTRIP# is a signal on the Intel Celeron processor which is asserted when the core reaches a critical temperature during operation as detailed in the processor specification. The Intel Celeron processor may not assert THERMTRIP# until a much higher temperature than the one specified is reached.

**IMPLICATION:** The THERMTRIP# feature is not functional on the Intel Celeron processor. Note that this erratum can only occur when the processor is running with a  $T_{PLATE}$  temperature over the maximum specification of 75 °C.

**WORKAROUND:** Avoid operation of the Intel Celeron processor outside of the thermal specifications defined by the processor specifications.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

## C17. Cache State Corruption in the Presence of Page A/D-bit Setting and Snoop Traffic

**PROBLEM:** If an operating system uses the Page Access and/or Dirty bit feature implemented in the Intel architecture and there is a significant amount of snoop traffic on the bus, while the processor is setting the Access and/or Dirty bit the processor may inappropriately change a single L1 cache line to the modified state.

**IMPLICATION:** The occurrence of this erratum may result in cache incoherency, which may cause parity errors, data corruption (with no parity error), unexpected application or operating system termination, or system hangs.

WORKAROUND: It is possible for BIOS code to contain a workaround for this erratum.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C18. Snoop Cycle Generates Spurious Machine Check Exception

**PROBLEM:** The processor may incorrectly generate a Machine Check Exception (MCE) when it processes a snoop access that does not hit the L1 data cache. Due to an internal logic error, this type of snoop cycle may still check data parity on undriven data lines. The processor generates a spurious machine check exception as a result of this unnecessary parity check.

**IMPLICATION:** A spurious machine check exception may result in an unexpected system halt if Machine Check Exception reporting is enabled in the operating system.

**WORKAROUND:** It is possible for BIOS code to contain a workaround for this erratum. This workaround would fix the erratum, however, the reporting of the data parity error will continue.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C19. MOVD/MOVQ Instruction Writes to Memory Prematurely

**PROBLEM:** When an instruction encounters a fault, the faulting instruction should not modify any CPU or system state. However, when the MMX technology store instructions MOVD and MOVQ encounter any of the following events, it is possible for the store to be committed to memory even though it should be canceled:

- 1. If CR0.EM = 1 (Emulation bit), then the store could happen prior to the triggered invalid opcode exception.

- 2. If the floating-point Top-of-Stack (FP TOS) is not zero, then the store could happen prior to executing the processor assist routine that sets the FP TOS to zero.

- 3. If there is an unmasked floating-point exception pending, then the store could happen prior to the triggered unmasked floating-point exception.

- If CR0.TS = 1 (Task Switched bit), then the store could happen prior to the triggered Device Not Available (DNA) exception.

If the MOVD/MOVQ instruction is restarted after handling any of the above events, then the store will be performed again, overwriting with the expected data. The instruction will not be restarted after event 1. The instruction will definitely be restarted after events 2 and 4. The instruction may or may not be restarted after event 3, depending on the specific exception handler.

**IMPLICATION:** This erratum causes unpredictable behavior in an application if MOVD/MOVQ instructions are used to manipulate semaphores for multiprocessor synchronization, or if these MMX instructions are used to write to uncacheable memory or memory mapped I/O that has side effects, e.g., graphics devices. This erratum is completely transparent to all applications that do not have these characteristics. When each of the above conditions are analyzed:

- Setting the CR0.EM bit forces all floating-point/MMX<sup>™</sup> instructions to be handled by software emulation. The MOVD/MOVQ instruction, which is an MMX instruction, would be considered an invalid instruction. Operating systems typically terminates the application after getting the expected invalid opcode fault.

- 2. The FP TOS not equal to 0 case only occurs when the MOVD/MOVQ store is the first MMX instruction in an MMX technology routine and the previous floating-point routine did not clean up the floating-point states properly when it exited. Floating-point routines commonly leave TOS to 0 prior to exiting. For a store to be executed as the first MMX instruction in an MMX technology routine following a floating-point routine, the software would be implementing instruction level intermixing of floating-point and MMX instructions. Intel does not recommend this practice.

#### INTEL® CELERON™ PROCESSOR SPECIFICATION UPDATE

- 3. The unmasked floating-point exception case only occurs if the store is the first MMX technology instruction in an MMX technology routine and the previous floating-point routine exited with an unmasked floating-point exception pending. Again, for a store to be executed as the first MMX instruction in an MMX technology routine following a floating-point routine, the software would be implementing instruction level intermixing of floating-point and MMX instructions. Intel does not recommend this practice.

- 4. Device Not Available (DNA) exceptions occur naturally when a task switch is made between two tasks that use either floating-point instructions and/or MMX instructions. For this erratum, in the event of the DNA exception, data from the prior task may be temporarily stored to the present task's program state.

**WORKAROUND:** Do not use MMX instructions to manipulate semaphores for multiprocessor synchronization. Do not use MOVD/MOVQ instructions to write directly to I/O devices if doing so triggers user visible side effects. An OS can prevent old data from being stored to a new task's program state by cleansing the FPU explicitly after every task switch. Follow Intel's recommended programming paradigms in the *Intel Architecture Developer's Optimization Manual* for writing MMX technology programs. Specifically, do not mix floating-point and MMX instructions. When transitioning to new a MMX technology routine, begin with an instruction that does not depend on the prior state of either the MMX technology registers or the floating-point registers, such as a load or PXOR mm0, mm0. Be sure that the FP TOS is clear before using MMX instructions.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C20. Memory Type Undefined for Nonmemory Operations

**PROBLEM:** The Memory Type field for nonmemory transactions such as I/O and Special Cycles are undefined. Although the Memory Type attribute for nonmemory operations logically should (and usually does) manifest itself as UC, this feature is not designed into the implementation and is therefore inconsistent.

**IMPLICATION:** Bus agents may decode a non-UC memory type for nonmemory bus transactions.

**WORKAROUND:** Bus agents must consider transaction type to determine the validity of the Memory Type field for a transaction.

STATUS: For the steppings affected, see the Summary Table of Changes at the beginning of this section.

### C21. Bus Protocol Conflict With Optimized Chipsets

**PROBLEM:** A "dead" turnaround cycle with no agent driving the address, address parity, request command, or request parity signals must occur between the processor driving these signals and the chipset driving them after asserting BPRI#. The Intel Celeron processor does not follow this protocol. Thus, if a system uses a chipset or third party agent which optimizes its arbitration latency (reducing it to 2 clocks when it observes an active (low) ADS# signal and an inactive (high) LOCK# signal on the same clock that BPRI# is asserted (driven low)), the Intel Celeron processor may cause bus contention during an unlocked bus exchange.

**IMPLICATION:** This violation of the bus exchange protocol when using a reduced arbitration latency may cause a system-level setup timing violation on the address, address parity, request command, or request parity signals on the system bus. This may result in a system hang or assertion of the AERR# signal, causing an attempted corrective action or shutdown of the system, as the system hardware and software dictate. The possibility of failure due to the contention caused by this erratum may be increased due to the processor's internal active pull-up of these signals on the clock after the signals are no longer being driven by the processor.

**WORKAROUND:** If the chipset and third party agents used with the Intel Celeron processor do not optimize their arbitration latency as described above, no action is required. For the 66 MHz Intel Celeron processor, no action is required.

### C22. FP Data Operand Pointer May Not Be Zero After Power On or Reset

**PROBLEM:** The FP Data Operand Pointer, as specified, should be reset to zero upon power on or Reset by the processor. Due to this erratum, the FP Data Operand Pointer may be nonzero after power on or Reset.

**IMPLICATION:** Software which uses the FP Data Operand Pointer and count on its value being zero after power on or Reset without first executing an FINIT/FNINIT instruction will use an incorrect value, resulting in incorrect behavior of the software.

**WORKAROUND:** Software should follow the recommendation in Section 8.2 of the *Intel Architecture Software Developer's Manual, Volume 3: System Programming Guide* (Order Number 243192). This recommendation states that if the FPU will be used, software-initialization code should execute an FINIT/FNINIT instruction following a hardware reset. This will correctly clear the FP Data Operand Pointer to zero.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

## C23. MOVD Following Zeroing Instruction Can Cause Incorrect Result

**PROBLEM:** An incorrect result may be calculated after the following circumstances occur:

- 1. A register has been zeroed with either a SUB reg, reg instruction or an XOR reg, reg instruction,

- 2. A value is moved with sign extension into the same register's lower 16 bits; or a signed integer multiply is performed to the same register's lower 16 bits,

- 3. This register is then copied to an MMX<sup>™</sup> technology register using the MOVD instruction prior to any other operations on the sign-extended value.

Specifically, the sign may be incorrectly extended into bits 16-31 of the MMX technology register. Only the MMX technology register is affected by this erratum.

The erratum only occurs when the 3 following steps occur in the order shown. The erratum may occur with up to 40 intervening instructions that do not modify the sign-extended value between steps 2 and 3.

- XOR EAX, EAX or SUB EAX, EAX

- 2. MOVSX AX, BL

or MOVSX AX, byte ptr <memory address> or MOVSX AX, BX or MOVSX AX, word ptr <memory address> or IMUL BL (AX implicit, opcode F6 /5) or IMUL byte ptr <memory address> (AX implicit, opcode F6 /5) or IMUL AX, BX (opcode 0F AF /r) or IMUL AX, word ptr <memory address> (opcode 0F AF /r) or IMUL AX, BX, 16 (opcode 6B /r ib) or IMUL AX, word ptr <memory address>, 16 (opcode 6B /r ib) or IMUL AX, 8 (opcode 6B /r ib) or IMUL AX, BX, 1024 (opcode 69 /r iw) or IMUL AX, word ptr <memory address>, 1024 (opcode 69 /r iw) or IMUL AX, 1024 (opcode 69 /r iw) or CBW

3. MOVD MM0, EAX

Note that the values for immediate byte/words are merely representative (i.e., 8, 16, 1024) and that any value in the range for the size may be affected. Also, note that this erratum may occur with "EAX" replaced with any 32bit general purpose register, and "AX" with the corresponding 16-bit version of that replacement. "BL" or "BX" can be replaced with any 8-bit or 16-bit general purpose register. The CBW and IMUL (opcode F6 /5) instructions are specific to the EAX register only.

In the example, EAX is forced to contain 0 by the XOR or SUB instructions. Since the four types of the MOVSX or IMUL instructions and the CBW instruction modify only bits 15:8 of EAX by sign extending the lower 8 bits of EAX, bits 31:16 of EAX should always contain 0. This implies that when MOVD copies EAX to MM0, bits 31:16 of MM0 should also be 0. Under certain scenarios, bits 31:16 of MM0 are not 0, but are replicas of bit 15 (the

#### INTEL® CELERON™ PROCESSOR SPECIFICATION UPDATE

16th bit) of AX. This is noticeable when the value in AX after the MOVSX, IMUL or CBW instruction is negative, i.e., bit 15 of AX is a 1.

When AX is positive (bit 15 of AX is a 0), MOVD will always produce the correct answer. If AX is negative (bit 15 of AX is a 1), MOVD may produce the right answer or the wrong answer depending on the point in time when the MOVD instruction is executed in relation to the MOVSX, IMUL or CBW instruction.

**IMPLICATION:** The effect of incorrect execution will vary from unnoticeable, due to the code sequence discarding the incorrect bits, to an application failure. If the MMX technology-enabled application in which MOVD is used to manipulate pixels, it is possible for one or more pixels to exhibit the wrong color or position momentarily. It is also possible for a computational application that uses the MOVD instruction in the manner described above to produce incorrect data. Note that this data may cause an unexpected page fault or general protection fault.

**WORKAROUND:** There are two possible workarounds for this erratum:

- Rather than using the MOVSX-MOVD or CBW-MOVD pairing to handle one variable at a time, use the sign extension capabilities (PSRAW, etc.) within MMX<sup>™</sup> technology for operating on multiple variables. This would result in higher performance as well.

- Insert another operation that modifies or copies the sign-extended value between the MOVSX/IMUL/CBW instruction and the MOVD instruction as in the example below:

XOR EAX, EAX (or SUB EAX, EAX) MOVSX AX, BL (or other MOVSX, other IMUL or CBW instruction) \*MOV EAX, EAX MOVD MM0, EAX

\*Note: MOV EAX, EAX is used here as it is fairly generic. Again, EAX can be any 32-bit register.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C24. Premature Execution of a Load Operation Prior to Exception Handler Invocation

**PROBLEM:** This erratum can occur with any of the following situations:

- 1. If an instruction that performs a memory load causes a code segment limit violation,

- If a waiting floating-point instruction or MMX<sup>™</sup> instruction that performs a memory load has a floating-point exception pending, or

- 3. If an MMX instruction that performs a memory load and has either CR0.EM =1 (Emulation bit set), or a floating-point Top-of-Stack (FP TOS) not equal to 0, or a DNA exception pending.

If any of the above circumstances occur, it is possible that the load portion of the instruction will have executed before the exception handler is entered.

**IMPLICATION:** In normal code execution where the target of the load operation is to write back memory there is no impact from the load being prematurely executed, nor from the restart and subsequent re-execution of that instruction by the exception handler. If the target of the load is to uncached memory that has a system side effect, restarting the instruction may cause unexpected system behavior due to the repetition of the side effect.

**WORKAROUND:** Code which performs loads from memory that has side-effects can effectively workaround this behavior by using simple integer-based load instructions when accessing side-effect memory and by ensuring that all code is written such that a code segment limit violation cannot occur as a part of reading from side-effect memory.

## C25. Read Portion of RMW Instruction May Execute Twice

**PROBLEM:** When the Intel Celeron processor executes a read-modify-write (RMW) arithmetic instruction, with memory as the destination, it is possible for a page fault to occur during the execution of the store on the memory operand after the read operation has completed but before the write operation completes.

If the memory targeted for the instruction is UC (uncached), memory will observe the occurrence of the initial load before the page fault handler and again if the instruction is restarted.

**IMPLICATION:** This erratum has no effect if the memory targeted for the RMW instruction has no side-effects. If, however, the load targets a memory region that has side-effects, multiple occurrences of the initial load may lead to unpredictable system behavior.

**WORKAROUND:** Hardware and software developers who write device drivers for custom hardware that may have a side-effect style of design should use simple loads and simple stores to transfer data to and from the device. Then the memory location will simply be read twice with no additional implications.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C26. Test Pin Must Be High During Power Up

**PROBLEM:** The Intel Celeron processor uses the PWRGOOD signal to ensure that no voltage sequencing issues arise; no pin assertions should cause the processor to change its behavior until this signal is asserted, when all power supplies and clocks to the processor are valid and stable. However, if the TESTHI signal is at a low voltage level when the core power supply comes up, it will cause the processor to enter an invalid test state.

IMPLICATION: If this erratum occurs, the system may boot normally however, L2 cache may not be initialized.

**WORKAROUND:** Ensure that the 2.5 V ( $V_{CC2,5}$ ) power supply ramps at or before the 2.0 V ( $V_{CC_{CORE}}$ ) power plane. If 2.5 V ramps after core, pull up TESTHI to 2.5 V ( $V_{CC2,5}$ ) with a 100K ohm resistor. The internal pull-up will keep the signal from being asserted during power up. For new motherboard designs, it is recommended that TESTHI be pulled up to 2.0 V ( $V_{CC_{CORE}}$ ) using a 1K-10K ohm resistor.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

### C27. Intervening Writeback May Occur During Locked Transaction

**PROBLEM:** During a transaction which has the LOCK# signal asserted (i.e., a locked transaction), there is a potential for an explicit writeback caused by a previous transaction to complete while the bus is locked. The explicit writeback will only be issued by the processor which has locked the bus, and the lock signal will not be deasserted until the locked transaction completes, but the atomicity of a lock may be compromised by this erratum. Note that the explicit writeback is an expected cycle, and no memory ordering violations will occur. This erratum is, however, a violation of the bus lock protocol.

**IMPLICATION:** A chipset or third-party agent (TPA) which tracks bus transactions in such a way that locked transactions may only consist of a read-write or read-read-write-write locked sequence, with no transactions intervening, may lose synchronization of state due to the intervening explicit writeback. Systems using chipsets or TPAs which can accept the intervening transaction will not be affected.

**WORKAROUND:** The bus tracking logic of all devices on the system bus should allow for the occurrence of an intervening transaction during a locked transaction.

#### C28. MC2\_STATUS MSR Has Model-Specific Error Code and Machine Check Architecture Error Code Reversed

**PROBLEM:** The Intel Architecture Software Developer's Manual, Volume 3: System Programming Guide, documents that for the MCi\_STATUS MSR, bits 15:0 contain the MCA (machine-check architecture) error code fields and bits 31:16 contain the model-specific error code field. However, for the MC2\_STATUS MSR, these bits have been reversed. For the MC2\_STATUS MSR, bits 15:0 contain the model-specific error code field and bits 31:16 contain the MC4 error code field.

**IMPLICATION:** A machine check error may be decoded incorrectly if this erratum on the MC2\_STATUS MSR is not taken into account.

WORKAROUND: When decoding the MC2\_STATUS MSR, reverse the two error fields.

**STATUS:** For the steppings affected see the Summary Table of Changes at the beginning of this section.

### C29. MOV With Debug Register Causes Debug Exception

**PROBLEM:** When in V86 mode, if a MOV instruction is executed on debug registers, a general-protection exception (#GP) should be generated, as documented in the *Intel Architecture Software Developer's Manual, Volume 3: System Programming Guide,* Section 14.2. However, in the case when the general detect enable flag (GD) bit is set, the observed behavior is that a debug exception (#DB) is generated instead.

**IMPLICATION:** With debug-register protection enabled (i.e., the GD bit set), when attempting to execute a MOV on debug registers in V86 mode, a debug exception will be generated instead of the expected general-protection fault.

**WORKAROUND:** In general, operating systems do not set the GD bit when they are in V86 mode. The GD bit is generally set and used by debuggers. The debug exception handler should check that the exception did not occur in V86 mode before continuing. If the exception did occur in V86 mode, the exception may be directed to the general-protection exception handler.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

### C30. Upper Four PAT Entries Not Usable With Mode B or Mode C Paging

**PROBLEM:** The Page Attribute Table (PAT) contains eight entries, which must all be initialized and considered when setting up memory types for the Intel Celeron processor. However, in Mode B or Mode C paging, the upper four entries do not function correctly for 4-Kbyte pages. Specifically, bit seven of page table entries that translate addresses to 4-Kbyte pages should be used as the upper bit of a three-bit index to determine the PAT entry that specifies the memory type for the page. When Mode B (CR4.PSE = 1) and/or Mode C (CR4.PAE) are enabled, the processor forces this bit to zero when determining the memory type regardless of the value in the page table entry. The upper four entries of the PAT function correctly for 2-Mbyte and 4-Mbyte large pages (specified by bit 12 of the page directory entry for those translations).

**IMPLICATION:** Only the lower four PAT entries are useful for 4-Kbyte translations when Mode B or C paging is used. In Mode A paging (4-Kbyte pages only), all eight entries may be used. All eight entries may be used for large pages in Mode B or C paging.

WORKAROUND: None identified at this time.

## intel

## C31. Incorrect Memory Type May Be Used When MTRRs Are Disabled

**PROBLEM:** If the Memory Type Range Registers (MTRRs) are disabled without setting the CR0.CD bit to disable caching, and the Page Attribute Table (PAT) entries are left in their default setting, which includes UC- memory type (PCD = 1, PWT = 0; see the Addendum—Intel Architecture Software Developer's Manual, Volume 3: System Programming Guide, for details), data for entries set to UC- will be cached as if the memory type were writeback (WB). Also, if the page tables are set to a memory type other than UC-, then the effective memory type used will be that specified by the page tables and PAT. Any regions of memory normally forced to UC by the MTRRs (such as the VGA video region) may now be incorrectly cached and speculatively accessed.

Even if the CR0.CD bit is correctly set when the MTRRs are disabled and the PAT is left in its default state, then retries and out of order retirement of UC accesses may occur, contrary to the strong ordering expected for these transactions.

**IMPLICATION:** The occurrence of this erratum may result in the use of incorrect data and unpredictable processor behavior when running with the MTRRs disabled. Interaction between the mouse, cursor, and VGA video display leading to video corruption may occur as a symptom of this erratum as well.

**WORKAROUND:** Ensure that when the MTRRs are disabled, the CR0.CD bit is set to disable caching. This recommendation is described in *Intel Architecture Software Developer's Manual, Volume 3: System Programming Guide.* If it is necessary to disable the MTRRs, first clear the PAT register before setting the CR0.CD bit, flushing the caches, and disabling the MTRRs to ensure that UC memory type is always returned and strong ordering is maintained.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C32. Misprediction in Program Flow May Cause Unexpected Instruction Execution

**PROBLEM:** To optimize performance through dynamic execution technology, the P6 architecture has the ability to predict program flow. In the event of a misprediction, the processor will normally clear the incorrect prediction, adjust the EIP to the correct location, and flush out any instructions it may have fetched from the misprediction. In circumstances where a branch misprediction occurs, the correct target of the branch has already been opportunistically fetched into the streaming buffers, and the L2 cycle caused by the evicted cache line is retried by the L2 cache, the processor may fail to flush out the retirement unit before the speculative program flow is committed to a permanent state.

**IMPLICATION:** The results of this erratum may range from no effect to unpredictable application or OS failure. Manifestations of this failure may result in:

- Unexpected values in EIP,

- Faults or traps (e.g., page faults) on instructions that do not normally cause faults,

- Faults in the middle of instructions, or

- Unexplained values in registers/memory at the correct EIP.

**WORKAROUND:** It is possible for BIOS code to contain a workaround for this erratum.

#### C33. Data Breakpoint Exception in a Displacement Relative Near Call May Corrupt EIP

**PROBLEM:** If a data breakpoint is programmed at the memory location where the stack push of a near call is performed, the processor will update the stack and ESP appropriately, but may skip the code at the destination of the call. Hence, program execution will continue with the next instruction immediately following the call, instead of the target of the call.

**IMPLICATION:** The failure mechanism for this erratum is that the call would not be taken; therefore, instructions in the called subroutine would not be executed. As a result, any code relying on the execution of the subroutine will behave unpredictably.

**WORKAROUND:** Do not program a data breakpoint exception on the stack where the push for the near call is performed.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

### C34. System Bus ECC Not Functional With 2:1 Ratio

**PROBLEM:** If a processor is underclocked at a core frequency to system bus frequency ratio of 2:1 and system bus ECC is enabled, the system bus ECC detection and correction will negatively affect internal timing dependencies.

**IMPLICATION:** If system bus ECC is enabled, and the processor is underclocked at a 2:1 ratio, the system may behave unpredictably due to these timing dependencies.

WORKAROUND: All bus agents that support system bus ECC must disable it when a 2:1 ratio is used.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C35. Fault on REP CMPS/SCAS Operation May Cause Incorrect EIP

**PROBLEM:** If either a General Protection Fault, Alignment Check Fault or Machine Check Exception occur during the first iteration of a REP CMPS or a REP SCAS instruction, an incorrect EIP may be pushed onto the stack of the event handler if all the following conditions are true:

- The event occurs on the initial load performed by the instruction(s),

- The condition of the zero flag before the repeat instruction happens to be opposite of the repeat condition (i.e., REP/REPE/REPZ CMPS/SCAS with ZF = 0 or RENE/REPNZ CMPS/SCAS with ZF = 1), and

- The faulting micro-op and a particular micro-op of the REP instruction are retired in the retirement unit in a specific sequence.

The EIP will point to the instruction following the REP CMPS/SCAS instead of pointing to the faulting instruction.

**IMPLICATION:** The result of the incorrect EIP may range from no effect to unexpected application/OS behavior.

WORKAROUND: None identified at this time.

#### C36. RDMSR or WRMSR To Invalid MSR Address May Not Cause GP Fault

**PROBLEM:** The RDMSR and WRMSR instructions allow reading or writing of MSRs (Model Specific Registers) based on the index number placed in ECX. The processor should reject access to any reserved or unimplemented MSRs by generating #GP(0). However, there are some invalid MSR addresses for which the processor will not generate #GP(0).

**IMPLICATION:** For RDMSR, undefined values will be read into EDX:EAX. For WRMSR, undefined processor behavior may result.

WORKAROUND: Do not use invalid MSR addresses with RDMSR or WRMSR.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### C37. SYSENTER/SYSEXIT Instructions Can Implicitly Load "Null Segment Selector" to SS and CS Registers