# intel®

### Pentium<sup>®</sup> II Processor Mobile Module: Embedded Module Connector 2 at 266 MHz (EMC-2) 66-MHz SDRAM DIMM Memory Routing Guidelines

**Application Note**

February 1999

Order Number: 273230-001

## intel

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Pentium<sup>®</sup> II Processor Mobile Module: EMC-2 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled platforms may require licenses from various entities, including Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1999

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Introd            | luction                                                                                                                  | 5        |

|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------|----------|

|     | 1.1<br>1.2<br>1.3 | Key Terms<br>Related Documents<br>66-MHz SDRAM DIMM System Considerations                                                | 5        |

| 2.0 | 66-MH             | Hz SDRAM DIMM Memory Guidelines                                                                                          | 6        |

|     | 2.1               | 66-MHz SDRAM DIMM Interface Overview                                                                                     |          |

|     |                   | <ul> <li>2.1.1 66-MHz SDRAM DIMM Layout Guidelines</li> <li>2.1.2 Design Guidelines</li></ul>                            | 7        |

|     |                   | <ul><li>2.1.3 DIMM Connection - SDRAM</li><li>2.1.4 Trace Lengths for 2-DIMM Design</li></ul>                            | 9        |

|     |                   | 2.1.4.1 Data - MD[63:0], MECC[7:0]<br>2.1.4.2 Data Mask - DQMA[7:0]                                                      | 10       |

|     |                   | 2.1.4.3 Chip Select - CSA[3:0]#<br>2.1.4.4 Clock Enable - CKE[3:0]<br>2.1.4.5 Command - MAB[13:0]x, WEA#, SRASA#, SCASA# | 12       |

| 3.0 | SDRA              | AM Clock Guidelines                                                                                                      | 14       |

|     | 3.1<br>3.2        | Timing Guidelines<br>Clock Layout Guidelines                                                                             | 14<br>14 |

### **Figures**

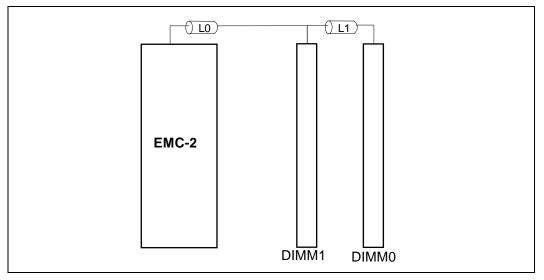

| 1 | SDRAM - 2 DIMM Slots                      | 8   |

|---|-------------------------------------------|-----|

| 2 | MD[63:0], MECC[7:0] Topology              |     |

| 3 | DQMA[7:0] Topology                        |     |

| 4 | CSA[3:0]# Topology                        | .11 |

| 5 | CKE[3:0] Topology                         |     |

| 6 | MAB[13:0]x, WEA#, SRASA#, SCASA# Topology | .13 |

| 7 | SDRAM Clock Timing Specification          | .14 |

| 8 | Clocking Layout Diagram - 66 MHz          |     |

### Tables

| 1  | Related Intel Documents                                         | 5  |

|----|-----------------------------------------------------------------|----|

| 2  | Examples of SDRAM DIMM and SO-DIMM Differences                  |    |

| 3  | SDRAM Connectivity                                              |    |

| 4  | Trace lengths MD[63:0], MECC[7:0]                               |    |

| 5  | Trace Lengths for DQMA[7:0]                                     |    |

| 6  | Trace Lengths for CSA[3:0]#                                     | 11 |

| 7  | Trace Lengths for CKE[3:0]                                      | 12 |

| 8  | Trace Lengths for MAB[13:0]x, WEA#, SRASA#, SCASA#              | 13 |

| 9  | Timing Specifications for Maximum and Minimum SDRAM Clock Skews | 14 |

| 10 | Trace Lengths for SDRAM Clocks and DCLK                         | 15 |

#### 1.0 Introduction

The purpose of this application note is to define the routing guidelines for 66-MHz SDRAM DIMM memory systems in Pentium<sup>®</sup> II Processor Embedded Mobile Module Connector 2 (EMC-2)/Intel 440BX AGPset systems.

*Note:* This document only focuses on a 2-SDRAM DIMM design and is not intended for extended data out (EDO) and on board memory designs.

The routing guidelines are specified in pre-layout simulation results only. Post-layout simulations and post-silicon signal integrity analysis are not available to correlate with the pre-layout simulation results. Therefore, when following these guidelines, it is recommended that the developer simulate these signals for proper signal integrity, flight time and cross talk.

#### 1.1 Key Terms

**EMC-2** refers to the Embedded Module Connector-2. This module is identical to the Intel<sup>®</sup> Pentium II Processor Mobile Module Connector (MMC-2). A complete description of this module is located in the *Intel<sup>®</sup> Pentium<sup>®</sup> II Processor Mobile Module: Mobile Module Connector 2 (MMC-2)* datasheet (http://developer.intel.com/design/mobile/datashts).

**Intel 440BX AGPset** refers to both the 82443BX Host Bridge Controller and the 82371EB PCI ISA IDE Xcelerator. A complete description of this chipset is located in both the *Intel®* 440BX AGPset: 82443BX Host Bridge/Controller datasheet and the 82371AB PCI-TO-ISA/IDE Xcelerator (PIIX4) datasheet (http://developer.intel.com/design/chipsets/datashts).

**SDRAM DIMM** refers to synchronous DRAM dual in-line memory modules.

#### 1.2 Related Documents

#### Table 1. Related Intel Documents

| Document Title                                                                          | Order Number                                     |

|-----------------------------------------------------------------------------------------|--------------------------------------------------|

| 4-Clock 66 MHz 72-Bit ECC Unbuffered SDRAM DIMM Specification, Rev. 1.0                 | Contact your Intel<br>Field Sales Representative |

| 66 MHz Unbuffered SDRAM 64-Bit (Non-ECC/Parity) 144-Pin SO-DIMM Specification, Rev. 1.1 | Contact your Intel<br>Field Sales Representative |

| Intel <sup>®</sup> Pentium <sup>®</sup> II Processor Mobile Module (MMC-2) datasheet    | 243668                                           |

| Mobile Pentium <sup>®</sup> II Processor Specification Update                           | 243887                                           |

| 82371AB PCI-TO-ISA/IDE Xcelerator (PIIX4) datasheet                                     | 290562                                           |

| Intel <sup>®</sup> 440BX AGPset: 82443BX Host Bridge/Controller datasheet               | 290633                                           |

| 82443BX Host Bridge/Controller Electrical and Thermal Specification datasheet addendum  | 273218                                           |

| Intel <sup>®</sup> 440BX AGPset: 82443BX Host Bridge/Controller Specification Update    | 290639                                           |

|                                                                                         | •                                                |

NOTE: Intel's technical documents are available on the Web at: http://developer.intel.com.

#### 1.3 66-MHz SDRAM DIMM System Considerations

A 66-MHz SDRAM DIMM system differs from previous 66-MHz SO-DIMM systems in that there are a few fundamental differences that must be comprehended when designing a system to support 66-MHz SDRAM DIMM operation. For examples of these differences, refer to Table 2. For a complete list of differences, refer to the 4-Clock 66 MHz 72-Bit ECC Unbuffered SDRAM DIMM and the 66 MHz Unbuffered SDRAM 64-Bit (Non-ECC/Parity) 144-Pin SO-DIMM Specifications.

#### Table 2. Examples of SDRAM DIMM and SO-DIMM Differences

|                                   | 66-MHz SDRAM DIMM <sup>†</sup> | 66-MHz SO-DIMM <sup>††</sup> |

|-----------------------------------|--------------------------------|------------------------------|

| Internal Signal<br>Routing Length | 2 – 9 in.                      | 1.2 – 3.94 in.               |

| Clocking                          | 4 Clocks                       | 2 Clock                      |

| DIMM Board<br>Impedence           | 70 Ω ± 15%                     | 55 Ω ± 10%                   |

Refer to the 4-Clock 66 MHz 72-Bit ECC Unbuffered SDRAM DIMM Specification for more information.

†† Refer to the 66 MHz Unbuffered SDRAM 64-Bit (Non-ECC/Parity) 144-Pin SO-DIMM Specification for more information.

#### 2.0 66-MHz SDRAM DIMM Memory Guidelines

This section lists guidelines for routing the signal traces for the board design. The order in which signals are routed will vary from designer to designer. Some designers prefer routing all of the clock signals first, while others prefer routing all of the high speed bus signals first. Either order can be used, as long as the guidelines listed here are followed. Even when these guidelines are followed, it is still highly recommended that the developer simulate these signals for proper signal integrity, flight time and cross talk.

#### 2.1 66-MHz SDRAM DIMM Interface Overview

The 82443BX Host Bridge Controller integrates a main memory DRAM controller that supports a 72-bit SDRAM array for 66-MHz environments. The DRAM controller interface is fully configurable through a set of control registers. A complete description of these registers is provided in the *Intel*<sup>®</sup> 440BX AGPset: 82443BX Host Bridge/Controller datasheet (order number: 290633).

Section 2.1.1 explains the connectivity between the EMC-2 and 66-MHz SDRAM DIMMs. A list of the signal names that are used in the 66-MHz SDRAM DIMM interface are provided in Table 3.

Note: MAB[13,10] are not inverted. These address bits are used to define various SDRAM commands.

#### 2.1.1 66-MHz SDRAM DIMM Layout Guidelines

#### Table 3. SDRAM Connectivity

| 82443BX Pins/Connection            | DIMM Pins                                          | Pin Function                  |  |

|------------------------------------|----------------------------------------------------|-------------------------------|--|

| CKBF buffer outputs DCLK[x:y]      | CK[3:0] (4 DCLKs per DIMM)                         | Clock                         |  |

| CKE[3:0]                           | CKE[1:0]                                           | Clock Enable                  |  |

| CSA#[3:0]                          | S#[1:0] (2 CS per DIMM)<br>S#[3:2] (2 CS per DIMM) | Chip Select                   |  |

| GND                                | A13                                                | Address                       |  |

| MAB10, MAB#[9:0]                   | A[10:0]                                            | Address                       |  |

| MAB#11                             | BA0                                                | Address                       |  |

| MAB#12                             | BA1, A12                                           | Address                       |  |

| MAB13                              | A11                                                | Address                       |  |

| MD[63:0]                           | DQ[63:0]                                           | Data                          |  |

| MECC[7:0]                          | CB[7:0]                                            | Error Checking and Correction |  |

| Strap for SMBus Individual Address | SA[2:0]                                            | SMBus Address                 |  |

| SMBDATA                            | SDA                                                | SMBus Data                    |  |

| SMBCLK                             | SCL                                                | SMBus Clock                   |  |

| SCASA#                             | CAS#                                               | SDRAM Column Address Select   |  |

| SRASA#                             | RAS#                                               | SDRAM Row Address Select      |  |

| WEA#                               | WE0#                                               | Write Enable                  |  |

#### 2.1.2 Design Guidelines

The following guidelines are required for proper connectivity between the EMC-2 and 66-MHz SDRAM DIMMs:

- Some of the pin ranges in Table 3 are dependent upon the DIMM being reviewed; "x" and "y" indicate signal copies.

- The memory data bit traces may be byte-swapped to simplify board routing and minimize trace lengths. This should also be done for the data bits within the byte channel.

- Board impedance should be 55  $\Omega \pm 10\%$ .

- All resistors should be maximum 5% tolerance.

- Populate the furthest DIMM first to avoid stub reflections.

- See the *SDRAM Serial Presence Detect Data Structure* Specification for information on EEPROM register contents (http://developer.intel.com/design/chipsets/memory/ spdsd12a.htm).

#### 2.1.3 DIMM Connection - SDRAM

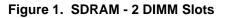

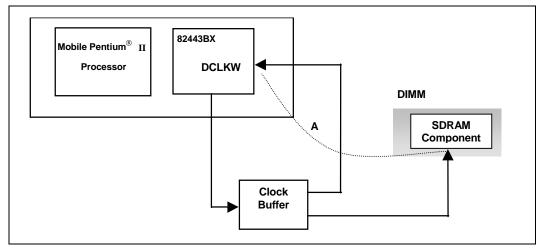

Figure 1 shows the DIMM connections on the system electronics. The guidelines described in this document are based on the assumption that 2-DIMM slots are present on the system electronics.

#### 2.1.4 Trace Lengths for 2-DIMM Design

The following section illustrates signal topology and provides the minimum and maximum trace lengths to the DIMM connector pads for each signal group in a 2-DIMM design.

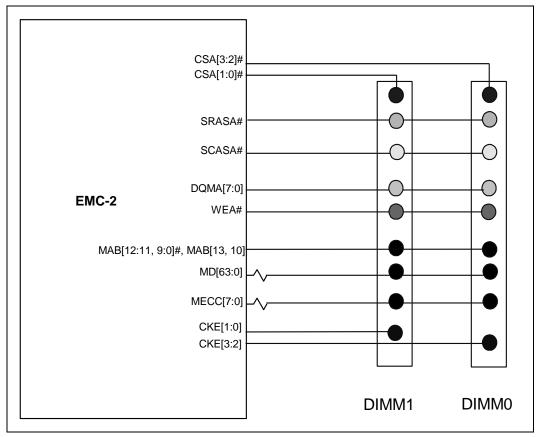

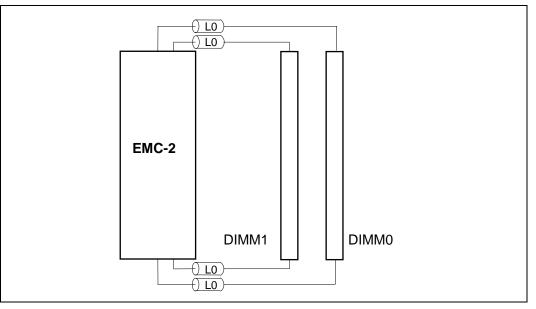

#### 2.1.4.1 Data - MD[63:0], MECC[7:0]

#### Table 4. Trace lengths MD[63:0], MECC[7:0]

| Section  | Minimum | Maximum           |  |

|----------|---------|-------------------|--|

| LO       | n/a     | 1.0 in.           |  |

| L2       | n/a     | 1.0 in.           |  |

| L0+L1+L2 | 1.0 in. | 8.0 in.           |  |

| Series R | n/a     | $18~\Omega\pm5\%$ |  |

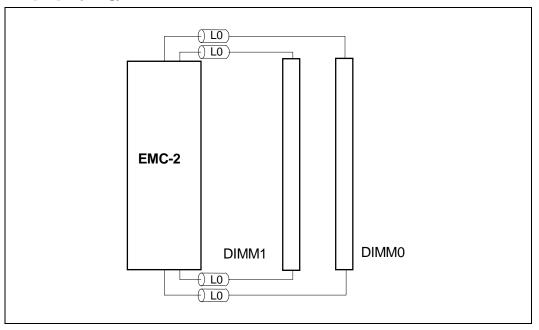

#### 2.1.4.2 Data Mask - DQMA[7:0]

#### Figure 3. DQMA[7:0] Topology

Table 5.

Trace Lengths for DQMA[7:0]

| Section | Minimum | Maximum |

|---------|---------|---------|

| LO      | 1.0 in. | n/a     |

| L1      | n/a     | 1.0 in. |

| L0 + L1 | 1.0 in. | 8 in.   |

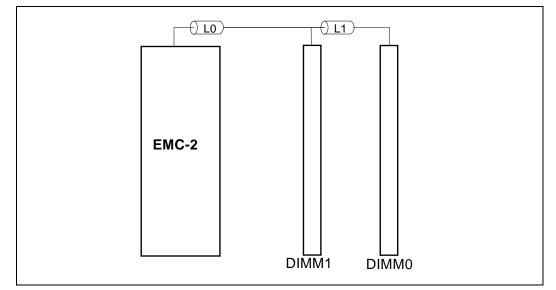

#### 2.1.4.3 Chip Select - CSA[3:0]#

#### Figure 4. CSA[3:0]# Topology

intel®

#### Table 6. Trace Lengths for CSA[3:0]#

| Section | Minimum | Maximum |  |

|---------|---------|---------|--|

| LO      | 1 in.   | 5 in.   |  |

#### 2.1.4.4 Clock Enable - CKE[3:0]

#### Figure 5. CKE[3:0] Topology

#### Table 7. Trace Lengths for CKE[3:0]

| Section | Minimum | Maximum |  |

|---------|---------|---------|--|

| LO      | 1 in.   | 5 in.   |  |

#### 2.1.4.5 Command - MAB[13:0]x, WEA#, SRASA#, SCASA#

#### Figure 6. MAB[13:0]x, WEA#, SRASA#, SCASA# Topology

#### Table 8. Trace Lengths for MAB[13:0]x, WEA#, SRASA#, SCASA#

| Section | Minimum | Maximum |

|---------|---------|---------|

| LO      | 1.0 in. | n/a     |

| L1      | n/a     | 1.0 in. |

| L0 + L1 | 1.0 in. | 8 in.   |

#### 3.0 SDRAM Clock Guidelines

This section defines the clock timing, lengths and series termination for SDRAM-related clocks.

#### 3.1 Timing Guidelines

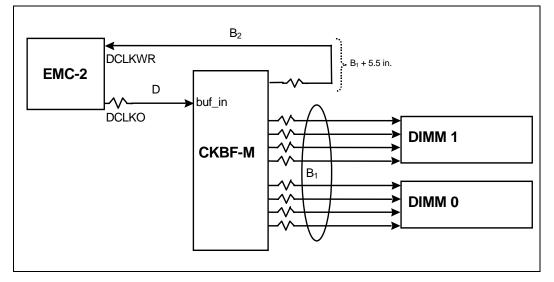

Figure 7 and Table 9 show a simplified SDRAM clock layout for the timing specifications.

*Note:* Even when following the SDRAM clock layout guidelines, it is highly recommended that the developer ensure that the maximum and minimum SDRAM clock skews are within the timing specifications.

Figure 7. SDRAM Clock Timing Specification

Table 9. Timing Specifications for Maximum and Minimum SDRAM Clock Skews

| Symb | ol | Description                    | Ck100-M<br>Pin-to-Pin         | Boards                        | Total                         |

|------|----|--------------------------------|-------------------------------|-------------------------------|-------------------------------|

| A    |    | DCLKWR to<br>SDRAM (SCLK) skew | 250 ps (max)<br>-250 ps (min) | 400 ps (max)<br>-400 ps (min) | 650 ps (max)<br>-650 ps (min) |

#### 3.2 Clock Layout Guidelines

The following guidelines are required for proper clock layout:

- Series matching resistors are required.

- Place as near to the driver pin as possible, less than 1 inch.

- Route all clocks on internal layers to provide better trace delay consistency and EMI containment.

- Set board impedance at 55  $\Omega \pm 10\%$ .

- Minimize the usage of vias in clock signals.

- Set the width to spacing ratio of all clocks to 1:2.

Figure 8. Clocking Layout Diagram - 66 MHz

Table 10. Trace Lengths for SDRAM Clocks and DCLK

| Variable       | Trace<br>Impedence | Trace<br>Length          | Minimum | Maximum | Resistor          |

|----------------|--------------------|--------------------------|---------|---------|-------------------|

| D              | $55~\Omega\pm10\%$ | n/a                      | 0 in.   | 4.0 in. | $18~\Omega\pm5\%$ |

| B <sub>1</sub> | $55~\Omega\pm10\%$ | B <sub>1</sub>           | 0 in.   | 3.0 in. | $8~\Omega\pm5\%$  |

| B <sub>2</sub> | $55~\Omega\pm10\%$ | B <sub>1</sub> + 5.5 in. | 5.5 in. | 8.5 in. | $20~\Omega\pm5\%$ |