AD1812 SoundPort Controller

**Technical Reference**

You may contact the Computer Products Division in the following ways:

- By contacting your local Analog Devices Sales Representative or Authorized Distributor

- For Marketing information, call (617) 461-3881 in Norwood, Massachusetts, USA

- For Applications Engineering information, call (617) 461-3672 in Norwood, Massachusetts, USA ; applications e-mail address is as follows: dsp\_applications@analog.com

- The Norwood office may also be reached by FAX: (617) 461-3010, Telex: 924491, TWX: 710/394-6577, Cables: ANALOG NORWOODMASS

- The Computer Products Division runs a Bulletin Board Service that can be reached at speeds up to 14,400 baud, no parity, 8 bits data, 1 stop bit, by dialing (617) 461-4258. This BBS supports: V.32bis, error correction (V.42 and MNP classes 2, 3, and 4), and data compression (V.42bis and MNP class).

- The Computer Products Division runs an FTP site that can be reached by typing: ftp ftp.analog.com or ftp 137.71.23.21

- By writing to:

Analog Devices Computer Products Division One Technology Way, P.O. Box 9106 Norwood, MA 02062-9106 USA

• The Computer Products Division Technical Publications staff appreciates your comments on this and other product documentation; the publication group's e-mail address is as follows:

dsp\_techpubs@analog.com

AD1812 SoundPort Controller Technical Reference

PRELIMINARY DOCUMENTATION NOTICE: Analog Devices reserves the right to change this product without prior notice. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices.

SoundPort<sup>®</sup> is trademarks of Analog Devices, Inc. Sound Blaster<sup>®</sup> is a registered trademark of Creative Labs, Ltd. MS-DOS<sup>®</sup> and Windows<sup>TM</sup> are trademarks of Microsoft, Inc. MPU-401<sup>®</sup> is a registered trademark of Roland AdLib<sup>TM</sup> is a trademark of AdLib Multimedia

© 1995 Analog Devices, Inc., ALL RIGHTS RESERVED

PRINTED IN USA Second Edition (Latest Revision : October 27, 1995)

## Contents

#### LIST OF FIGURES & TABLES

| CHAPTER 1 INTRODUCTION                                          |      |

|-----------------------------------------------------------------|------|

| 1.1 Overview                                                    |      |

| 1.2 AD1812 System Architecture                                  |      |

| 1.3 AD1812 Development                                          |      |

| 1.4 MANUAL CONVENTIONS                                          |      |

| 1.5 MANUALORGANIZATION                                          |      |

| 1.6 MANUALERRATA                                                |      |

| CHAPTER 2 AD1812 PROGRAMMING                                    |      |

| 2.1 Overview                                                    |      |

| 2.2 AD1812 PLUG & PLAY DEVICE CONFIGURATION                     |      |

| 2.3 AD1812 Non-Plug & Play Device Configuration                 |      |

| 2.4 AD1812 WINDOWS SOUND SYSTEM CODEC PROGRAMMING               |      |

| 2.4.1 Codec Data Formats & Sequencing                           |      |

| 2.4.2 Codec DMA & PIO Data Transfers                            |      |

| 2.4.3 Codec I/O Mixing, Gain, & Attenuation                     |      |

| 2.4.4 Codec Autocalibration                                     |      |

| 2.4.5 Codec Sample Rate Operations                              |      |

| 2.4.6 Codec Powerdown Operations                                |      |

| 2.4.7 Codec Comparison (AD1845 Vs. AD1812's Integrated Codec.)  |      |

| 2.5 AD1812 PROGRAMMINGSUMMARY                                   | 2-44 |

| CHAPTER 3 AD1812 REGISTERS                                      |      |

| 3.1 Overview                                                    |      |

| 3.2 AD1812 PLUG & PLAY AND NON-PLUG & PLAY REGISTERS            |      |

| 3.2.1 Plug & Play And Non-Plug & Play ISA Bus Registers (Ports) |      |

| 3.2.2 Plug & Play And Non-Plug & Play Indexed Registers         |      |

| 3.3 AD1812 WINDOWS SOUND SYSTEM REGISTERS                       |      |

| 3.3.1 Windows Sound System ISA Bus Registers (Ports.)           |      |

| 3.3.2 Windows Sound System Indexed Registers                    |      |

| 3.4 AD1812 Sound Blaster Pro ISA Bus Registers (Ports)          |      |

| 3.5 AD1812 ADLIB ISA BUS REGISTERS (PORTS)                      |      |

| 3.6 AD1812 MIDI MPU-401 ISA B/s Registers (Ports)               |      |

| 3.7 AD1812 GAME PORT                                            |      |

| 3.8 AD1812 Register Summary                                     | 3-64 |

| CHAPTER 4 AD1812 REFERENCE DESIGN                               | 4-65 |

| 4.1 Overview                                                    | 4-65 |

| 4.2 Reference Design Architecture                               |      |

| 4.3 Design Information                                          | 4-68 |

#### INDEX

# List Of Figures & Tables

| FIGURE 1.1 AD1812 SOUNDPORT CONTROLLER BLOCK DIAGRAM                         | 1-1  |

|------------------------------------------------------------------------------|------|

| FIGURE 1.2 AD1812 PC PLUG-IN CARD                                            | 1-3  |

| FIGURE 1.3 AD1812 SOUNDPORT CONTROLLER SYSTEM ARCHITECTURE                   | 1-4  |

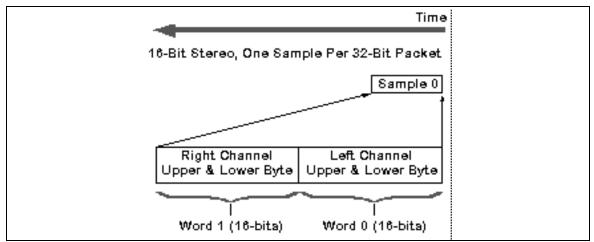

| FIGURE 2.1 STEREO 16-BIT (LINEAR BIG & LITTLE ENDIAN) AUDIO DATA             | 2-25 |

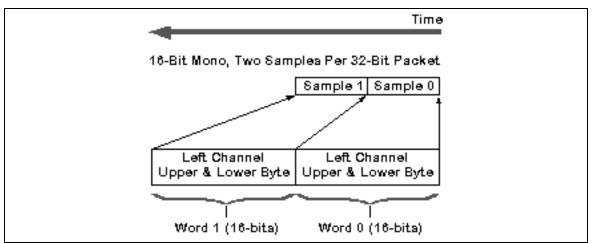

| FIGURE 2.2 MONO 16-BIT (LINEAR BIG & LITTLE ENDIAN) AUDIO DATA               | 2-25 |

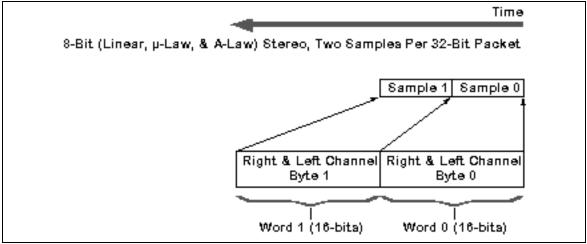

| FIGURE 2.3 STEREO 8-BIT (LINEAR, µ-LAW, & A-LAW) AUDIO DATA                  | 2-25 |

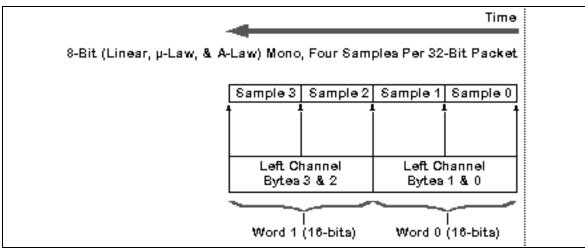

| FIGURE 2.4 MONO 8-BIT (LINEAR, µ-LAW, & A-LAW) AUDIO DATA                    | 2-26 |

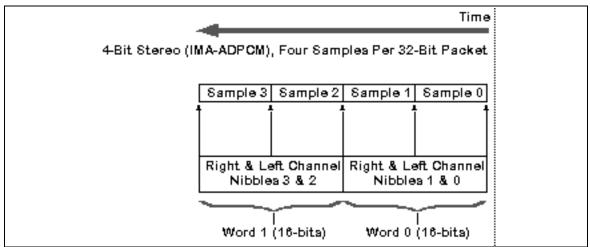

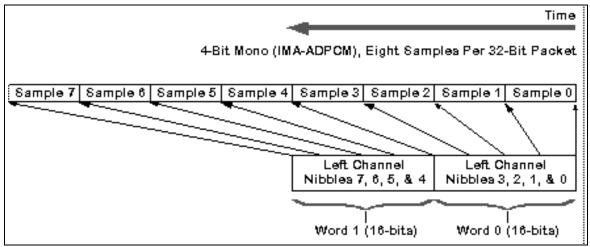

| FIGURE 2.5 MONO 4-BIT (IMA-ADPCM) AUDIO DATA                                 | 2-26 |

| FIGURE 2.6 MONO 4-BIT (IMA-ADPCM) AUDIO DATA                                 | 2-26 |

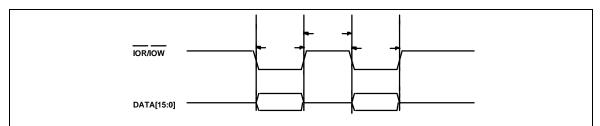

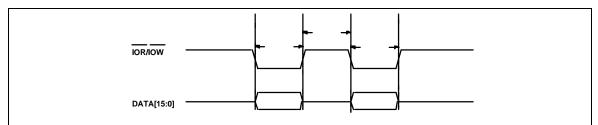

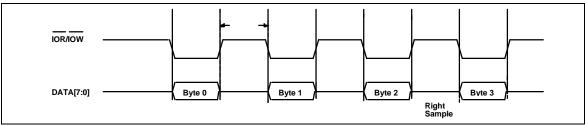

| FIGURE 2.7 CODEC TRANSFERS 16-BIT INTERFACE                                  | 2-27 |

| FIGURE 2.8 CODEC TRANSFERS 16-BIT INTERFACE                                  | 2-29 |

| FIGURE 2.9 CODEC TRANSFERS 8-BIT INTERFACE                                   |      |

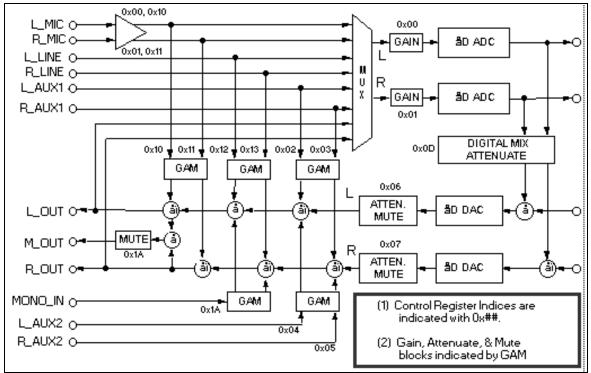

| FIGURE 2.10 MAP OF AD1812 INTEGRATED CODEC (WITH CONTROL REGISTERS)          | 2-36 |

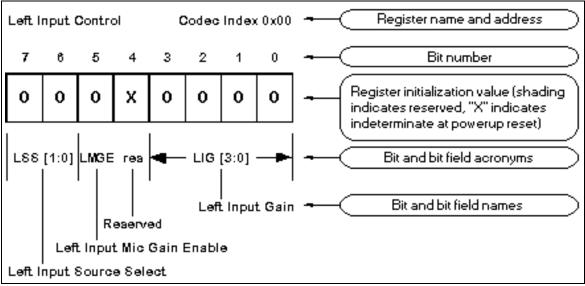

| FIGURE 3.1 REGISTER DIAGRAM EXAMPLE                                          |      |

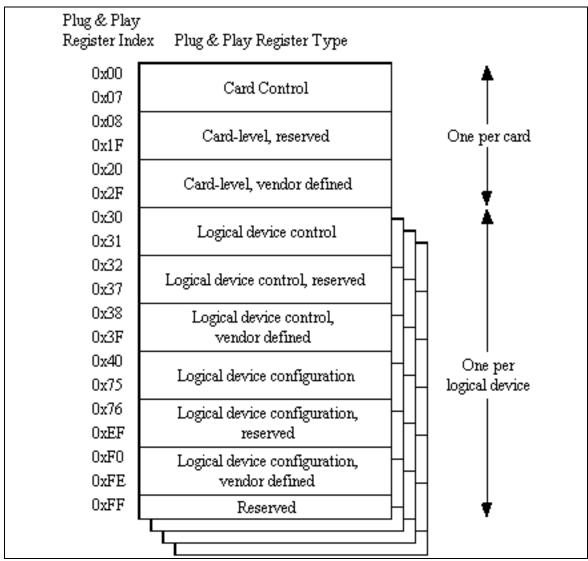

| FIGURE 3.2 AD1812 PLUG & PLAY REGISTER INDEXING                              |      |

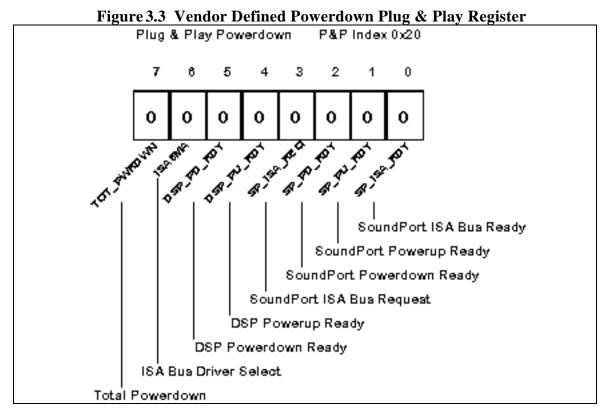

| FIGURE 3.3 VENDOR DEFINED POWERDOWN PLUG & PLAY REGISTER                     |      |

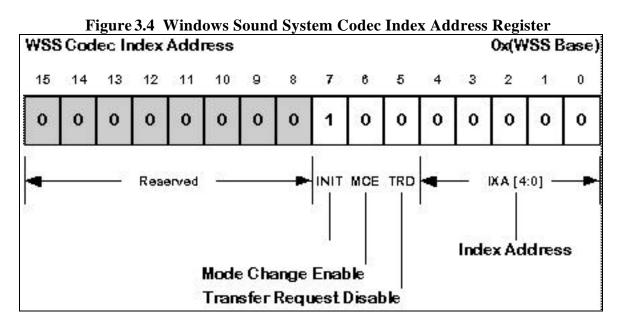

| FIGURE 3.4 WINDOWS SOUND SYSTEM CODEC INDEX ADDRESS REGISTER                 | 3-9  |

| FIGURE 3.5 WINDOWS SOUND SYSTEM CODEC INDEXED DATA REGISTER                  | 3-12 |

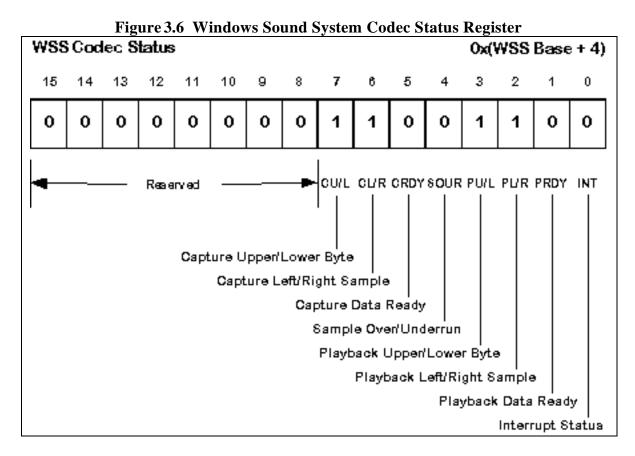

| FIGURE 3.6 WINDOWS SOUND SYSTEM CODEC STATUS REGISTER                        |      |

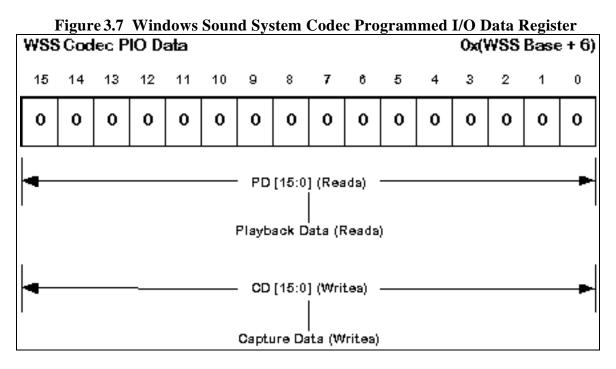

| FIGURE 3.7 WINDOWS SOUND SYSTEM CODEC PROGRAMMEDI/O DATA REGISTER            | 3-16 |

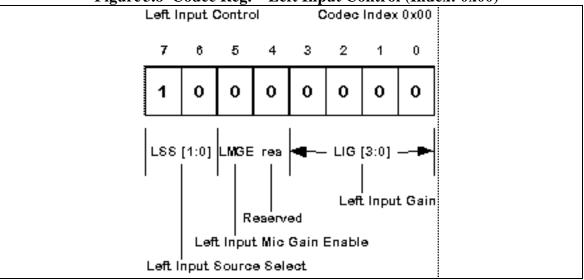

| FIGURE 3.8 CODEC REG.—LEFT INPUT CONTROL (INDEX: 0x00)                       | 3-22 |

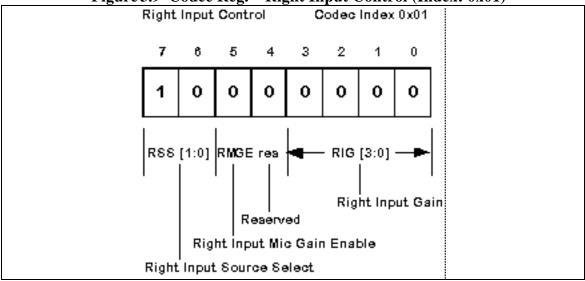

| FIGURE 3.9 CODEC REG.—RIGHT INPUT CONTROL (INDEX: 0x01)                      | 3-23 |

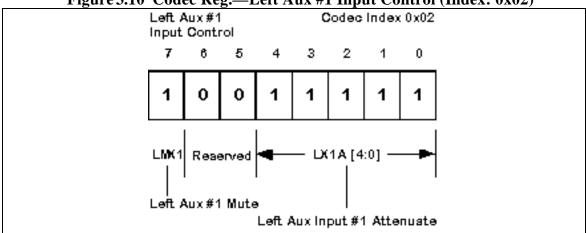

| FIGURE 3.10 CODEC REG.—LEFT AUX #1 INPUT CONTROL (INDEX: 0x02)               | 3-24 |

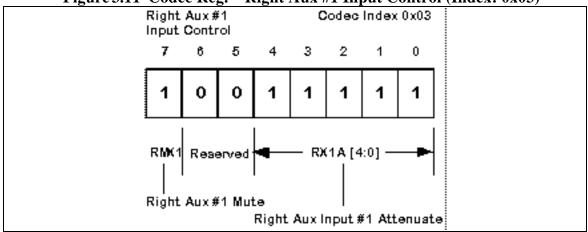

| FIGURE 3.11 CODEC REG.—RIGHT AUX #1 INPUT CONTROL (INDEX: 0x03)              | 3-25 |

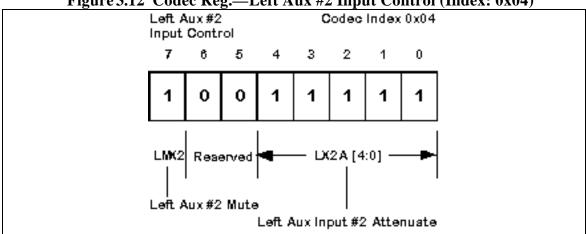

| FIGURE 3.12 CODEC REG.—LEFT AUX #2 INPUT CONTROL (INDEX: 0x04)               | 3-26 |

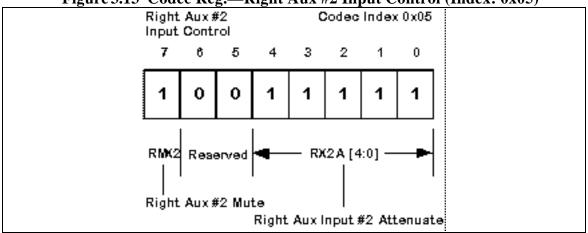

| FIGURE 3.13 CODEC REG.—RIGHT AUX #2 INPUT CONTROL (INDEX: 0x05)              | 3-27 |

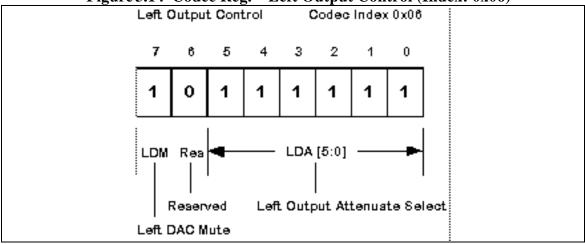

| FIGURE 3.14 CODEC REG.—LEFT OUTPUT CONTROL (INDEX: 0x06)                     | 3-28 |

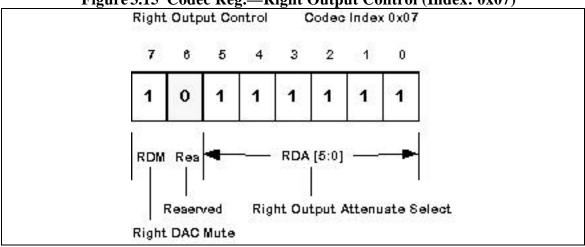

| FIGURE 3.15 CODEC REG.—RIGHT OUTPUT CONTROL (INDEX: 0x07)                    | 3-29 |

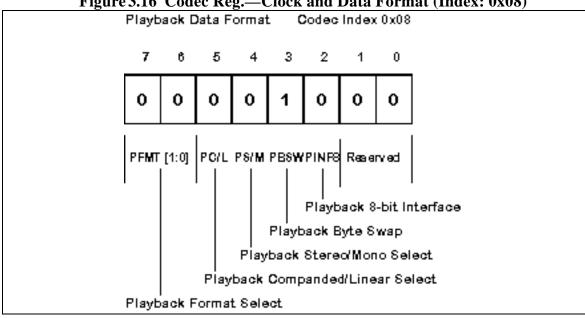

| FIGURE 3.16 CODEC REG.—CLOCK AND DATA FORMAT (INDEX: 0x08)                   |      |

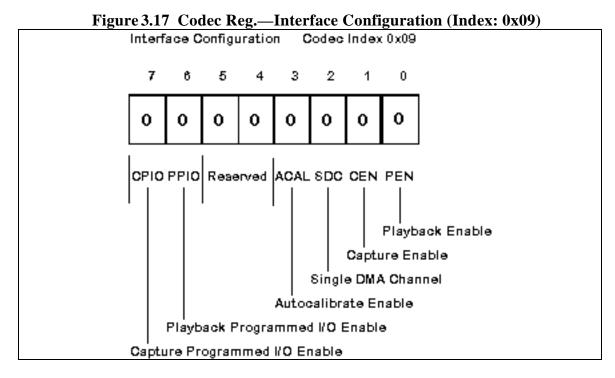

| FIGURE 3.17 CODEC REG.—INTERFACE CONFIGURATION (INDEX: 0x09)                 | 3-32 |

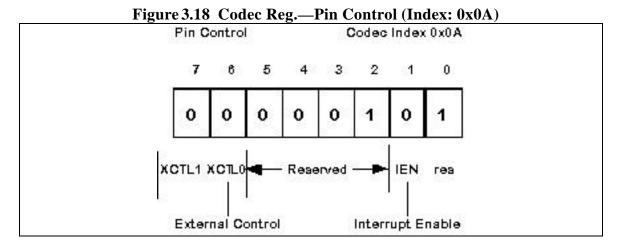

| FIGURE 3.18 CODEC REG.—PIN CONTROL (INDEX: 0x0A)                             | 3-35 |

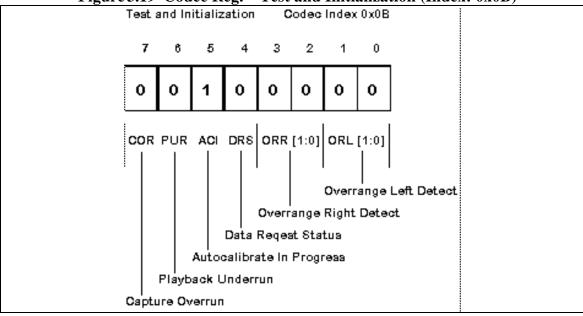

| FIGURE 3.19 CODEC REG.—TEST AND INITIALIZATION (INDEX: 0x0B)                 |      |

| FIGURE 3.20 CODEC REG.—MISCELLANEOUSINFORMATION(INDEX: 0x0C)                 | 3-38 |

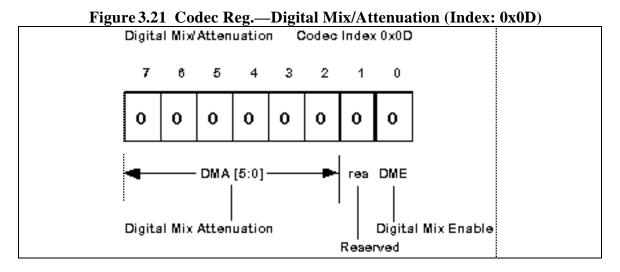

| FIGURE 3.21 CODEC REG.—DIGITAL MIX/ATTENUATION (INDEX: 0x0D)                 | 3-39 |

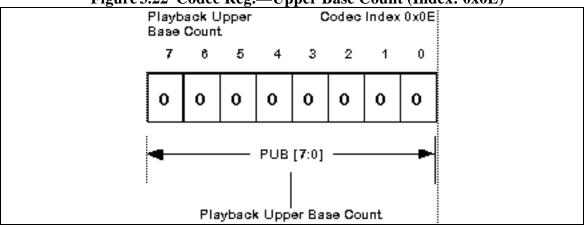

| FIGURE 3.22 CODEC REG.—UPPER BASE COUNT (INDEX: 0x0E)                        | 3-40 |

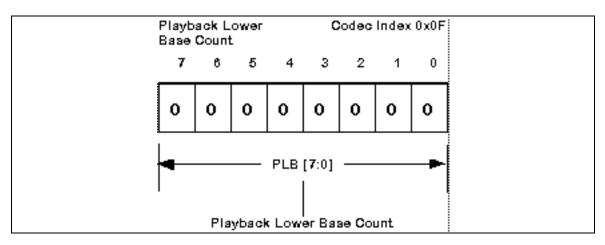

| FIGURE 3.23 CODEC REG.—LOWER BASE COUNT (INDEX: 0x0F)                        | 3-40 |

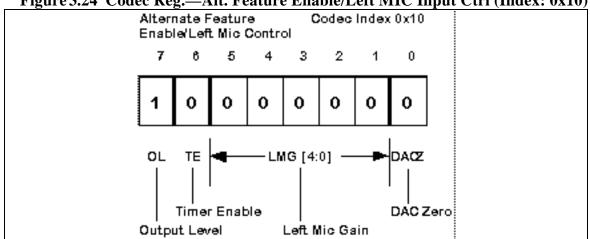

| FIGURE 3.24 CODEC REG.—ALT. FEATURE ENABLE/LEFT MIC INPUT CTRL (INDEX: 0x10) |      |

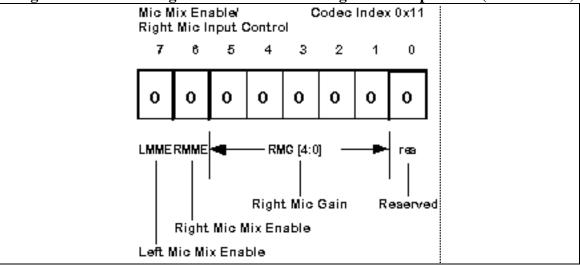

| FIGURE 3.25 CODEC REG.—MIC MIX ENABLE/RIGHT MIC INPUT CTRL (INDEX: 0x11)     | 3-43 |

| FIGURE 3.26 CODEC REG.—LEFT LINE GAIN, ATTENUATE, MUTE, MIX (INDEX: 0x12)    | 3-45 |

| FIGURE 3.27 CODEC REG.—RIGHT LINE GAIN, ATTENUATE, MUTE, MIX (INDEX: 0x13)   | 3-46 |

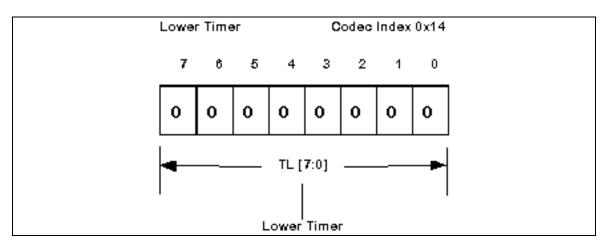

| FIGURE 3.28 CODEC REG.—LOWER TIMER (INDEX: 0x14)                             | 3-47 |

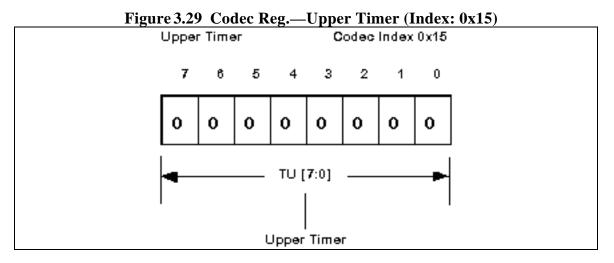

| FIGURE 3.29 CODEC REG.—UPPER TIMER (INDEX: 0x15)                             |      |

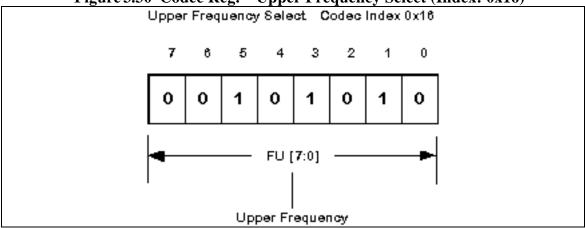

| FIGURE 3.30 CODEC REG.—UPPER FREQUENCY SELECT (INDEX: 0x16)                  | 3-49 |

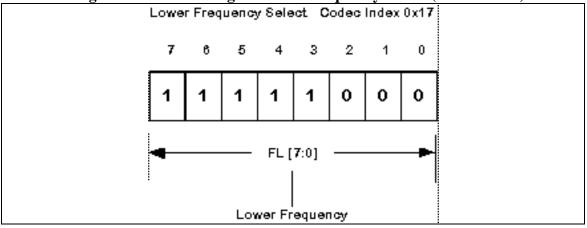

| FIGURE 3.31 CODEC REG.—LOWER FREQUENCY SELECT (INDEX: 0x17)                  |      |

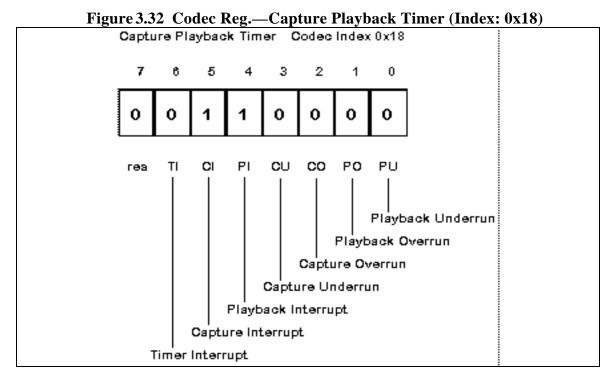

| FIGURE 3.32 CODEC REG.—CAPTURE PLAYBACK TIMER (INDEX: 0x18)                  |      |

| FIGURE 3.33 CODEC REG.—REVISION ID (INDEX: 0x19)                             |      |

| FIGURE 3.34 CODEC REG.—MONO CONTROL (INDEX: 0x1A)                            |      |

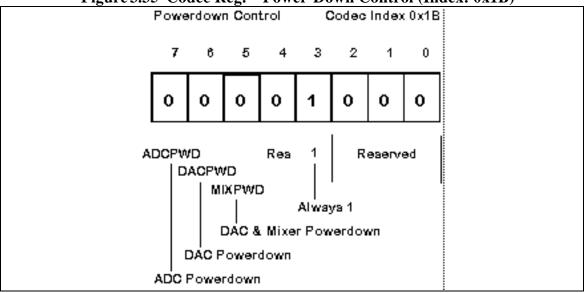

| FIGURE 3.35 CODEC REG.—POWER-DOWN CONTROL (INDEX: 0x1B)                      |      |

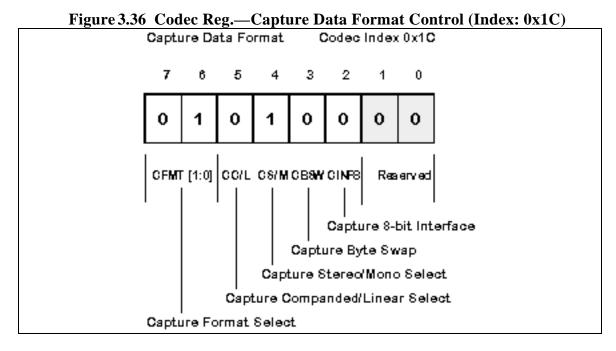

| FIGURE 3.36 CODEC REG.—CAPTURE DATA FORMAT CONTROL (INDEX: 0x1C)             | 3-56 |

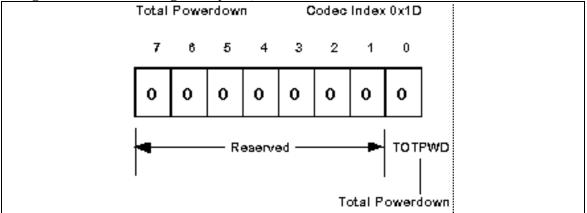

| FIGURE 3.37 CODEC REG.—CRYSTAL, CLOCK SELECT/TOTAL POWER-DOWN (INDEX: 0x1D)       | 3-58 |

|-----------------------------------------------------------------------------------|------|

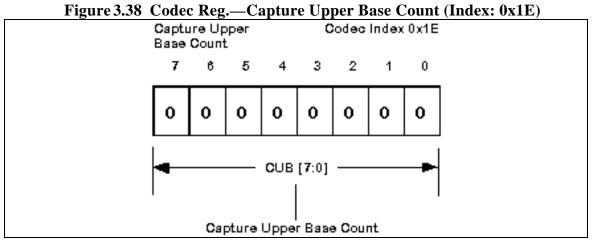

| FIGURE 3.38 CODEC REG.—CAPTURE UPPER BASE COUNT (INDEX: 0x1E)                     | 3-59 |

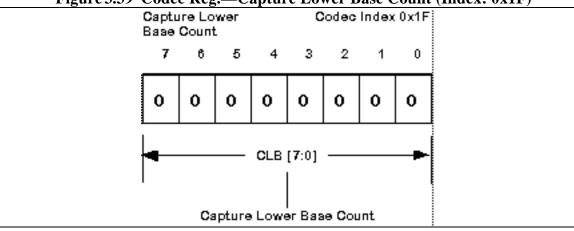

| FIGURE 3.39 CODEC REG.—CAPTURE LOWER BASE COUNT (INDEX: 0x1F)                     | 3-59 |

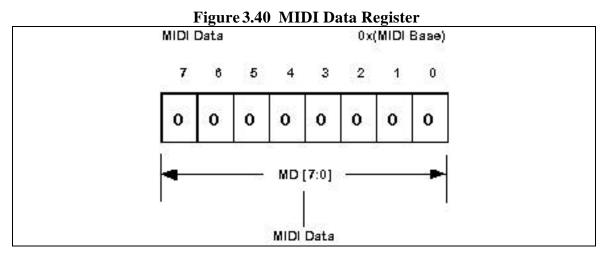

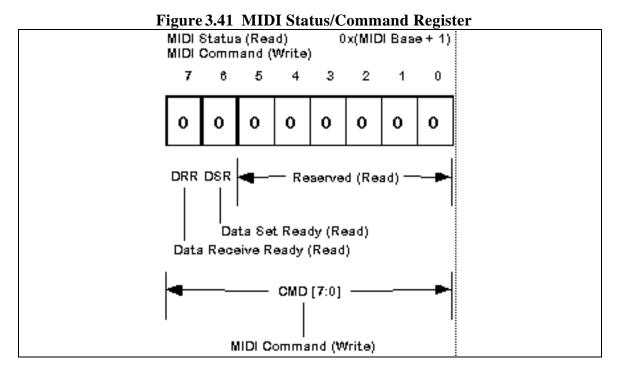

| FIGURE 3.40 MIDI DATA REGISTER                                                    | 3-62 |

| FIGURE 3.41 MIDI STATUS/COMMAND REGISTER                                          | 3-63 |

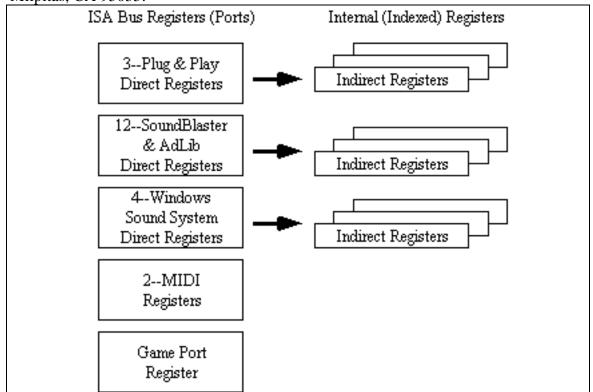

| FIGURE 3.42 REGISTER OVERVIEW                                                     | 3-64 |

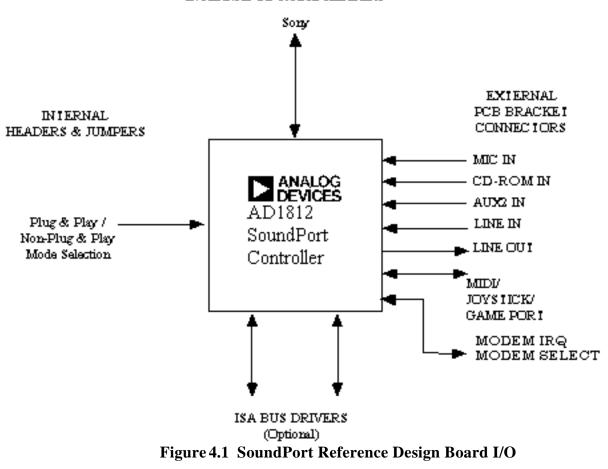

| FIGURE 4.1 SOUNDPORT REFERENCE DESIGN BOARD I/O                                   | 4-66 |

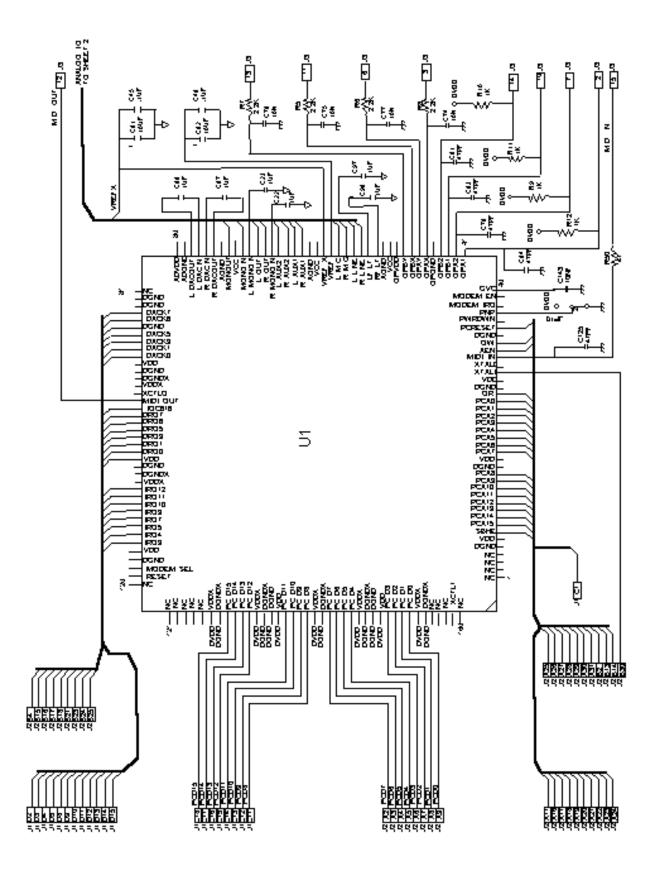

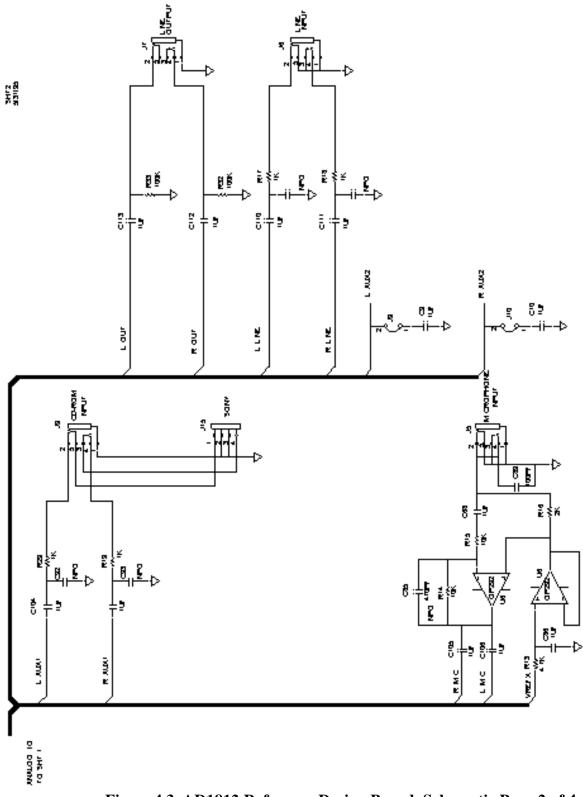

| FIGURE 4.2 AD1812 REFERENCE DESIGN BOARD, SCHEMATIC PAGE 1 OF 4                   | 4-69 |

| FIGURE 4.3 AD1812 REFERENCE DESIGN BOARD, SCHEMATIC PAGE 2 OF 4                   | 4-70 |

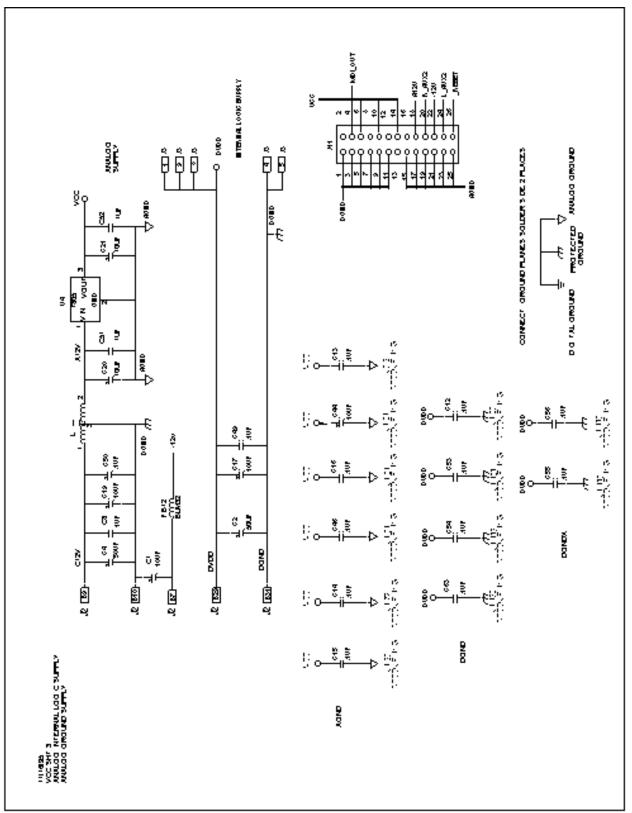

| FIGURE 4.4 1812 REFERENCE DESIGN BOARD, SCHEMATIC PAGE 3 OF 4                     | 4-71 |

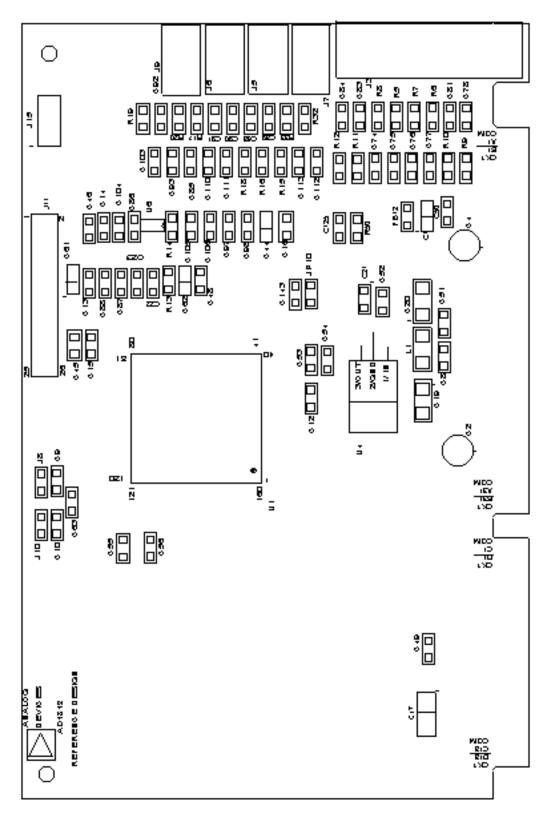

| FIGURE 4.5 AD1812 REFERENCE DESIGN BOARD, COMPONENT SIDE SILK-SCREEN              |      |

|                                                                                   |      |

| TABLE 1.1       AD1812       SoundPort Controller Features                        | 1-3  |

| TABLE 1.2    MANUAL TEXT & SYMBOL CONVENTIONS.                                    | 1-8  |

| TABLE 2.1 AD1812 LOGICAL DEVICES AND COMPATIBLE PLUG & PLAY DEVICE DRIVERS        | 2-3  |

| TABLE 2.2       PLUG & PLAY ISA BUS REGISTERS (PNP PIN ASSERTED)                  | 2-4  |

| TABLE 2.3 PLUG & PLAY AD1812 LOGICAL DEVICES-DESCRIPTORS-CONFIGURATIONS           | 2-5  |

| TABLE 2.4 NON-PLUG & PLAY ISA BUS REGISTERS (PNP PIN DE-ASSERTED)                 | 2-10 |

| TABLE 2.5 NON-PLUG & PLAY AD1812 ADDRESS REGISTER VALUES                          |      |

| TABLE 2.6 NON-PLUG & PLAY AD1812 ADDRESS REGISTER VALUES (WINDOWS SOUND SYSTEM,   |      |

| LDN==0)                                                                           | 2-12 |

| TABLE 2.7 NON-PLUG & PLAY AD1812 ADDRESS REGISTER VALUES (SOUND BLASTER, LDN==1)  | 2-15 |

| TABLE 2.8 NON-PLUG & PLAY AD1812 ADDRESS REGISTER VALUES (ADLIB MUSIC SYNTHESIS,  |      |

| LDN==2)                                                                           | 2-16 |

| TABLE 2.9 NON-PLUG & PLAY AD1812 ADDRESS REGISTER VALUES (MIDI, LDN==3)           | 2-17 |

| TABLE 2.10 NON-PLUG & PLAY AD1812 ADDRESS REGISTER VALUES (GAME PORT, LDN==4)     | 2-19 |

| TABLE 2.11 NON-PLUG & PLAY AD1812 ADDRESS REGISTER VALUES (MODEM, LDN==5)         | 2-20 |

| TABLE 2.12 CODEC TRANSFERS 16-BIT INTERFACE, NO BYTE SWAP (P/CINF8=0, P/CBSW=0)   | 2-27 |

| TABLE 2.13 CODEC TRANSFERS 16-BIT INTERFACE, WITH BYTE SWAP (P/CINF8=0, P/CBSW=1) | 2-29 |

| TABLE 2.14       CODEC TRANSFERS8-BIT INTERFACE (P/CINF8=1)                       | 2-31 |

| TABLE 2.15    POWERDOWN BITS (PLUG & PLAY VERSUS CODEC)                           | 2-40 |

| TABLE 2.16    POWER DOWN MODE SUMMARY                                             | 2-41 |

| TABLE 2.17 COMPARISON OF AD1845 Vs. AD1812'S CODEC                                | 2-42 |

| TABLE 3.1    MAP OF AD1812 ISA Bus Registers.                                     | 3-2  |

| TABLE 3.2       PLUG & PLAY ISA BUS REGISTERS (PNP PIN ASSERTED)                  |      |

| TABLE 3.3 NON-PLUG & PLAY ISA BUS REGISTERS (PNP PIN DE-ASSERTED)                 | 3-3  |

| TABLE 3.4       MAP OF AD1812       PLUG & PLAY—INDEXED REGISTERS                 |      |

| TABLE 3.5    MAP OF WINDOWS SOUND SYSTEM REGISTER BITS                            | 3-8  |

| TABLE 3.6       MAP OF AD1812       WINDOWS SOUND SYSTEM CODEC—INDEXED REGISTERS  | 3-18 |

| TABLE 3.7       MAP OF WINDOW SOUND SYSTEM INDEXED REGISTER BITS                  | 3-20 |

| TABLE 3.8    Sound Blaster Pro ISA Bus Registers                                  | 3-60 |

| TABLE 3.9    ADLIB ISA BUS REGISTERS                                              | 3-61 |

| TABLE 3.10   MIDI ISA Bus Registers                                               |      |

| TABLE 3.11    GAME PORT ISA BUS REGISTER (PORT)                                   | 3-64 |

### 1.1 Overview

The purpose of the AD1812 SoundPort Controller User's Manual is to provide an audience of programmers, engineers, and OEMs with the information required to program the chip, design PC motherboards (and plug-in boards) using the chip, and manufacture AD1812 based boards.

The AD1812 SoundPort Controller integratescodec, synthesis, and bus interface functions into a single chip audio sub-system — adding lessost 16-bit stereo audio to any ISA busequippedPC. Motherboard or PC plug-in designs using the AD1812 are compatible with virtually all applications written to measure Blaster® Pro, Ad Lib<sup>TM</sup>, MIDI MPU-401, Windows 95®, and the Microsof® Windows<sup>TM</sup> Sound System standards.

Figure 1.1 AD1812 SoundPort Controller Block Diagram

Figure 1.1 shows the AD1812 audio sub-system combines following components

- ADSP-2171 DSP with RAM & ROM

- AD1845 SoundPortStereo Codec

- Plug & Play Compatible ISA Bus Interface

This combinationprovides five Plug & Playlogical devices:

- Windows Sound System Code(application-level compatible)

- Sound BlasterPro (register level compatible

- AdLib (OPL-3 FM parameter compatible usic synthesize)

- MIDI MPU-401 Port

- Game/Joystick Port

- Modem

The AD1812 contains a register set that corresponds to those used for bound Blaster Pro Windows Sound System, MIDI MPU-401, Game/Joystick Port, and Plug Play Configuration.

All logical devices in the AD1812 are compliant with the Intel/Microsoft Plug & Play Specification.Devices (Windows Sound System, MIDI, etc. ...) are automatically configured at system start. Through the Plug & Play mechanism, the operating system can reconfigure the AD1812, avoiding conflicts with other hardware devices AD1812 also can be programmed in a non-Plug & Play environment.

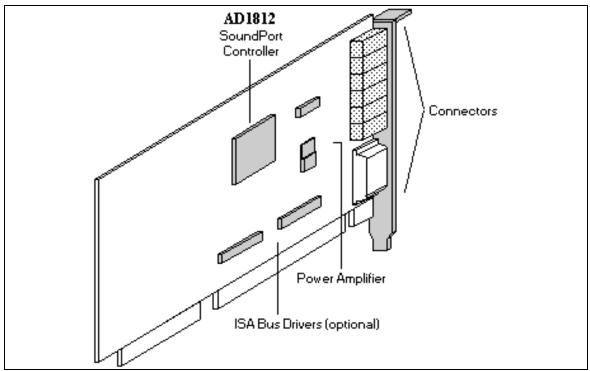

The PC plug-in cardshown in Figure 1.2illustrates how few additional components are needed to build an AD1812 board. Only a power Amp and a few discrete components are needed to build an AD1812 plug-in card — even fewer are required to add an AD1812 to a motherboard design.Table 1.1 contains a summary of the controller's features.

| • | Single-Chip Integration      | - | 16-bit Stereo Codec                                       |

|---|------------------------------|---|-----------------------------------------------------------|

|   |                              | - | Music Synthesizer                                         |

|   |                              | - | 16-bit ISA Bus Interface                                  |

|   |                              | - | Power Management                                          |

|   |                              | - | Game Port                                                 |

| • | Industry StandardsCompliance | - | Sound BlasterPro <sup>TM</sup>                            |

|   |                              | - | Microsoft <sup>®</sup> Windows <sup>TM</sup> Sound System |

|   |                              | - | General MIDI & MPU-401                                    |

|   |                              | - | Plug & Play Configurable                                  |

| • | Available Software Support   | - | Microsoft <sup>®</sup> Windows <sup>TM</sup> 3.1 Drivers  |

|   |                              | - | Microsoft <sup>®</sup> Windows <sup>TM</sup> 95 Drivers   |

|   |                              | - | Windows <sup>TM</sup> Control & Diagnostic Applets        |

| • | Integrated Codec Advantages  | - | Full-Duplex Operation                                     |

|   | -                            | - | DynamicSample Rate Variation from kHz                     |

|   |                              |   | to 50 kHz (in 1 Hz increments)                            |

## 1.2 AD1812 System Architecture

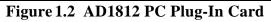

As shown in Figure 1.3, the AD1812 SoundPort Controller's architecture connects a set of Plug & Play logical devices to the PC ISA bus. These devices include a Sound Blaster Pro compatible device (SB), an AdLib compatible device (ADLIB), a Windows Sound System device (WSS), a MIDI MPU-401 compatible device (MIDI), and a Game Port device (GAME). The AD 1812 also provides a Plug and Play ISA bus interface for an external modem chipset. To provide these devices, theoSindPort Controller's architecture combines a codec, digital signal processor, and **m** ISA bus interface **m** a single chip.

The AD1812's PC ISA bus interface (INTERFACE) connects the DOS games register set, Windows Sound System register setand music synthesis hardware to the ISA bus using a fully compatible Plug& Play (PnP) configurationinterface. Hardware support in the AD1812 includes address decoding for on-hip devices control & signal interpretation, DMA selection& control logic, IRQ selection& control logic, and interface configuration logic.

- The three functional units (Codec, DSP, & Interface) that make up the AD1812 controller have the following architectural features.

- Codec

A modified AD1845 stereo-audio 16-bi  $\Delta$  codec is integrated into the AD1812 controller. This codec provides support for business audio and multi-media applications withstereo audio converters, completeon-chip filtering(some external capacitors required) MPC Level-2 compliant analog mixing, programmable gas attenuation, a variable sample attenuator, and FIFO buffers.

The codec's architecture includes a stereo pair of  $\Sigma \Delta$  analog-to-digital converters (ADC) and a stereo pair of  $\Sigma \Delta$  digital-to-analog converters(DAC). You can select inputs to the ADC from four stereo pairs of analog signals: line (LINE), microphone (MIC), auxiliary line #1 (AUX1), and post-mixed DAC outpuAn analog mixerlets you mixmono (MONO\_IN), MIC, AUX1, LINE and auxiliary line #2 (AUX2) nputs with the DACs' output. Independent gain for each channel going into the ADIS available through  $\infty$ oftware-controlled programmable gain stageThis architecture also lets you digitallymix the ADCs' output with the DACs' inputAlso, the codec includes avariable samplerate frequency generatorthat lets you instantaneously change the codec's sample rate with a resolution of 1 HzCreating audio special effects (like Doppler-effect bullet-shots) without any clicks or pops is easy with this feature. The codec uses the variable sampler rate frequency generator to derive all internal clocks from a single, 14.31818 MHz clock input.

The integrated codec supports a DMA request/grant (or a Programmed I/O mode) architecture for transferring dataon the ISA bus. Dual DMA count registers in the AD1812 provide for fullduplex operation, enabling simultaneous capture and playback on separate DMA channel 8 or 16-bit).

• DSP

An ADSP-2171 Digital Signal Processor (DSP with internal ROM & RAM) is integrated into the AD1812 controller. Softwareunning on this internal signal processor provides sound effects and music synthesis by emulating the responses of the Yamaha YM262 (OPL-3)FM synthesis chip. Using this technique, the internal signal processor delivers 20voice, 11-note polyphony Music synthesized on the signal processor is converted on an additional pair of  $\Delta$  DACs and sent to the analog mixer on the codec.

• Interface

An ESC615 ISA bus interface chip (with added Plug & Play interface) is integrated into the AD1812 controller. This interface'architecture also supports Sound Blaster Pro DMA transfers (separate channel from codec).

The controller's interface complies with the Intel/Microsoft Plug & Play specification, making all onchip features automatically configurable. For compatibility withon-Plug & Play systems, you can disable the Plug & Play protocoland use a non-Plug & Play software configuration utility. In either case, the controller is completely software configurable. To provide Sound Blaster Pro, AdLib, and MIDI MPU-401 support, the interface includes registers that emulate those used by these devices.

These three architectural components (Codec, DSP, & Interface) are combined in the controller to support a broad range of PC audio conversion operations. An AD1812 based system can do the following audio operations simultaneously:

- Synthesize music and sound effects for games

- Convert compressed digital wave files into analog wave forms

- Digitize, format, and compress analog signals

- Receive and transmit MIDI MPU-401 UART information

- Communicate with an IBM compatible joystick

## 1.3 AD1812 Development

Virtually all applications developed for Sound Blaster, Windows Sound System, AdLib, and MIDI MPU-401 platforms run on the AD1812 SoundPort Controller. Follow the same development process for the controller as you would use for these other devices. This section provides information on related development kitsardware/software specifications, and reference texts.

For information on AD1812 signal timing, mechanical, and electrical specifications, see the Analog Devices:

• AD1812 SoundPort Controller Data Sheet

As the AD1812 contains Sound Blaster (compatible) and Windows Sound System logical devices, you may find the following related development kits useful when developing AD1812 applications.

- *Developer Kit for Sound Blaster Series*2nd ed. ©1993, Creative LabsInc., 1901 McCarthy Blvd., Milpitas, CA 95035

- *Microsoft Windows Sound System Driver Development Kit (CD*)Version 2.0, ©1993, Microsoft Corp., One Microsoft Way, Redmond, WA 98052

Because the AD1812 complies with the following related specificationy ou can use them as an additional reference to AD1812 operations beyond the material in this manual.

- *Plug & Play ISA Specification Version 1.0a*, ©1993,1994, Intel Corp. & Microsoft Corp., One Microsoft Way, Redmond, WA 98052

- *Multimedia PC Level 2 Specification*©1993, Multimedia PC Marketing Council, 1730 M St. NW, Suite 707, Washington, DC 20036

- *MIDI 1.0 Detailed Specification& Standard MIDI Files 1.Q* ©1994, MIDI Manufacturers Association, PO Box 3173 La Habra, CA 90632-3173

- Recommendation G.711—Pulse Code Modulation (PCM) Of Voice Frequenciep-Law & A-LawCompanding, The International Telegraph and Telephone Consultative Committee IX Plenary Assembly Blue Book, Volume III - Fascicle III.4, General Aspects Of Digital Transmission Systems; Terminal Equipments, Recommendations G.700 - G.795, (Geneva, 1988), ISBN 92-61-03341-5

- *IMA Digital Audio Doc-Pac*(IMA-ADPCM), ©1992, Interactive Multimedia Association, 48 Maryland Avenue, Suite 202, Annapolis, MD 21401-8011

The following reference texts an serve as additional sources of information on developing applications that run on the AD1812.

- S. De Furia & J. Scacciaferro, *The MIDI Implementation Book* (©1986, Third Earth, Pompton Lake)

- C. Petzold, *Programming Windows the Microsoft guide to writing applications for Windows 3.1*, 3rd. ed. (©1992, Microsoft Press, Redmond)

- K. Pohlmann, Principles of Digital Audia (©1989, Sams, Indianapolis)

- A. Stolz, *The Sound Blaster Book* (©1993, Abacaus, Grand Rapids)

- J. Strawn, Digital Audio Engineering An Anthology, (©1985, Kaufmann, Los Altos)

- T. Yamamoto, *MIDI Guidebook*, 4th. ed., (©1987, 1989, Roland Corp., Japan)

## 1.4 Manual Conventions

Table 1.2 lists the text and layout conventions used in this manual. In addition to the conventions shown, please note the following euphemisms and acronyms

- *Sound Blaster, Sound Blaster Prq AdLib,* and *Music Synthesis* refer to DSP-based emulation of these devices through a combination of DSP software and dedicated hardware.

- *Windows Sound System Codec*refers to a modified AD1845 Codec integrated into the AD1812 SoundPort Controller that (with custom driver software) supports Windows Sound System applications.

- *DSP* stands for Digital Signal Processor.

| Item             | Convention (how shown or used)                                                                                                                        |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Trademarks:      | Registered trademarks ( <sup>®</sup> ) and trademarks ( <sup>TM</sup> ) used in this document are <i>honored</i> in the front matter of this document |  |

| Registers:       | Registers are documented with a labeled figure and a bit definition table                                                                             |  |

| Bits:            | Bits are indicated as part of a range of bits from upper bit to lower bit, [15:0] indicates bits 15 through 0.                                        |  |

| Decimal base     | Decimal basenumbers are shown without a prefix: 2050                                                                                                  |  |

| Hexadecimal base | Hexadecimal base numbers are shown with a 0x prefix: 0x000F                                                                                           |  |

| Binary base      | Binary base numbers are shown with a 0b prefix: 0b1010,1010                                                                                           |  |

| Addresses:       | Addresses are shown as a hexadecimal numbers: 0x201                                                                                                   |  |

| (PC and AD1812)  | (Text with address indicates the type of address)                                                                                                     |  |

| Bold Text:       | Bold text is used to indicatevery important text                                                                                                      |  |

| Italic Text:     | Italic text is used to indicate important text                                                                                                        |  |

| Courier Text:    | Courier text is used to indicateprogram listings                                                                                                      |  |

| Tables:          | Tables are shown in grid boxes with title at top                                                                                                      |  |

| Figures:         | Figures are shown in a box with title at bottom                                                                                                       |  |

| Note:            | Notes indicate information crucial to step, operation, or options                                                                                     |  |

| Caution:         | Cautions indicate information crucial to avoiding component damag                                                                                     |  |

| Footnote:        | Footnotes indicate information that is not required to operate the part but can be of some assistance                                                 |  |

Table 1.2 Manual Text & Symbol Conventions

## 1.5 Manual Organization

This manual documents the AD1812 SoundPort Controller. Areas of particular interest to programmers and designers include the following:

- Chapter 2 AD1812 Programming

The programming reference provides an overview of AD1812 programming, lists Plug & Play resource data for the AD1812's built-in logical devices, and describes how to configure/program the AD1812 when it is in non-Plug & Play mode. Also, this chapter includes descriptions of Windows Sound System Codec programming.

- Chapter 3 AD1812 Registers

The register reference provides an overview of AD1812 registers with a map of all

AD1812 registers and describes each register in detail. The manual presents register's

descriptions in functional groupsRlug & Play, Windows Sound System, Sound

Blaster Pro, MIDI, AdLib, and Game Port)

- Chapter 4 AD1812 Reference Design The design reference provides specifications for producing an AD1812-based PC plugin card. These specifications include a functional overview, an architectural description, and board schematics.

## 1.6 Manual Errata

This is the second edition of the AD1812 SoundPort Controller Technical Reference. Errata in this manual is documented on the Computer Products Division Bulletin Board Service which can be reached at speeds up to 14,400 baud, no parity, 8 bits data, 1 stop bit, dialing (617) 461-4258. This BBS supports: V.32bis, error correction (V.42 and MNP classes 2, 3, and 4), and data compression (V.42bis and MNP class).

### 2.1 Overview

Programming the AD1812 SoundPort Controller consists of setting the controller's configuration and programming the controller's logical devices (Windows Sound System, Sound Blaster, AdLib, MIDI MPU-401, modem, and Game Port). This chapter describes AD1812 Plug & Play mode configuration data, non-Plug & Play mode configuration process, and procedures for programming the integrated Windows Sound System codec.

For information on the Plug & Play mode configuration process, see t**Re**ug & Play ISA Specification Version 1.0a (May 5, 1994)All the AD1812's logical devices comply with Plug & Play resource definitions described in the specification.

For information on vendor specific Plug & Play registers and all Windows Sound System codec registers, see Chapter 3*AD1812 Registers*

The next several sections use Plug & Play related terminology describe configuration and programming topics. Definitions of terms are as follows:

- *Plug & Play Logical Devices*—Devices that meet the Plug & Play specification for runtime configuration in an ISA bus PC.

- *System Boot*—Steps a PC system goes through at power up (BIOS, POST, & BOOT)

- *System Resources*—Standard PC system resources (i.e. I/O addresses, interrupt channels, and DMA channels)

- *Plug & Play Resource ROM*—Read-Only-Memory in the AD1812 containing a list of possible resource settings for the orchip logical devices.

- *Plug & Play Device IDs*—Product identifier that the system uses to find and start corresponding Plug & Play device drivers.

- *Plug & Play Resource Manager*–PC system software (Plug & Play BIOS or after Boot Plug & Play System Support) that provides runtime system configuration services.

- Active Plug & Play Devices—Active logical devices respond to all ISA bus cycles as per its normal operation. Inactive logical devices doot respond to nor drive any ISA bus signals.

- *Dependent functions*—Encoded interdependent options within a logical device's configuration resource data. The Plug & Play system software weighs these options, when configuring the system, to achieve the highest rating. Device configurations involving dependent functions can have the following ratings:

- A) *Good Plug & Play Configuration*—Configuration that best serves the software using the device

- B) Acceptable Plug & Play Configuration—Configuration that satisfactorily serves the software using the device

- C) *Sub-optimal Plug & Play Configuration* Configuration that barely serves the software using the device

Note: The *Good*, *Acceptable*, and *Sub-optimal* ratings of dependent function configurations come from a variety of sources (i.e. most commonly recognizable I/O base addresses for devices, most useful DMA channel assignments, etc. ...). Not all devices have what could be considered*Good* configurations, but all devices do hav*Acceptable* configurations.

## 2.2 AD1812 Plug & Play Device Configuration

The operating system configures/re-configures AD1812 Plug & Play Logical Devices after system boot<sup>\*</sup>. To complete this configuration, the system reads resource data from the AD1812's on-chip resource ROM and from any other Plug & Play cards in the system, then arbitrates the configuration of system resources with a heuristic algorithm. The algorithm maximizes the number of *ctive* devices and the *acceptability* of their configurations.

The system considers all Plug & Play logical device resource data at the same time and makes a conflict-free assignment of resources to the devices. If the system cannot assign a conflict-free resource to a device, the system does not configure or activate the device. All configured devices are activated.

The system's Plug & Play support selects all necessary drivers, starts them, and outputs a list of system resources allocated to each logical device. Optionally, you can re-assign system resources at runtime with a Plug & Play Resource Manager. The custom setup created using the manager can be saved and used automatically on following system boots.

There are no "boot-devices" among the Plug & Play Logical Devices in the AD1812. Non-Plug & Play BIOS systems configure the AD1812's Logical Devices after boot using drivers. Depending on BIOS implementations, Plug & Play BIOS systemsnay configure the AD1812's Logical Devices before POST or after Boot. See the Plug & Play ISA Specification Version 1.0 dor more information on configuration control.

Plug & Play Device IDs(embedded in the logical device's resource data) provide the system with the information required to find and load the correct device drivers. In one case, a custom driver is required; the AD1812 Window Sound System driver from Analog Devices is required for correct operation. In all other cases (Sound Blaster, AdLib, MIDI, Game Port and modem), the Analog Devices custom driver is preferred, but the system can use generic drivers (that ship with all Plug & Play systems) if the custom driver is unavailable. Table 2.1 lists the AD1812's logical devices and compatible Plug & Play device drivers.

| Device Name         | ADI (Device ID) & Driver                                  | Compatible (Device ID) &                               |

|---------------------|-----------------------------------------------------------|--------------------------------------------------------|

|                     | Name                                                      | Driver Name                                            |

| Window Sound System | (ADS7140)                                                 | (None)                                                 |

|                     | ADS7140 Windows Sound<br>System                           | None                                                   |

| Sound Blaster Pro   | (ADS7141)                                                 | (PNPB002)                                              |

| (Compatible)        | ADS7141 Sound Blaster Pro                                 | PNPB002 Sound Blaster Pro                              |

| AdLib(Compatible)   | (ADS7142)                                                 | (PNPB020)                                              |

|                     | ADS7142 Yamaha OPL3-<br>compatible FM synthesis<br>device | PNPB020 Yamaha OPL3-<br>compatible FM synthesis device |

| MIDI (Compatible)   | (ADS7143)                                                 | (PNPB006)                                              |

|                     | ADS7143 MPU401 compatible                                 | PNPB006 MPU401 compatible                              |

| Game Port           | (ADS7144)                                                 | (PNPB02F)                                              |

|                     | ADS7144 Joystick/Game port                                | PNPB02F Joystick/Game port                             |

| Modem               | (ADS7145)                                                 | (PNP0501)                                              |

|                     | ADS7145 Modem                                             | PNP0501 Compatible COM port                            |

Table 2.1 AD1812 Logical Devices And Compatible Plug & Play Device Drivers

When the AD1812's PnP pin is asserted, the chip is in Plug & Play mode configuration process for the logical devices on the AD1812 is described in the g & *Play ISA Specification Version 1.0a (May 5, 1994)*The specification describes how to transfer the logical devices from their startu Wait For Keystate to the Config state and how to assign I/O ranges, interrupt channels, and DMA channels.

Tables 2.2 and 2.3 list the Plug & Play ISA bus registers and configuration data for the AD1812 in Plug & Play mode. The resource data presented in these tables corresponds to data described in the AD1812 Resource ROM.

| Table 2.2 Thug & Thay 1511 Dus Register of Int philasserieu) |                                       |            |  |

|--------------------------------------------------------------|---------------------------------------|------------|--|

| Port Name                                                    | ISA Address                           | Туре       |  |

| ADDRESS                                                      | 0x279 (Printer status port)           | Write-only |  |

| WRITE_DATA                                                   | 0xA79 (Printer status port + 0x800)   | Write-only |  |

| READ_DATA                                                    | Relocatable in range<br>0x203 - 0x3FF | Read-only  |  |

Table 2.2 Plug & Play ISA Bus Registers(PnP pin asserted)

| Device                                 | Descriptor                                          | Configuration                                                                                                                                                                                                                                                                     |

|----------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Windows<br>Sound<br>System<br>(LDN==0) | I/O Port<br>Address<br>Descriptor 0<br>(0x60-0x61)  | The Windows Sound System address range is from 0x0008 to 0xFFF8 The most commonly used address is 0x530. The range is 8 bytes long and must be aligned to an 8 byte memory boundary.                                                                                              |

|                                        | Interrupt<br>Request<br>Level<br>Select 0<br>(0x70) | The Windows Sound System requires one of the following IRQ channels: 3, 4, 5, 7, 9, 10, 11, or 12.                                                                                                                                                                                |

|                                        | DMA<br>Channel                                      | The Windows Sound System equires one or two DMA channels. Possible configurations are as follows:                                                                                                                                                                                 |

|                                        | Select 0 (0x74),                                    | <i>Two 16-bit DMA channels</i> selected from channels 5, 6, or 7. This is the Plug & Play <i>Good</i> configuration.                                                                                                                                                              |

|                                        | DMA<br>Channel<br>Select 1                          | <i>One 16-bit DMA playbackchannel and one 8-bit DMA capture channel</i> , selected from 16-bit channels 5, 6, or 7 and 8-bit channels 0, 1, or 3. This is a Plug & Play <i>Acceptable</i> configuration.                                                                          |

|                                        | (0x75)                                              | <i>Two 8-bit DMA channels</i> selected from channels 0, 1, or 3. This is a Plug & PlayAcceptable configuration.                                                                                                                                                                   |

|                                        |                                                     | One 16-bit DMA channel selected from channels 5, 6, or<br>7. Because the channel is shared for capture and playback<br>operations, simultaneous playback and capture <b>is</b> ot<br>possible in this configuration. This a Plug & Play<br>Sub-optimal configuration.             |

|                                        |                                                     | <i>One 8-bit DMA channel</i> selected from channels 0, 1, or 3.<br>Because the channel is shared for capture and playback<br>operations, simultaneous playback and capture <i>isot</i><br>possible in this configuration. This a Plug & Play<br><i>Sub-optimal</i> configuration. |

Table 2.3 Plug & Play AD1812 Logical Devices-Descriptors-Configurations

## Table 2.3 Plug & Play AD1812 Logical Devices-Descriptors-Configurations (continued)

| (continued)                                |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|--------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Device                                     | Descriptor                                          | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Sound<br>Blaster<br>Compatible<br>(LDN==1) | I/O Port<br>Address<br>Descriptor 0<br>(0x60-0x61)  | The Sound Blaster address range is from 0x010 to 0x3F0.<br>The range is 16 bytes long and must be aligned to a 16<br>byte memory boundary.<br>In Plug & Play terms, a Sound Blaster Configuration that<br>has a base address of 0x300 or 0x330 is Acceptable. The<br>configuration is Sub-optimal if using an address between<br>0x010 to 0x3F0 (other than 0x220 or 0x240) because most<br>games will not recognize these non-standard ports. |  |

|                                            | Interrupt<br>Request<br>Level<br>Select 0<br>(0x70) | The Sound Blaster requires one of the following IRQ channels: 3, 4, 5, 7, 9, 10, 11, or 12.                                                                                                                                                                                                                                                                                                                                                    |  |

|                                            | DMA<br>Channel<br>Select 0<br>(0x74)                | The Sound Blaster requires one 8-bit DMA channel.<br>Possible choices are (0,1,3).                                                                                                                                                                                                                                                                                                                                                             |  |

| AdLib<br>(LDN==2)                          | I/O Port<br>Address<br>Descriptor 0<br>(0x60-0x61)  | The AdLib address range is from 0x008 to 0x3F8. The range is 4 bytes long and must be aligned to an 8 byte memory boundary.<br>In Plug & Play terms, an AdLib Configuration that has a base address of 0x388 is Acceptable. The configuration is Sub-optimal if using an address between 0x008 to 0x3F8 (other than 0x388) because most games will not recognize these non-standard ports.                                                     |  |

| Table 2.3 | <b>B Plug &amp; Play</b> | AD1812 Logical Devices-Descriptors-Configurations |

|-----------|--------------------------|---------------------------------------------------|

|           |                          | (continued)                                       |

|           |                          |                                                   |

| Device                      | Descriptor                                          | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIDI<br>MPU-401<br>(LDN==3) | I/O Port<br>Address<br>Descriptor 0<br>(0x60-0x61)  | The MIDI address range is from 0x008 to 0x3F8. The range is 4 bytes long and must be aligned to a 16 byte memory boundary.<br>In Plug & Play terms, a MIDI Configuration that has a base address of 0x300 or 0x330 is Acceptable. The configuration is Sub-optimal if using an address between 0x010 to 0x3F0 (other than 0x300 or 0x330) because most serial devices will not recognize these non-standard ports.                                                                                                                     |

|                             | Interrupt<br>Request<br>Level<br>Select 0<br>(0x70) | The MIDI requires one of the following IRQ channels: 3, 4, 5, 7, 9, 10, 11, or 12.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Game Port<br>(LDN==4)       | I/O Port<br>Address<br>Descriptor 0<br>(0x60-0x61)  | The Game Port address range is from 0x001 to 0x3FF. The range is 1 byte long. In Plug & Play terms, a Game Port Configuration that has a base address of 0x201 is <i>Acceptable</i> . The configuration is <i>Sub-optimal</i> if using an address between 0x001 to 0x3FF (other than 0x201) because most games will not recognize these non-standard ports.                                                                                                                                                                            |

| Modem<br>(LDN==5)           | I/O Port<br>Address<br>Descriptor 0<br>(0x60-0x61)  | The Modem device address range is from 0x008 to 0x3F8.<br>The range is 8 bytes long and must be aligned to an eight<br>byte memory boundary. In Plug & Play terms, a Modem<br>Configuration that has a base address of 0x3F8 (with<br>IRQ4), 0x2F8 (with IRQ3), 0x3E8 (with IRQ4), or 0x2E8<br>(with IRQ3) is <i>Acceptable</i> . The configuration is<br><i>Sub-optimal</i> if using an address between 0x008 to 0x3F8<br>(other than above combinations) because most serial<br>devices will not recognize these non-standard ports. |

|                             | Interrupt<br>Request<br>Level<br>Select 0<br>(0x70) | The Modem requires one of the following IRQ channels: 3 4, 5, 7, 9, 10, 11, or 12 (see I/O Port Address for address and interrupt combinations).                                                                                                                                                                                                                                                                                                                                                                                       |

### 2.3 AD1812 Non-Plug & Play Device Configuration

Configuring the AD1812 in non-Plug & Play mode is similar to configuring the device when it is in Plug & Play mode. In non-Plug & Play mode, the logical devices (Windows Sound System, Sound Blaster, AdLib, MIDI, & Game Port) on the AD1812 are locked in *Config* mode, ready to be assigned configuration data. Note that in non-Plug & Play mode all configuration decisions are left to your configuration routine rather than the operating system's Plug & Play configuration process.

Use the following procedure configure the AD1812 SoundPort Controller when the controller is in NonPlug & Play mode(PnP pin is deasserted).

- 1. Write the value 0x00 to the ADDRESS egister (PC I/O Address 0x234) (Sets the AD1812 register index to Set RD\_DATA port register)

- Write the value 0x87 to the WRITE\_DATA register (PC I/O Address 0x235) (Sets the address for the READ\_DATA register to PC I/O Address 0x21F (or any valid RD I/O address). See Table 2.4 for a description of how the address value in WRITE\_DATA is calculated and address options.)

- 2. Write the value 0x02 to the ADDRESS register (PC I/O Address 0x234) (Sets the AD1812 register index to Config Control register)

- Write the value 0x01 to the WRITE\_DATA register (PC I/O Address 0x235) (Resets all Plug & Play logical devices to power up values)

- **Note:** Each AD1812 logical device varies slightly in configurable features. The AD1812 Logical Device Number register (AD1812 register index 0x07) lets you select a device to configure. Once you have selected a device, AD1812 register indices 0x30 through 0xFF correspond to the configuration register of that device. The AD1812 register indices below 0x30 are always available because they are not indexed by the logical device register.

The series of steps that follow demonstrate the logical device selection/configuration process for the Windows Sound System. Use the data in Tables 2.4 through 2.10 (at the end of this procedure) to complete configuration steps for the other devices.

- 3. Write the value 0x07 to the ADDRESS egister (PC I/O Address 0x238) (Sets the AD1812 register index to Logical Device Number (LDN) register)

- Write the value 0x00 to the WRITE\_DATA register (PC I/O Address 0x239) (Selects the Windows Sound System Plug & Play device to configure—Logical Device Number 0x00—other valid device numbers are 0x01 (Sound Blaster), 0x02 (AdLib), 0x03 (MIDI), and 0x04 (Game Port))

- Write the value 0x60 to the ADDRESS egister (PC I/O Address 0x238) (Sets the AD1812 register index to IO\_BASE, upper byte register for Windows Sound System)

- Write the value 0x05 to the WRITE\_DATA register (PC I/O Address 0x239) (Sets upper byte of the IO\_BASE register [upper byte of the logical device's PC I/O address] to 0x05)

- Write the value 0x61 to the ADDRESS register (PC I/O Address 0x238) (Sets the AD1812 register index to IO\_BASE, lower byte register for Windows Sound System)

- Write the value 0x30 to the WRITE\_DATA register (PC I/O Address 0x239) (Sets lower byte of the IO\_BASE register [lower byte of the logical device's PC I/O address] to 0x30—Step 4 sets the Windows Sound System address to PC I/O Address 0x530. For other I/O Address range options, see Table 2.5.)

- Write the value 0x70 to the ADDRESS register (PC I/O Address 0x238) (Sets the AD1812 register index to Interrupt level select 0 register for Windows Sound System)

- Write the value 0x0A to the WRITE\_DATA register (PC I/O Address 0x239) (Sets the interrupt level to 10—see Table 2.5 for additional Interrupt request level options)

- Write the value 0x74 to the ADDRESS egister (PC I/O Address 0x238) (Sets the AD1812 register index to DMA channel select *Cupture* register for Windows Sound System)

- Write the value 0x05 to the WRITE\_DATA register (PC I/O Address 0x239) (Sets the DMA channel select 0 to channel 5, 16-bit DMA*apture*—see Table 2.5 for additional DMA options)

- Note: If you do not enable the *capture* DMA channel all DMA (both *capture* & *playback*) occurs on the *playback* DMA channel. Also, note that simultaneous capture and playback is *not* possible using single channel DMA mode.

- Write the value 0x75 to the ADDRESS egister (PC I/O Address 0x238) (Sets the AD1812 register index to DMA channel select *playback* register for Windows Sound System)

- Write the value 0x06 to the WRITE\_DATA register (PC I/O Address 0x239) (Sets the DMA channel select 0 to channel 6, 16-bit DM*playback*—see Table 2.5 for additional DMA options)

At this point, you have configured the Windows Sound System device. The device is ready to be activated or an I/O port conflict check can be performed.

In Tables 2.4 through 2.10 the following acronyms describe register and bit types: (RO) Read Only, (WO) Write Only (WM) Write only Momentaryand (RW) Read/Write.

|            | s a may ion bus Registers                 | (1 III pill de disserted) |

|------------|-------------------------------------------|---------------------------|

| Port Name  | PC I/O Address                            | Туре                      |

| ADDRESS    | 0x234                                     | Write Only (WO)           |

| WRITE_DATA | 0x235                                     | Write Only (WO)           |

| READ_DATA  | Relocatable in the range<br>0x203 - 0x3FF | Read Only (RO)            |

Table 2.4

Non-Plug & Play ISA Bus Registers (PnP pin de-asserted)

|                  | Ŭ       | lay AD1812 ADDRESSRegister Values                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register Name    | ADDRESS | Definition (value)                                                                                                                                                                                                                                                                                                                                                                                                          |

| Set RD_DATA Port | 0x00 WO | Sets the address-value of the READ_DATA port.<br>A write to this register must be performed before<br>any reads. The contents of RD_DATA (bits [7:0])<br>correspond to part of (bits [9:2]) the PC I/O<br>address of the READ_DATA port. The upper bits<br>[15:10] of the PC I/O address contain zeros and the<br>lower bits [1:0] contain ones <i>These bits are not</i><br>user accessible,shown in gray type in example. |

|                  |         | The location of READ_DATA is Relocatable in the range 0x203 to 0x3FF.                                                                                                                                                                                                                                                                                                                                                       |

|                  |         | <b>Example</b> To set the PC I/O address of the READ_DATA port to 0x21F, write 0x87 to the RD_DATA port register. The example below indicates the relationship between the bits in each register. Bit [7] of RD_DATA is set to 1 always.                                                                                                                                                                                    |

|                  |         | READ_DATA<br>Address: 0b0000,0010,0001,1111 = 0x21F                                                                                                                                                                                                                                                                                                                                                                         |

|                  |         | RD_DATA contents: $0b1000,0111 = 0x87$                                                                                                                                                                                                                                                                                                                                                                                      |

| Config Control   | 0x02 WM | Resets all logical devices.                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  |         | Write (1) to bit [0:0] to reset all AD1812 logical devices.                                                                                                                                                                                                                                                                                                                                                                 |

|                  |         | The contents of the configuration registers are set<br>to power up values. Logical devices are inactive<br>and the I/O ranges are disabled (set to zero).                                                                                                                                                                                                                                                                   |

| Logical Device   | 0x07 RW | Selects the current logical device.                                                                                                                                                                                                                                                                                                                                                                                         |

| Number(LDN)      |         | All reads and writes of I/O, DMA, and interrupt configuration registers access the logical devices indexed by this register. AD1812 logical device number indices are:                                                                                                                                                                                                                                                      |

|                  |         | 0x00 (Window Sound System)                                                                                                                                                                                                                                                                                                                                                                                                  |

|                  |         | 0x01 (Sound Blaster)                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  |         | 0x02 (AdLib Music synthesis)                                                                                                                                                                                                                                                                                                                                                                                                |

|                  |         | 0x03 (MIDI port)                                                                                                                                                                                                                                                                                                                                                                                                            |

|                  |         | 0x04 (Game port)                                                                                                                                                                                                                                                                                                                                                                                                            |

|                  |         | 0x05 (Modem)                                                                                                                                                                                                                                                                                                                                                                                                                |

#### Table 2.5 Non-Plug & Play AD1812 ADDRESSRegister Values

| Register Name | ADDRESS | Definition (value)                                                                           |

|---------------|---------|----------------------------------------------------------------------------------------------|

| Powerdown     | 0x20 RW | Controls powerdown operations. (For bit definitions, see Chapter 3 <i>AD1812 Registers</i> ) |

Table 2.5

Non-Plug & Play AD1812 ADDRESSRegister Values (continued)

## Table 2.6 Non-Plug & Play AD1812 ADDRESS Register Values (Windows Sound<br/>System, LDN==0)

| Register Name         | ADDRESS | Definition (value)                                                                                                                                                                                                                                    |

|-----------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Activate              | 0x30 RW | Activates the device on the ISA bus.                                                                                                                                                                                                                  |

|                       |         | Write (1) to bit [0] to activate the device.                                                                                                                                                                                                          |

|                       |         | Note: Do <i>not</i> enable Activate and I/O Range<br>Check at the same time. Bits [7:1] of this register<br>return (0) on reads. An inactive device doe <i>sot</i><br>respond to writes to its I/O address, interrupt<br>(IRQ), or DMA request (DRQ). |

| I/O Range Check       | 0x31 RW | Checks for I/O port conflicts with other devices on ISA bus.                                                                                                                                                                                          |

|                       |         | Write (1) to bit [0] to select 0x55 return on device reads in the programmed range.                                                                                                                                                                   |

|                       |         | Write (0) to bit [0] to select 0xAA return on device reads in the programmed range.                                                                                                                                                                   |

|                       |         | Write (1) to bit [1] to enable I/O check.                                                                                                                                                                                                             |

|                       |         | Note: Do <i>not</i> enable I/O Range Check and Activate at the same time. Bits [7:2] of this register return (0) on reads.                                                                                                                            |

| I/O port base address | 0x60 RW | Holds PC I/O base address.                                                                                                                                                                                                                            |

|                       | 0x61 RW | Write upper byte to 0x60—IO_BASE, bits [15:8]                                                                                                                                                                                                         |

|                       |         | Write lower byte to 0x61—IO_BASE, bits [7:0]                                                                                                                                                                                                          |

|                       |         | Note: The Windows Sound System address range<br>is from 0x0008 to 0xFFF8. The most commonly<br>used address is 0x530. The range is 8 bytes long<br>and must be aligned to an 8 byte memory<br>boundary.                                               |

| Interrupt request     | 0x70 RW | Holds the PC interrupt level selection.                                                                                                                                                                                                               |

| level select 0        |         | Write IRQ value to bits [3:0] to set the PC interrupt level, where valid IRQ values are: 3, 4, 5, 7, 9, 10, 11, & 12                                                                                                                                  |

|                       |         | Note: An IRQ value of 0 represents no interrupt selection. The most commonly used IRQs are 10 & 11.                                                                                                                                                   |

| Register Name     | ADDRESS | Definition (value)                                                                                                                                                                                                                                                                                      |

|-------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt request | 0x71 RO | Holds the PC interrupt sensitivity selection.                                                                                                                                                                                                                                                           |

| type select 0     |         | This Read Only (RO) register contains the value 0x02, indicating that the interrupt sensitivity is set to active-high & edge-sensitive. The contents of this register cannot be changed and it is included only for Plug & Play compatibility.                                                          |

| DMA channel       | 0x74 RW | Holds the <i>capture</i> DMA channel selection.                                                                                                                                                                                                                                                         |

| select 0          |         | Write channel value to bits [2:0], where valid channel values are:                                                                                                                                                                                                                                      |

|                   |         | 0, 1, or 3 (for 8-bit DMA)                                                                                                                                                                                                                                                                              |

|                   |         | 4 (for no DMA)                                                                                                                                                                                                                                                                                          |

|                   |         | 5, 6, or 7 (for 16-bit DMA)                                                                                                                                                                                                                                                                             |

|                   |         | Note: In Plug & Play terms, a Windows Sound<br>System Configuration that includes two 16-bit<br>DMA channels is <i>Good</i> , one 16-bit & one 8-bit<br>DMA channel or two 8-bit DMA channels is<br><i>Acceptable</i> , and one 16-bit DMA channel or one 8-<br>bit DMA channel is <i>Sub-optimal</i> . |

|                   |         | If you do not enable the <i>capture</i> DMA channel all<br>DMA (both <i>capture</i> & <i>playback</i> ) occurs on the<br><i>playback</i> DMA channel. Also, note that<br>simultaneous capture and playback is <i>ot</i> possible<br>using single channel DMA mode                                       |

| DMA channel       | 0x75 RW | Holds the <i>playback</i> DMA channel selection.                                                                                                                                                                                                                                                        |

| select 1          |         | Write channel value to bits [2:0], where valid channel values are:                                                                                                                                                                                                                                      |

|                   |         | 0, 1, or 3 (for 8-bit DMA)                                                                                                                                                                                                                                                                              |

|                   |         | 4 (for no DMA)                                                                                                                                                                                                                                                                                          |

|                   |         | 5, 6, or 7 (for 16-bit DMA)                                                                                                                                                                                                                                                                             |

#### Table 2.6 Non-Plug & Play AD1812ADDRESS Register Values (Window Sound System, LDN==0) (continued)

| <b>D</b> 1 1-         |                    | LDN == 1)                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register Name         | ADDRESS            | Definition (value)                                                                                                                                                                                                                                                                                                                                                                                                                    |