# ADSP-21065L EZ-LAB EVALUATION & DEVELOPMENT BOARD

### **KEY FEATURES:**

### **Evaluation Board**

- **(** € Certified

- ADSP-21065L SHARC DSP running at 60 MHz

- Memory

- 544 Kbits On-Chip SRAM

- 1M x 32-bit External SDRAM

- Socketed 256K x 8-bit ROM (configurable to 1M x 8-bit)

- Full Duplex, 16-bit stereo audio codec

- RS-232 interface with UART

- Expansion through EMAFE connector and external port interface

- EZ-ICE JTAG header connection

#### **Accessories**

- RS-232 cable

- Power supply (Power connector supplied with European version; see table for specifications)

### Software Development Tools

- Debug Target/Monitor with single step and breakpoint features

- VisualDSP Test Drive 45-day trial of IDE, C Compiler, Assembler, Linker, & Loader

- VisualDSP Debugger & SHARC simulator

- Interactive tutorials & ADSP-21065L examples

#### **Demonstrations**

- Fast Fourier Transform (FFT)

- Discrete Fourier Transform (DFT)

- Band Pass Filter

- Pluck String Themes

- Talk Through

- Primes

### **OVERVIEW**

The ADSP-21065L EZ-LAB® is a complete evaluation and development board for the ADSP-21065L SHARC® DSP. The hardware evaluation board is specifically tuned to the features of the ADSP-21065L. For example, the on-board SDRAM allows you to benchmark code that uses the ADSP-21065L's SDRAM controller. In addition, the ADSP-21065L EZ-LAB includes a VisualDSP® Test Drive, a trial license that allows you to evaluate the full development tools suite for the

Analog Devices' SHARC DSP. You can use these tools to create projects for evaluating the features of the ADSP-21065L. You can use the demonstration programs and tutorial included in the Test Drive to become proficient with the development tools and familiar with the features of the ADSP-21065L. Features such as a socketed EPROM, SDRAM memory, EMAFE external port connectors, JTAG connectors, and extensive debug support, allow you to use the EZ-LAB to fully prototype your ADSP-21065L design.

### **ADSP-21065L**

The ADSP-21065L is a generalpurpose, programmable 32-bit DSP that allows users to program with equal efficiency in both fixed-point or floating-point arithmetic. Running at 60 MHz, the ADSP-21065L offers 180 MFLOPs or 180 MOPs of fixed-point performance. This DSP integrates 544 Kbits of configurable, on-chip memory, a glueless SDRAM interface, and two serial transmit/receive ports. The serial ports support 32 channels of TDM and up to 8 channels of audio I/O in I2S mode. There are a total of 10 DMA channels dedicated to the serial ports and the external port. The rich feature set combined with the high performance core makes the ADSP-21065L an outstanding price/performance value for a broad

base of consumer, communications, automotive, industrial and computer applications.

### 16-BIT STEREO AUDIO I/O

The ADSP-21065L EZ-LAB provides full-duplex, 16-bit stereo audio capability for evaluating a range of audio algorithms. The on-board AD1819 CODEC offers professional-quality 3-D audio with 92dB+ fidelity. It supports sampling frequencies from 5.5 to 48 KHz and offers hardware volume control.

### CODE DEVELOPMENT AND DEBUG TOOLS

The SHARC DSPs are supported by the VisualDSP development tools suite. VisualDSP introduces an easyto-use project management environment, comprised of an Integrated Development Environment and Debugger. Because the project development and debug environments are integrated, you can move easily between editing, building, and debugging activities.

### **Software Development Tools Features:**

- Cycle accurate, instructionlevel simulator and debugger that allows debug of assembly,

C, or mixed C/assembly code

- Algebraic syntax assembler

- Optimizing C compiler

- Linker that supports multi processing, shared memory, and code overlays

- Over 100 math, DSP and C

Runtime libraries

- Support for creating host and EPROM boot images

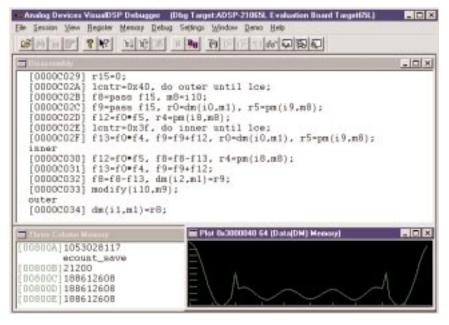

The VisualDSP Test Drive included with the ADSP-21065L EZ-LAB allows designers to evaluate code on

DFT example on the ADSP-21065L EZ-LAB board highlighting memory views and plotting capabilities.

the ADSP-21065L or simulate your application on the ADSP-21060, ADSP-21062, ADSP-21061, or ADSP-21065L using the complete software development tools for these DSPs. The Test Drive includes a 45day trial of the VisualDSP Environment, C compiler, assembler, linker and loader for SHARC DSPs. It also includes the VisualDSP debugger and simulator, which remain accessible beyond the 45-day trial period. As the designer transitions from evaluation to development, there is no additional learning curve because the environment and code development tools remain the same. Detailed, interactive tutorials and extensive example programs are included to ensure that designers make optimum use of the 45-day trial. Additionally, free on-line training for the SHARC architecture and VisualDSP tools is available at www.tolu.com.

## EXTENSIVE DEBUG SUPPORT

The ADSP-21065L EZ-LAB provides extensive debug capabilities via a monitor program running on the DSP in conjunction with a host program running on the PC. Along with basic functions such as uploading and downloading code and data, and running and halting programs, the debug monitor supports breakpoints, single step debug mode, and the ability to view and modify both memory and registers.

If you require non-intrusive in-circuit emulation support, you can purchase the SHARC in-circuit emulator, Mountain-ICE, or Summit-ICE

emulators. These emulators support all the ADSP-2106x processors. A direct connection for the emulator is provided on the EZ-LAB board via the JTAG header.

### **Development Partners**

Hundreds of products are available from independent developers.

Libraries, RTOS, debuggers, COTS DSP boards, and emulators are detailed on the ADI website at www.analog.com/dsp.

You can order the ADSP-21065L EZ-LAB evaluation board, SHARC incircuit emulator, and VisualDSP from your local ADI-authorized distributor. For the office nearest you, see our website at www.analog.com.

For more information about the Mountain-ICE, or Summit-ICE products, see www.wmdsp.com or send E-mail to info@wmdsp.com.

### **European Power Supply Specifications**

| DC Voltage   | 7.5V +/- 5% (Full Load)                        |

|--------------|------------------------------------------------|

|              |                                                |

| Current      | 1.2 Amps (Minimum Rating)                      |

|              |                                                |

| Ripple       | 500 mV rms (Max @ Full Load)                   |

|              |                                                |

| DC Connector |                                                |

| Туре         | Switchcraft 760 style, FEMALE                  |

| Plug Size    | 5.5 (OD) X 2.5 (ID) X 9.5 (length) millimeters |

| Polarity     | Center is Positive (inside terminal)           |

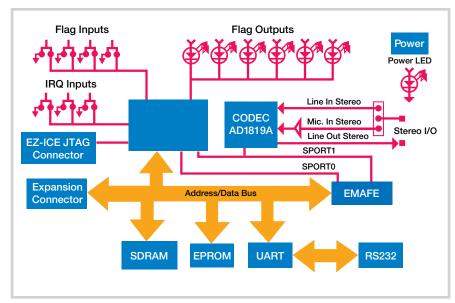

### ADSP-21065L EZ-LAB System Block Diagram

### **DSP SUPPORT:**

Email:

In the U.S.A.: dsp.support@analog.com In Europe: dsp.europe@analog.com

Fax: In the U.S.A.: 1 781 461-3010 In Europe: +49-89-76903-307

Web Address: http://www.analog.com/dsp

### **WORLDWIDE HEADQUARTERS**

One Technology Way P.O. Box 9106 Norwood, MA 02062-9106, U.S.A. Tel: 1 781 329 4700

(1 800 262 5643 U.S.A. only)

Fax: 1 781 326 8703

World Wide Web Site: http://www.analog.com

### **EUROPE HEADQUARTERS**

Am Westpark 1-3 81373 München, Germany Tel: +89 76903-0; Fax +89 76903-157

#### JAPAN HEADQUARTERS

New Pier Takeshiba, South Tower Building 1-16-1 Kaigan, Minato-ku, Tokyo 105, Japan Tel: +3 5402 8210; Fax: +3 5402 1063

#### **SOUTHEAST ASIA HEADQUARTERS**

2102 Nat West Tower, Times Square One Matheson Street Causeway Bay, Hong Kong Tel: +2 506 9336; Fax: +2 506 4755

Printed in the U.S.A H3595-15-4/99