# Programmable Digital QPSK/16-QAM Modulator

AD9853

#### **FEATURES**

Universal Low Cost Solution for HFC Network Return-Channel T<sub>X</sub> Function: 5 MHz-42 MHz/ 5 MHz-65 MHz

165 MHz Internal Reference Clock Capability Includes Programmable Pulse-Shaping FIR Filters and Programmable Interpolating Filters

FSK/QPSK/DQPSK/16-QAM/D16-QAM Modulation Formats

6× Internal Reference Clock Multiplier

Integrated Reed-Solomon FEC Function

Programmable Randomizer/Preamble Function

Supports Interoperable Cable Modem Standards

Internal SINx/x Compensation

>50 dB SFDR @ 42 MHz Output Frequency (Single Tone)

Controlled Burst Mode Operation

+3.3 V to +5 V Single Supply Operation

Low Power: 750 mW @ Full Clock Speed (3.3 V Supply)

Space Saving Surface Mount Packaging

APPLICATIONS

HFC Data, Telephony and Video Modems

Wireless LAN

#### **GENERAL DESCRIPTION**

The AD9853 integrates a high speed direct-digital synthesizer (DDS), a high performance, high speed digital-to-analog converter (DAC), digital filters and other DSP functions onto a single chip, to form a complete and flexible digital modulator device. The AD9853 is intended to function as a modulator in network applications such as interactive HFC, WLAN and MMDS, where cost, size, power dissipation, functional integration and dynamic performance are critical attributes.

The AD9853 is fabricated on an advanced CMOS process and it sets a new standard for CMOS digital modulator performance. The device is loaded with programmable functionality and provides a direct interface port to the AD8320, digitally-programmable cable driver amplifier. The AD9853/AD8320 chipset forms a highly integrated, low power, small footprint and cost-effective solution for the HFC return-path requirement and other more general purpose modulator applications.

The AD9853 is available in a space saving surface mount package and is specified to operate over the extended industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

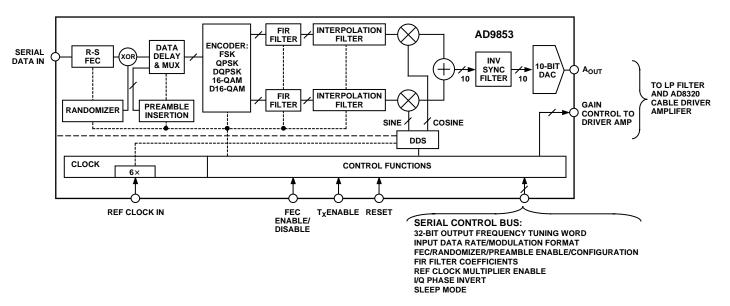

#### FUNCTIONAL BLOCK DIAGRAM

# $\textbf{AD9853-SPECIFICATIONS} \ \, (\textbf{V}_{\text{S}} = +3.3 \, \text{V} \pm 5\%, \, \textbf{R}_{\text{SET}} = 3.9 \, \text{k}\Omega, \, \text{Reference Clock Frequency} = 20.48 \, \text{MHz with } \\ \textbf{6} \times \text{ REFCLK Enabled, Symbol Rate} = 2.56 \, \text{MS/s}, \, \alpha = 0.25, \, \text{unless otherwise noted})$

| Parameter                                                                   | Temp  | Test Level | Min  | Typ  | Max  | Units |

|-----------------------------------------------------------------------------|-------|------------|------|------|------|-------|

| REF CLOCK INPUT CHARACTERISTICS                                             |       |            |      |      |      |       |

| Frequency Range                                                             |       |            |      |      |      |       |

| 6× REFCLK Disabled (+3.3 V Supply)                                          | Full  | IV         | 42   |      | 126  | MHz   |

| 6× REFCLK Enabled (+3.3 V Supply)                                           | Full  | IV         | 7    |      | 21   | MHz   |

| 6× REFCLK Disabled (+5 V Supply)                                            | Full  | IV         | 108  |      | 168  | MHz   |

| 6× REFCLK Enabled (+5 V Supply)                                             | Full  | IV         | 18   |      | 28   | MHz   |

| Duty Cycle                                                                  | +25°C | IV         | 40   |      | 60   | %     |

| Input Capacitance                                                           | +25°C | V          |      | 3    |      | pF    |

| Input Impedance                                                             | +25°C | V          |      | 100  |      | ΜΩ    |

| DAC OUTPUT CHARACTERISTICS                                                  |       |            |      |      |      |       |

| Resolution                                                                  |       |            |      | 10   |      | Bits  |

| Full-Scale Output Current                                                   | +25°C | IV         | 5    | 10   | 20   | mA    |

| Gain Error                                                                  | +25°C | I          | -10  |      | +10  | % FS  |

| Output Offset                                                               | +25°C | I          |      |      | 10   | μA    |

| Output Offset Temperature Coefficient                                       | Full  | V          |      | 50   |      | nA/°C |

| Differential Nonlinearity                                                   | +25°C | I          |      | 0.5  | 0.75 | LSB   |

| Integral Nonlinearity                                                       | +25°C | I          |      | 0.5  | 1.5  | LSB   |

| Output Capacitance                                                          | +25°C | V          |      | 5    |      | pF    |

| Phase Noise @ 1 kHz Offset, 40 MHz A <sub>OUT</sub>                         |       |            |      |      |      |       |

| 6× REFCLK Enabled                                                           | +25°C | V          |      | -100 |      | dBc   |

| 6× REFCLK Disabled                                                          | +25°C | V          |      | -110 |      | dBc   |

| Voltage Compliance Range                                                    | +25°C | I          | -0.5 |      | +1.5 | V     |

| Wideband SFDR (Single Tone):                                                |       |            |      |      |      |       |

| 1 MHz A <sub>OUT</sub>                                                      | +25°C | IV         | 62   | 68   |      | dBc   |

| $20~\mathrm{MHz}~\mathrm{A}_{\mathrm{OUT}}$                                 | +25°C | IV         | 52   | 54   |      | dBc   |

| 42 MHz A <sub>OUT</sub>                                                     | +25°C | IV         | 48   | 50   |      | dBc   |

| 65 MHz A <sub>OUT</sub> <sup>1</sup>                                        | +25°C | IV         | 42   | 44   |      | dBc   |

| MODULATOR CHARACTERISTICS                                                   |       |            |      |      |      |       |

| I/Q Offset                                                                  | +25°C | IV         | 48   |      |      | dB    |

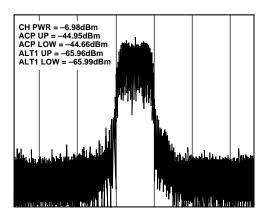

| Adjacent Channel Power                                                      | +25°C | IV         | 44   |      |      | dBm   |

| Error Vector Magnitude                                                      | +25°C | IV         |      | 1    | 2    | %     |

| In-Band Spurious Emission                                                   |       |            |      |      |      |       |

| 5 MHz–42 MHz A <sub>OUT</sub>                                               | +25°C | IV         |      | 42   |      | dBc   |

| 5 MHz–65 MHz A <sub>OUT</sub> <sup>1</sup>                                  | +25°C | IV         |      | 40   |      | dBc   |

| Passband Amplitude Ripple                                                   | +25°C | V          |      | ±0.3 |      | dB    |

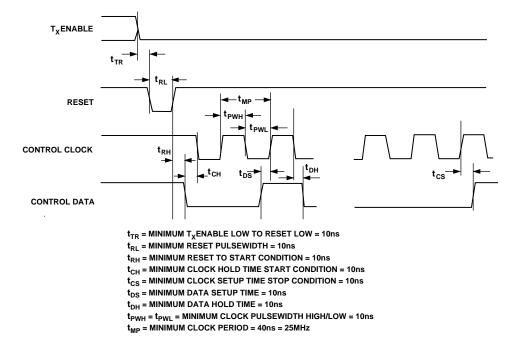

| TIMING CHARACTERISTICS                                                      |       |            |      |      |      |       |

| Serial Control Bus                                                          |       |            |      |      |      |       |

| Maximum Frequency                                                           | Full  | IV         |      |      | 25   | MHz   |

| Minimum Clock Pulsewidth Low (t <sub>PWL</sub> )                            | Full  | IV         | 10   |      |      | ns    |

| Minimum Clock Pulsewidth High (t <sub>PWH</sub> )                           | Full  | IV         | 10   |      |      | ns    |

| Maximum Clock Rise/Fall Time                                                | Full  | IV         | 100  |      |      | ns    |

| Minimum Data Setup Time (t <sub>DS</sub> )                                  | Full  | IV         | 10   |      |      | ns    |

| Minimum Data Hold Time (t <sub>DH</sub> )                                   | Full  | IV         | 10   |      |      | ns    |

| Minimum Clock Setup—Stop Condition (t <sub>CS</sub> )                       | Full  | IV         | 10   |      |      | ns    |

| Minimum Clock Hold—Start Condition (t <sub>CH</sub> )                       | Full  | IV         | 10   |      |      | ns    |

| RESET                                                                       | L     |            |      |      |      |       |

| Minimum T <sub>X</sub> ENABLE Low to RESET Low (t <sub>TR</sub> )           | Full  | IV         | 10   |      |      | ns    |

| Minimum RESET High to Start Condition (t <sub>RH</sub> )                    | Full  | IV         | 10   |      |      | ns    |

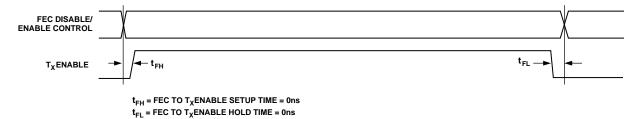

| FEC ENABLE                                                                  | F "   | 177        |      |      |      |       |

| Minimum FEC ENABLE/DISABLE to T <sub>X</sub> ENABLE High (t <sub>FH</sub> ) | Full  | IV         | 0    |      |      | ns    |

| Minimum FEC ENABLE/DISABLE to T <sub>X</sub> ENABLE Low (t <sub>FL</sub> )  | Full  | IV         | 0    |      |      | ns    |

-2- REV. A

| Parameter                                       | Temp  | Test Level | Min  | Тур | Max  | Units   |

|-------------------------------------------------|-------|------------|------|-----|------|---------|

| TIMING CHARACTERISTICS (Continued)              |       |            |      |     |      |         |

| Wake-Up Time-PLL Power-Down                     | +25°C | IV         |      | 1   |      | ms      |

| Wake-Up Time-DAC Power-Down                     | +25°C | IV         |      | 200 |      | μs      |

| Wake-Up Time-Digital Power-Down                 | +25°C | IV         |      | 5   |      | μs      |

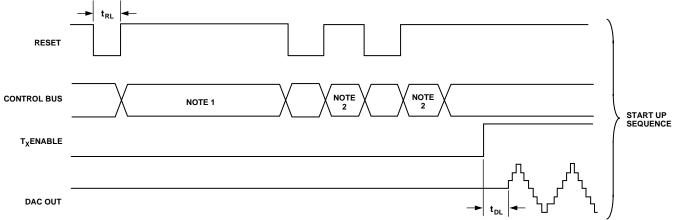

| Data Latency (t <sub>DL</sub> )                 | +25°C | IV         |      | 6   |      | Symbols |

| Minimum RESET Pulsewidth Low (t <sub>RL</sub> ) | +25°C | IV         |      | 10  |      | ns      |

| CMOS LOGIC INPUTS                               |       |            |      |     |      |         |

| Logic "1" Voltage, +5 V Supply                  | +25°C | I          | +3.5 |     |      | V       |

| Logic "1" Voltage, +3.3 V Supply                | +25°C | I          | +3.0 |     |      | V       |

| Logic "0" Voltage                               | +25°C | I          |      |     | +0.4 | V       |

| Logic "1" Current                               | +25°C | I          |      |     | 12   | μA      |

| Logic "0" Current                               | +25°C | I          |      |     | 12   | μA      |

| Input Capacitance                               | +25°C | V          |      | 3   |      | pF      |

| POWER SUPPLY <sup>2</sup>                       |       |            |      |     |      |         |

| $+V_S$ Current (+3.3 V + 5%)                    |       |            |      |     |      |         |

| Full Operating Conditions                       | +25°C | I          |      | 184 | 230  | mA      |

| With PLL Power-Down Enabled                     | +25°C | I          |      | 178 | 224  | mA      |

| With DAC Power-Down Enabled                     | +25°C | I          |      | 170 | 216  | mA      |

| With Digital Power-Down Enabled                 | +25°C | I          |      | 36  | 54   | mA      |

| With All Power-Down Enabled                     | +25°C | I          |      | 16  | 20   | mA      |

| +V <sub>S</sub> Current (+5 V + 5%)             | +25°C | I          |      | 400 | 595  | mA      |

#### NOTES

Specifications subject to change without notice.

#### **EXPLANATION OF TEST LEVELS**

#### **Test Level**

- I 100% Production Tested.

- III Sample Tested Only.

- IV Parameter is guaranteed by design and characterization testing.

- V Parameter is a typical value only.

- VI Devices are 100% production tested at +25°C and guaranteed by design and characterization testing for industrial operating temperature range.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Maximum Junction Temperature +150°C                       |

|-----------------------------------------------------------|

| $V_S$ +6 $V$                                              |

| Digital Inputs $-0.7 \text{ V to } + \text{V}_{\text{S}}$ |

| Digital Output Current 5 mA                               |

| Storage Temperature65°C to +150°C                         |

| Operating Temperature40°C to +85°C                        |

| Lead Temperature (10 sec Soldering) +300°C                |

| MQFP $\theta_{JA}$ Thermal Impedance                      |

|                                                           |

<sup>\*</sup>Absolute maximum ratings are limiting values, to be applied individually, and beyond which the serviceability of the circuit may be impaired. Functional operability under any of these conditions is not necessarily implied. Exposure of absolute maximum rating conditions for extended periods of time may affect device reliability.

#### **ORDERING GUIDE**

| Model    |                | Package<br>Description      | Package<br>Option |

|----------|----------------|-----------------------------|-------------------|

| AD9853AS | -40°C to +85°C | Metric Quad Flatpack (MQFP) | S-44A             |

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9853 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. A -3-

<sup>&</sup>lt;sup>1</sup>Reference clock = 28 MHz with clock multiplier enabled; supply voltage = +5 V.

<sup>&</sup>lt;sup>2</sup>Maximum values are obtained under worst case operating modes. Typical values are valid for most applications.

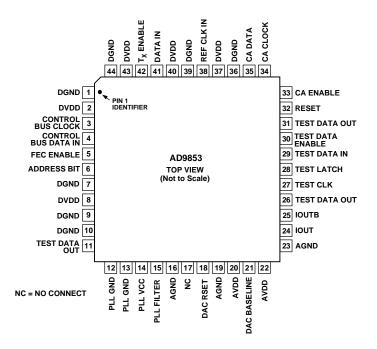

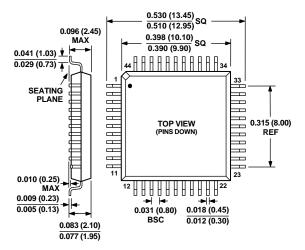

#### PIN FUNCTION DESCRIPTIONS

| Pin #        | Pin Name              | Pin Function                                     |

|--------------|-----------------------|--------------------------------------------------|

| 1, 7, 9, 10, |                       |                                                  |

| 36, 39, 44   | DGND                  | Digital Ground                                   |

| 2, 8, 37,    |                       |                                                  |

| 40, 43       | DVDD                  | Digital Supply Voltage                           |

| 3            | Control Bus Clock     | Bit Clock for Control Bus<br>Data                |

| 4            | Control Bus Data In   | Control Bus Data In                              |

| 5            | FEC Enable            | Enables/Disables FEC                             |

| 6            | Address Bit           | Address Bit for Control Bus                      |

| 11, 26, 31   | Test Data Out         | Factory Use—Serial Test Data Out                 |

| 12, 13       | PLL GND               | PLL Ground                                       |

| 14           | PLL VCC               | Supply Voltage for PLL                           |

| 15           | PLL Filter            | PLL Loop Filter Connection                       |

| 16, 19, 23   | AGND                  | Analog Ground                                    |

| 17           | NC                    | No Connect                                       |

| 18           | DAC Rset              | Rset Resistor Connection                         |

| 20, 22       | AVDD                  | Analog Supply Voltage                            |

| 21           | DAC Baseline          | DAC Baseline Voltage                             |

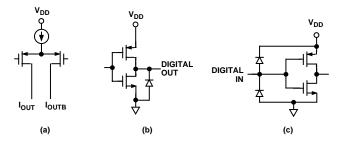

| 24           | IOUT                  | Analog Current Output of the DAC                 |

| 25           | IOUTB                 | Complementary Analog Current Output of the DAC   |

| 27           | Test CLK              | Factory Use—Scan Clock                           |

| 28           | Test Latch            | Factory Use—Scan Latch                           |

| 29           | Test Data In          | Factory Use—Serial Test Data<br>In               |

| 30           | Test Data Enable      | Factory Use—Serial Test Data<br>Enable           |

| 32           | RESET                 | Master Device Reset Function                     |

| 33           | CA Enable             | Cable Amplifier Enable                           |

| 34           | CA Clock              | Cable Amplifier Serial Control<br>Clock          |

| 35           | CA Data               | Cable Amplifier Serial Control<br>Data           |

| 38           | REF CLK IN            | Reference Clock Input                            |

| 41           | Data In               | Input Serial Data Stream                         |

| 42           | T <sub>x</sub> ENABLE | Pulse that Frames the Valid<br>Input Data Stream |

#### PIN CONFIGURATION

44-Lead Metric Quad Flatpack (S-44A)

-4- REV. A

| Table I   | Modulator | Function | Description |

|-----------|-----------|----------|-------------|

| i abie i. | MOGUIAIOF | runchon  | Describtion |

| Modulation Encoding Format        | FSK*, QPSK, DQPSK, 16-QAM, D16-QAM, Selectable via Control Bus                                                                                                                                                                                                                                               |  |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Output Carrier Frequency Range    | DC – 63 MHz with +3.3 V Supply Voltage<br>DC – 84 MHz with +5 V Supply Voltage                                                                                                                                                                                                                               |  |  |  |  |  |

| Serial Input Data Rate            | Evenly Divisible Fraction of Reference Clock                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Pulse-Shaping FIR Filter          | 41 Tap, Linear Phase, 10-Bit Coefficients Fully Programmable via Control Bus                                                                                                                                                                                                                                 |  |  |  |  |  |

| Interpolation Range               | Interpolation Rate = $(4/M) \times (ICIC1) \times (ICIC2)$ where: $M = 2$ for QPSK, $M = 4$ for 16-QAM                                                                                                                                                                                                       |  |  |  |  |  |

|                                   | Minimum and Maximum Rates Minimum Interpolation Rate—QPSK = $2 \times 3 \times 2 = 12$ $16\text{-QAM} = 1 \times 4 \times 3 = 12$ Maximum Interpolation Rate—QPSK = $2 \times 31 \times 63 = 3906$ $16\text{-QAM} = 1 \times 31 \times 63 = 1953$                                                            |  |  |  |  |  |

|                                   | These are the minimum and maximum interpolation ratios from the input data rate to the system clock. The interpolation range is a function of the fixed interpolation factor of four in the FIR filters, the programmed CIC filter interpolation rates (ICIC1, ICIC2), as well as system timing constraints. |  |  |  |  |  |

| Maximum Reference Clock Frequency | +3.3 V Supply: 21 MHz with 6× REFCLK enabled, 126 MHz with 6× REFCLK disabled<br>+5 V Supply: 28 MHz with 6× REFCLK enabled, 168 MHz with 6× REFCLK disabled                                                                                                                                                 |  |  |  |  |  |

| 6× REFCLK                         | Fixed 6× reference clock multiplier, enable/disable control via control bus                                                                                                                                                                                                                                  |  |  |  |  |  |

| R-S FEC                           | Enable/disable via control bus and dedicated control pin. Control pin enable/disable function:  Logic "1" = Enable  Logic "0" = Disable                                                                                                                                                                      |  |  |  |  |  |

|                                   | Primitive Polynomial: $p(x) = x^8 + x^4 + x^3 + x^2 + 1$<br>Code Generator Polynomial: $g(x) = (x + \alpha^0)(x + \alpha^1)(x + \alpha^2) \dots (x + \alpha^{2t-1})$                                                                                                                                         |  |  |  |  |  |

|                                   | Selectable via Control Bus $t = 0-10 \text{ (Programmable)}$ Codeword Length (N) = 255 max (Programmable) $N = K + 2 t \text{ (K Range} = 16 \le K \le 255 - 2 t)$                                                                                                                                           |  |  |  |  |  |

|                                   | FEC/Randomizer can be transposed in signal chain via control bus.                                                                                                                                                                                                                                            |  |  |  |  |  |

| I/Q Channel Spectrum              | $I \times COS + Q \times SIN$ (default) or $I \times COS - Q \times SIN$ , selectable via control bus.                                                                                                                                                                                                       |  |  |  |  |  |

| Preamble Insertion                | 0-96 Bits, Programmable Length and Content                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Randomizer                        | Enable/Disable Control via Control Bus Generating Polynomial: $x^{6} + x^{5} + 1, \text{Programmable Seed (Davic/DVB-Compliant)}$ or $x^{15} + x^{14} + 1, \text{Programmable Seed (DOCSIS-Compliant)}$ Randomizer and FEC blocks can be transposed in signal chain, via control bus.                        |  |  |  |  |  |

<sup>\*</sup>In FSK mode, F0:F1 are direct DDS Cosine output.

REV. A -5-

Table II. Control Register Functional Assignment

| Register<br>Address |                                                                                                   |                                                                                            |                                                        | DATA                                                    |                                                  |                                                                                           |                           |                   |

|---------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------|-------------------|

| (Note 1)            | <b>D</b> 7                                                                                        | D6                                                                                         | D5                                                     | D4                                                      | D3                                               | D2                                                                                        | D1                        | D0                |

| 00h                 | MSB                                                                                               | Value of K (Mess                                                                           | age Length in Bytes                                    | ) for Reed-Solomon                                      | Encoder, where 16 <sub>1</sub>                   | $0 \le K \le 255_{10}$ (No                                                                | te 2)                     | LSB               |

| 01h                 | MSB                                                                                               | The Number of Errors (t) for the Encoder, where 0 For $t = 0$ , the RS effectively disable | Reed-Solomon<br>$\leq t \leq 10_{10}$ .<br>Sencoder is | LSB                                                     | Randomizer Insertion  0 = After RS 1 = Before RS | Randomizer I<br>$00_2 = 6$ Bit<br>$01_2 = 15$ Bit<br>$10_2 = $ Random<br>$11_2 = $ Random | nizer OFF                 | (Note 3)          |

| 02h                 | MSB                                                                                               | Lower Eight Bits                                                                           | of Seed Value for 15                                   | 5-Bit Randomizer (                                      | Not Used for 6-Bit                               |                                                                                           |                           | LSB               |

| 03h                 | MSB                                                                                               | – OR –                                                                                     | of Seed Value for 1 Bit Randomizer (D                  |                                                         | ase).                                            |                                                                                           | LSB                       |                   |

| 04h                 | MSB                                                                                               | Preamble Length                                                                            | (L) where $0 \le L \le 9$                              | 6 Bits (Note 4)                                         |                                                  |                                                                                           | LSB                       |                   |

| 05h                 | Modulation Mode<br>000 <sub>2</sub> = QPSK, 001 <sub>2</sub> =<br>011 <sub>2</sub> = D16-QAM, 100 |                                                                                            | -QAM                                                   |                                                         |                                                  |                                                                                           |                           |                   |

| 06h                 | The MSB of the pream a packet. Up to 96 bits                                                      |                                                                                            |                                                        |                                                         |                                                  |                                                                                           | ce during tran            | smission of       |

| 11h                 | MSB                                                                                               |                                                                                            | Preamble Data                                          | a. (Note 5)                                             |                                                  |                                                                                           |                           |                   |

| 12h                 |                                                                                                   | MSB                                                                                        | Interpolator #<br>Rate Change F                        | 1: RATE<br>Factor (R) where 3 <sub>10</sub>             | $_{0} \leq R \leq 31_{10}$                       | LSB                                                                                       |                           |                   |

| 13h                 |                                                                                                   | MSB                                                                                        | Interpolator #2<br>Rate Change F                       | 2: RATE<br>Factor (R) where 2 <sub>10</sub>             | $_0 \le R \le 63_{10}$                           |                                                                                           | LSB                       |                   |

| 14h                 | MSB                                                                                               | Interpolator #1:                                                                           | SCALE                                                  |                                                         | LSB                                              | 2× Multiplier<br>0 = OFF<br>1 = ON                                                        |                           |                   |

| 15h                 | MSB                                                                                               | Interpolator #2:                                                                           | SCALE                                                  |                                                         |                                                  | LSB                                                                                       |                           |                   |

| 16h<br>:<br>19h     | MSB                                                                                               |                                                                                            |                                                        | ning Word #1 pecifies the "space" es: Specifies the car |                                                  |                                                                                           |                           | LSB               |

| 1Ah<br>:<br>1Dh     | MSB                                                                                               |                                                                                            | Frequency Tu<br>FSK Mode: Sp                           |                                                         | frequency (F1).                                  |                                                                                           |                           | LSB               |

| 1Eh <sup>5</sup>    | MSB-2                                                                                             | MSB-3                                                                                      | · · · · · · · · · · · · · · · · · · ·                  | d Tap Coefficient,                                      |                                                  |                                                                                           |                           | LSB <sub>0</sub>  |

| 1Fh                 | MSB <sub>0</sub>                                                                                  | MSB-1                                                                                      | <                                                      |                                                         | ———Unused Bi                                     | its — — — —                                                                               |                           | >                 |

| : : :               | 11.020                                                                                            | 1.02 1                                                                                     | FIR Intermedi                                          | ate Tap Coefficient                                     |                                                  |                                                                                           |                           | <u>`</u>          |

| 46h                 | MSB-2                                                                                             | MSB-3                                                                                      | 10-Bit FIR Ce                                          | nter Tap Coefficien                                     | nt, a <sub>20</sub>                              |                                                                                           |                           | LSB <sub>20</sub> |

| 47h                 | MSB <sub>20</sub>                                                                                 | MSB-1                                                                                      | <                                                      |                                                         | ———Unused Bi                                     | its ————                                                                                  |                           | >                 |

| 48h<br>(Note 6)     | $Spectrum \\ 0 = I \times Cos + Q \times Sin \\ 1 = I \times Cos - Q \times Sin$                  | Digital Power<br>0 = Normal<br>1 = Shutdown                                                | 6× RefClk<br>0 = Off<br>1 = On                         | PLL Mode<br>0 = Awake<br>1 = Sleep                      | DAC Mode<br>0 = Awake<br>1 = Sleep               |                                                                                           |                           |                   |

| 49h<br>(Note 7)     | MSB                                                                                               | The absolute gain                                                                          | AD8320 Cable $A_{V}$ , of the AD832                    | e Driver Gain Con 0 is given by: $A_V =$                |                                                  | $GCB$ (where $0 \le G$                                                                    | GCB ≤ 255 <sub>10</sub> ) | LSB               |

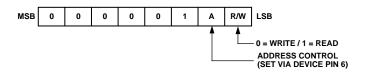

<sup>1</sup>The 8-bit Register Address is preceded by an 8-bit Device Address, which is given by 000001XY, where the value of Bits X and Y are determined as follows:

| X | Voltage Applied to Pin 6 | Y | Desired Register Function |

|---|--------------------------|---|---------------------------|

| 0 | GND                      | 0 | WRITE                     |

| 1 | +V <sub>S</sub>          | 1 | READ                      |

<sup>&</sup>lt;sup>2</sup>This register must be loaded with a nonzero value even if the RS encoder has been disabled by setting T = 0 in register 01h.

REV. A -6-

<sup>&</sup>lt;sup>3</sup>Unused regions are *don't care* bit locations.

<sup>4</sup>If a preamble is not used this register *must* be initialized to a value of 0 by the user.

<sup>&</sup>lt;sup>5</sup>Addresses 06h-011h and 1Eh-47h are write only.

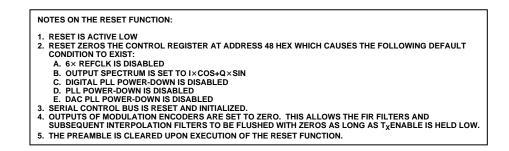

$<sup>^6</sup>$  Assertion of RESET (Pin 32) sets the contents of this register to 0.  $^7$  Registers 0h–48h may be written to using a single register address followed by a contiguous data sequence (see Figure 27). Register 49h, however, must be written to individually; i.e., a separately addressed 8-bit data sequence.

# **Typical Performance Characteristics—AD9853**

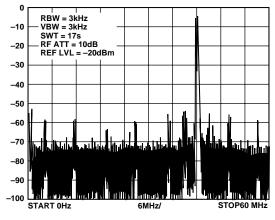

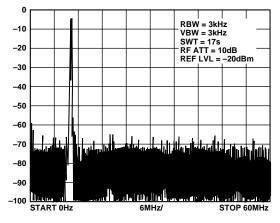

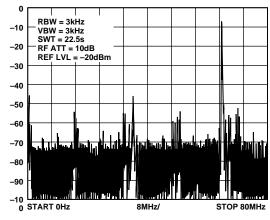

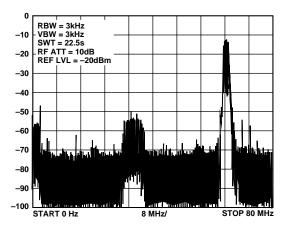

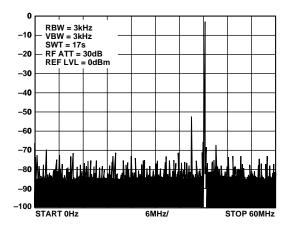

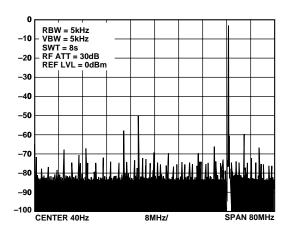

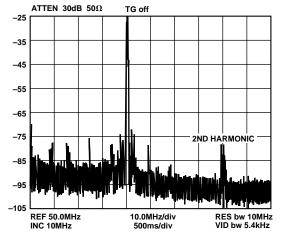

### Modulated Output Spectrum with 3.3 V Supply, $\alpha = 0.25$ , 20.48 MHz REFCLK

Figure 1. QPSK, 320 kb/s,  $A_{OUT} = 10 \text{ MHz}$

Figure 2. QPSK, 640 kb/s,  $A_{OUT} = 20 \text{ MHz}$

Figure 3. QPSK, 1.28 Mb/s,  $A_{OUT} = 42$  MHz

Figure 4. QPSK, 1.28 Mb/s,  $A_{OUT} = 10$  MHz

Figure 5. QPSK, 2.56 Mb/s,  $A_{OUT} = 20$  MHz

Figure 6. QPSK, 5.12 Mb/s,  $A_{OUT} = 42$  MHz

REV. A -7-

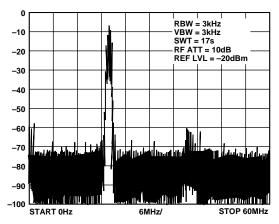

### Modulated Output Spectrum with 5 V Supply, $\alpha = 0.25$ , 27.5 MHz REFCLK

Figure 7. QPSK, 1.375 Mb/s,  $A_{OUT} = 65$  MHz

Figure 10. QPSK, 5.5 Mb/s,  $A_{OUT} = 65$  MHz

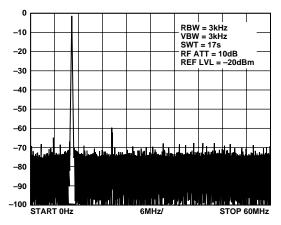

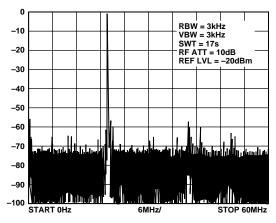

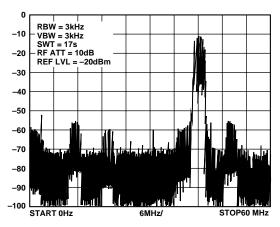

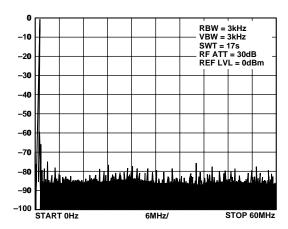

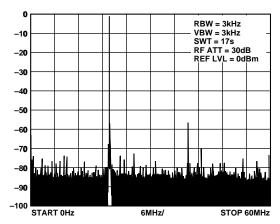

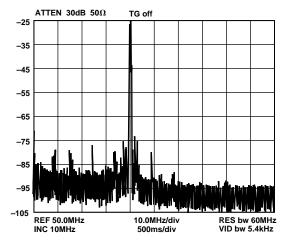

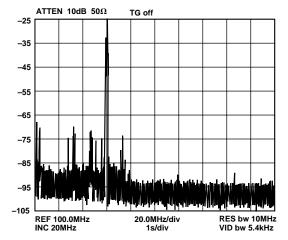

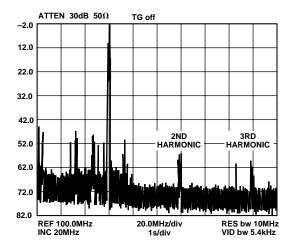

### Single Tone Output Spectrum with +3.3 V Supply, 20.48 MHz REFCLK

Figure 8.  $A_{OUT} = 1 MHz$

Figure 11.  $A_{OUT} = 20 \text{ MHz}$

Figure 9.  $A_{OUT} = 42 \text{ MHz}$

Figure 12.  $A_{OUT} = 65 \text{ MHz}$ (+5 V Supply, 27.5 MHz REFCLK)

-8- REV. A

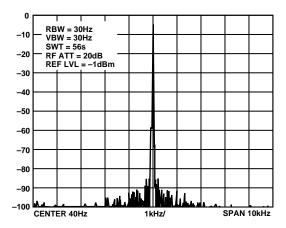

# Output Phase Noise Plots, $A_{\text{OUT}} = 40 \text{ MHz}$

Figure 13. 6× REFCLK Enabled

Figure 14. 6× REFCLK Disabled

Figure 15. Adjacent Channel Power,  $A_{OUT}$  = 30 MHz, 2.56 MS/s, Channel BW = 3.2 MHz ( $\alpha$  = 0.25)

REV. A -9-

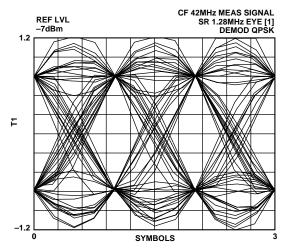

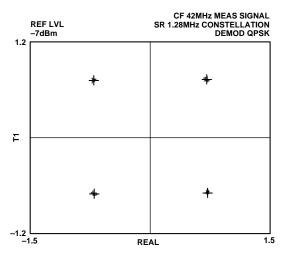

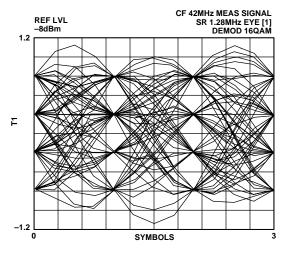

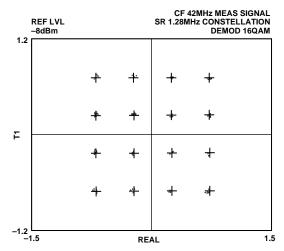

### **Typical Plots of Eye Diagrams and Constellations**

Figure 16. QPSK Modulation

Figure 17. QPSK Modulation

Figure 18. 16-QAM Modulation

Figure 19. 16-QAM Modulation

-10- REV. A

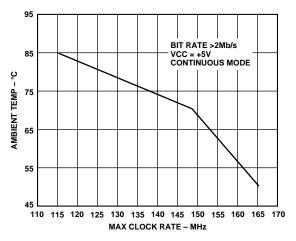

Figure 20. Max CLK Rate vs. Ambient Temperature (To Ensure Max Junction Temp is Not Exceeded)

0.80

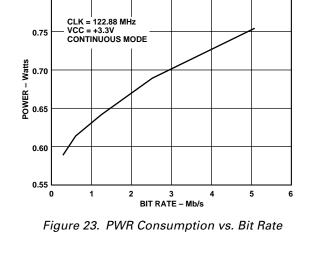

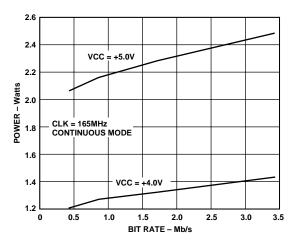

Figure 21. Power Consumption vs. Bit Rate

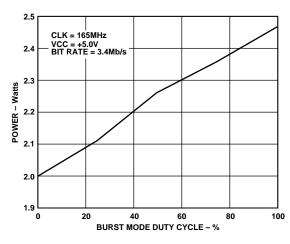

Figure 24. Power Consumption vs. Burst Duty Cycle

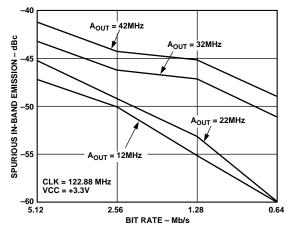

Figure 22. Spurious Emission vs. Bit Rate vs. A<sub>OUT</sub>

Figure 25. Spurious Emission vs. Bit Rate vs. A<sub>OUT</sub>

REV. A -11-

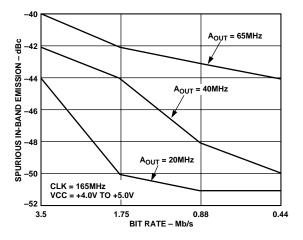

- 3. IF NECESSARY, ZERO FILL THE LAST CODEWORD TO REACH ASSIGNED K DATA BYTES PER CODEWORD

- 4. THE INPUT DATA IS SAMPLED AT THE BIT RATE FREQUENCY ( $f_B$ ) WITH THE FIRST SAMPLE TAKEN AT  $\frac{1}{2 \times (f_B)}$  SECONDS AFTER THE RISING EDGE OF T<sub>Y</sub>ENABLE

- 5. PREAMBLE DELAY =  $\frac{\text{(# OF PREAMBLE BITS)}}{\text{(BIT RATE FREQUENCY)}}$

- 6. DATA RATE MUST BE EXACT SUB-MULTIPLE OF REFERENCE CLOCK.

Figure 26. Data Framing and Processing

-12- REV. A

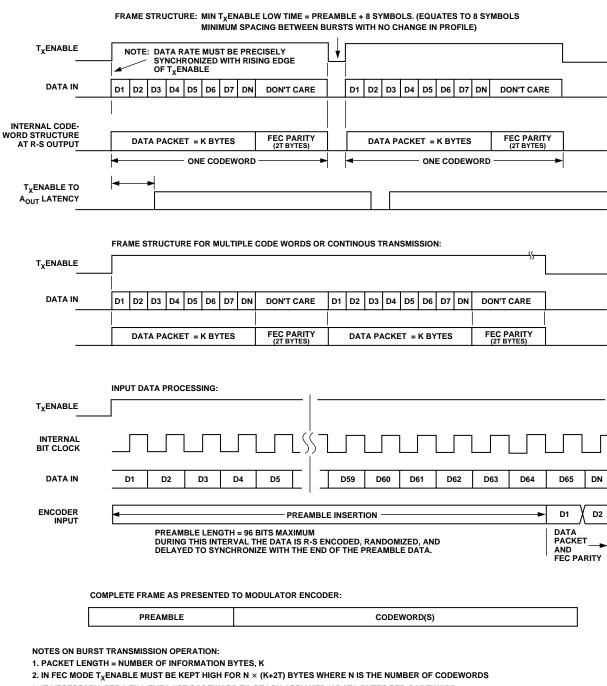

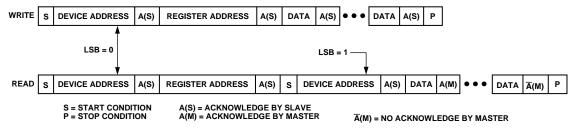

Figure 27. Serial Control Bus—Read and Write Sequences

Figure 28. Serial Control Bus—8-Bit Device Address Detail

Figure 29. FEC Enable/Disable Timing Diagram

Figure 30. Serial Control Interface Timing Diagram

-13-

REV. A

t<sub>RL</sub>: MINIMUM RESET LOW TIME = 10ns t<sub>DL</sub>: DATA LATENCY = 6 SYMBOLS

NOTE 1. DURING THIS INTERVAL ALL CONTROL BUS REGISTERS MUST BE PROGRAMMED.

NOTE 2. DURING THIS INTERVAL THE CONTROL REGISTER (48h) MAY NEED TO BE REPROGRAMMED DUE TO BEING CLEARED BY THE PRECEDING RESET PULSE.

NOTE 3. THREE RESETS ARE REQUIRED TO ENSURE THAT THE DATA PATH IS ZERO'D.

Figure 31. Recommended Start-Up Sequence

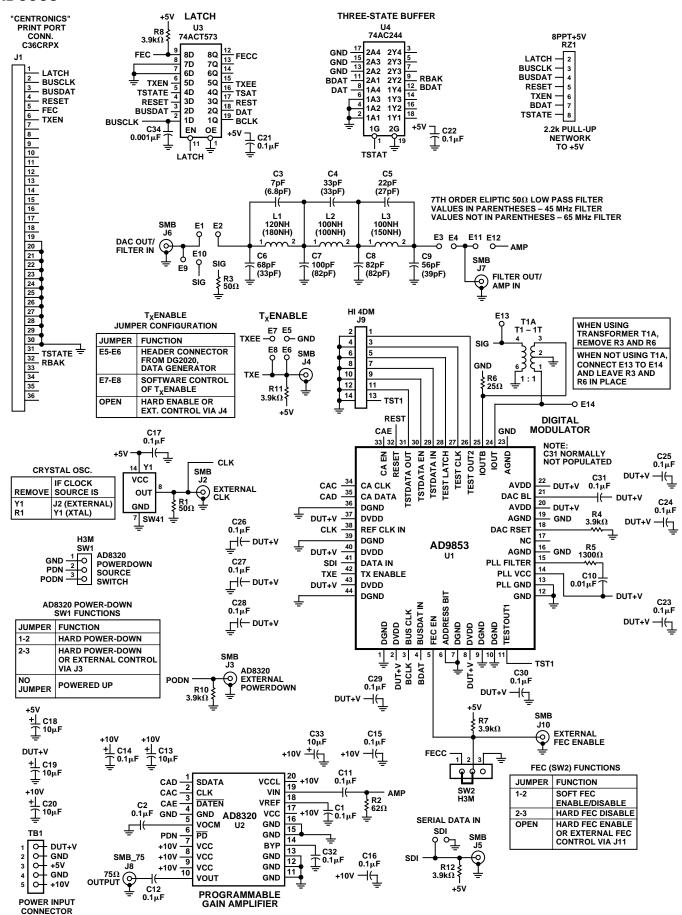

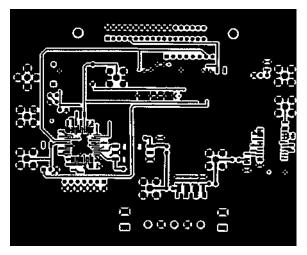

Figure 32. Basic Implementation of AD9853 Digital Modulator and AD8320 Programmable Cable Driver Amplifier in Return-Path Application

#### THEORY OF OPERATION

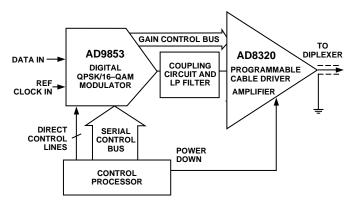

The AD9853 is a highly integrated modulator function that has been specifically designed to meet the requirements of the HFC upstream function for both interoperable and proprietary system implementations. The AD8320 is a companion cable driver amplifier with a digitally-programmable gain function, that interfaces to the AD9853 modulator and directly drives the cable plant with the modulated carrier. Together, the AD9853 and AD8320 provide an easily implementable transmitter solution for the HFC return-path requirement.

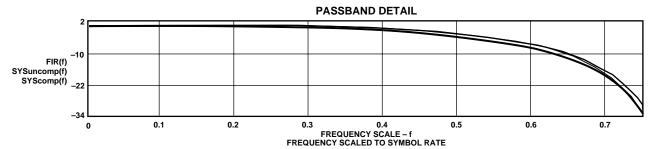

#### **CONTROL AND DATA INTERFACE**

As shown in the device's block diagram on the front page, the various transmit parameters, which include the input data rate, modulation format, FEC and randomizer configurations, as well as all the other modulator functions, are programmed into the AD9853 via a serial control bus. The AD8320 cable driver amp gain can be programmed directly from the AD9853 via a 3-wire bus by writing to the appropriate AD9853 register. The AD9853 also contains dedicated pins for FEC enable/disable and a RESET function.

Note: T<sub>X</sub>ENABLE pin must be held low for the duration of all serial control bus operations.

The AD9853's serial control bus consists of a bidirectional data line and a clock line. Communication is initiated upon a start condition, which is defined as a high-to-low transition of the data line while the clock is held high. Communication terminates upon a stop condition, which is defined as a low-to-high transition in the data line while the clock is held high. Ordinarily, the data line transitions only while the clock line is low to avoid a start or stop condition. Data is always written or read back in 8-bit bytes followed by a single acknowledge bit. The microcontroller or ASIC (i.e., the bus master) transfers eight data bits and the AD9853 (i.e., the slave) issues the acknowledge bit. The acknowledge bit is active low and is clocked out on every ninth clock pulse. The bus master must three-state the data line during the ninth clock pulse and allow the AD9853 to pull it low.

A valid write sequence consists of a minimum of three bytes. This means 27 clock pulses (three bytes with nine clock pulses each) must be provided by the bus master. The first byte is a chip address byte that is predefined except for Bit Positions 1 and 0. Bit Positions 7, 6, 5, 4 and 3 must be zero. Bit Position 2 must be a one. Bit 1 is set according to the external address pin on the AD9853 (1 if the pin is connected to +V<sub>S</sub>; 0 if the pin is grounded). Bit 0 is set to 1 if a read operation is desired, 0 if a write operation is desired. The second byte is a register address with valid addresses between 00h and 49h. An address which is outside of this range will not be acknowledged. The third byte is data for the address register. Multiple data bytes are allowed and loaded sequentially. That is, the first data byte is written to the addressed register and any subsequent data bytes are written to subsequent register addresses. It is permissible to write all registers by issuing a valid chip address byte, then an address byte of 00h and then 72 (48h) data bytes. Address 49h must be written independently, that is, not in conjunction with any other address.

A valid read sequence consists of a minimum of four bytes (refer to Figure 27). This means the bus master must provide 36 clock pulses (four bytes with nine clock pulses each). Like the write sequence, the first two bytes are the Chip Address Byte, with the

read/write bit set to 0, and the readback register address. After the slave provides an acknowledge at the end of the register address, the master must present a START condition on the bus, followed by the Chip Address Byte with the read/write bit set to a 1. The slave proceeds to provide an acknowledge. During the next eight clocks the slave will write to the bus from the register address. The master must provide an acknowledge on the ninth clock of this byte. Any subsequent clocks from the master will force the slave to read back from subsequent registers. At the end of the read-back cycle, the MASTER must force a "no-acknowledge" and then a STOP condition. This will take the SLAVE out of read-back mode. Not all of the serial control bus registers can be read back. Registers (06h–11h) and (1Eh–47h) are write only. Also, like the writing procedure, register 49h must be read from independently.

#### INPUT DATA SYNCHRONIZATION

The serial input data interface consists of two pins, the serial data input pin and a  $T_x ENABLE$  pin. The input data arrives at the bit rate and is framed by the  $T_x ENABLE$  signal as shown in Figure 26. A high frequency sampling clock continuously samples the  $T_x ENABLE$  signal to detect the rising edge. Once the rising edge of  $T_x ENABLE$  is detected, an internal sampler strobes the serial data at the correct point in time relative to the positive  $T_x ENABLE$  transition and then continues to sample at the correct interval based on the programmed Input Data rate. For proper synchronization of the AD9853, 1) the input burst data must be accurately framed by  $T_x ENABLE$  and 2) the input data rate must be an exact even submultiple of the system clock. Typically this will require that the input data rate clock be synchronized with reference clock.

#### **REED-SOLOMON ENCODER**

The AD9853 contains a programmable Reed-Solomon (R-S) encoder capable of generating an (N, K) code where N is the code word length and K is the message length.

Error correction becomes vital to reliable communications when the transmission channel conditions are less than ideal. The original message can be precisely reconstructed from a corrupted transmission as long as the number of message errors is within the encoder's limits. When forward error correction (FEC) is engaged, either through the serial control interface bus or hardware (logic high at Pin 5), it is implemented using the following MCNS-compatible field generator and primitive polynomials:

Primitive Polynomial:  $p(x) = x^8 + x^4 + x^3 + x^2 + 1$

Code Generator Polynomial:  $g(x) = (x + a^0)(x + a^1)(x + a^2)$ ...  $(x + a^{2t-1})$

The code-word structure is defined as follows:

N = K + 2t (bytes)

where:

N = code-word length

K = message length (in bytes), programmable from 16–255

t =number of byte errors that can be corrected programmable from 0-10.

A Code Word is the sum of the Message Length (in bytes) and number of Check Bytes required to correct byte errors at the

REV. A -15-

receive end. The values actually programmed on the serial control bus are "K" and "t," which will define N as shown in the above code-word structure equation. As can be seen from the code-word structure equation, two check bytes are required to correct each byte error. Setting t=0 and K>0 will bypass the Reed-Solomon encoding process.

Since Reed-Solomon works on bytes of information and not bits, a single byte error can be as small as one inverted bit out of a byte, or as large as eight inverted bits of one byte; in either instance the result is one byte error. For example, if the value "t" is specified as 5, the R-S FEC could be correcting as many as 40, or as few as 05, erroneous bits, but those errors must be contained in 5 message bytes. If the errors are spread among more than five bytes, the message will not be fully error corrected.

When using the R-S encoder, the message data needs to be partitioned or "gapped" with "don't care" data for the time duration of the check bytes as shown in the timing diagram of Figure 26. During the intervals between message data, the device ignores data at the input.

The position of the R-S encoder in the coding data path can be switched with the randomizer by exercising Register 1, Bit D3, via the serial control bus.

#### RANDOMIZER FUNCTION

The next stage in the modulation chain is the randomizing or "scrambling" stage. Randomizing is necessary due to the fact that impairments in digital transmission can be a function of the statistics of the digital source. Receiver symbol synchronization is more easily maintained if the input sequence appears random or equiprobable. Long strings of 0s or 1s can cause a bit or symbol synchronizer to lose synchronization. If there are repetitive patterns in the data, discrete spurs can be produced, causing interchannel interference. In modulation schemes relying on suppressed carrier transmission, nonrandom data can increase the carrier feedthrough. Using a randomizer effectively "whitens" the data.

The technique used in the AD9853 to randomize the data is to perform a modulo 2 logic addition of the data with a pseudorandom sequence. The pseudorandom sequence is generated by a shift register of length m with an exclusive OR combination of the nth bit and the last (mth) bit of the shift register that is fed back to the shift register input. By choosing the appropriate feedback point, a maximal length sequence is generated. The maximal length sequence will repeat after every  $2^m$  clock cycles, but appears effectively "random" at the output. The criterion for maximal length is that the polynomial  $1 + x^n + x^m$  be irreducible and prime over the Galois field. The AD9853 contains the following two polynomial configurations in hardware:

$x^{15} + x^{14} + 1$  :MCNS (DOCSIS) compatible.

$x^6 + x^5 + 1$  :DAVIC/DVB compatible.

The seed value is fully programmable for both configurations. The seed value is reset prior to each burst and is used to calculate the randomizer bit, which is combined in an exclusive XOR with the first bit of data from each burst. The first bit of data in a burst is the MSB of the first symbol following the last symbol of the internally generated preamble.

#### PREAMBLE INSERTION BLOCK

As shown in the block diagram of the AD9853, the circuit includes a programmable preamble insertion register. This register is 96 bits long and is transmitted upon receiving the  $T_XENABLE$  signal. It is transmitted without being Reed-Solomon encoded or scrambled. Ramp-up data, to allow for receiver synchronization, is included as the first bits in the preamble, followed by user burst profile or channel equalization information. The first bit of R-S encoded and scrambled information data is timed to immediately follow the last bit of preamble data.

For most modulation modes, a minimum preamble is required. This minimum is one symbol, two bits for DQPSK or four bits for either 16-QAM or D16-QAM. No preamble is required for either FSK or QPSK.

In conformance with DAVIC/DVB standards, the preamble is not differentially coded in DQPSK mode. However the preamble data can be differentially precoded when loaded into the preamble register. The last symbol of the preamble is used as the reference point for the first internal differentially coded symbol so the preamble and data will effectively be coded differentially. In the D16-QAM mode, the preamble is always differentially coded internally.

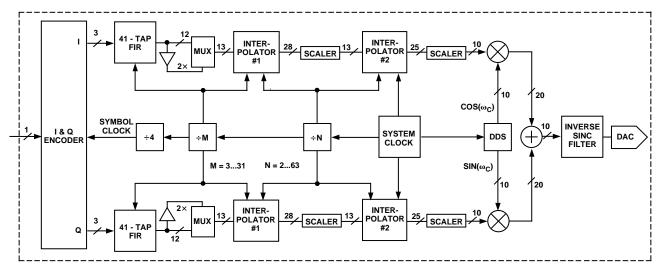

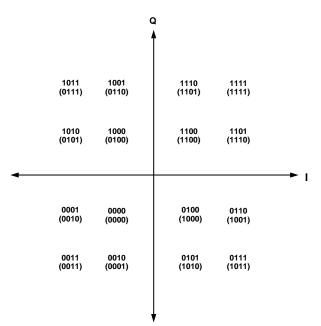

#### MODULATION ENCODER

The preamble, followed by the encoded and scrambled data is then modulation encoded according to the selected modulation format. The available modulation formats are FSK, QPSK, DQPSK, 16-QAM and D16-QAM. The corresponding symbol constellations support the interactive HFC cable specifications called out by MCNS (DOCSIS), 802.14 and DAVIC/DVB. The data arrives at the modulation encoder at the input bit rate and is demultiplexed as modulation encoded symbols into separate I and Q paths. For QPSK and DQPSK, the symbol rate is one-half of the bit rate and each symbol is comprised of two bits. For 16-QAM and D16-QAM, the symbol rate is onefourth the bit rate and each symbol is comprised of four bits. In the FSK mode, although the 1 and 0 data is entered into the serial data input, it effectively bypasses the encoding, scrambling and modulation paths. The FSK data is directly routed to the direct digital synthesizer (DDS) where it is used to switch the DDS between two stored tuning words (F0:F1) to achieve FSK modulation in a phase-continuous manner. By holding the input at either 1 or 0, a single frequency continuous wave can be output for system test or CW transmission purposes.

Differential encoding of data is frequently used to overcome phase ambiguity error or a "false lock" condition that can be introduced in carrier-recovery circuits used to demodulate the signal. In straight QPSK and 16-QAM, the phase of the received signal is compared to that of a "recovered carrier" of known phase to demodulate the signal in a coherent manner. If the phase of the recovered carrier is in error, then demodulation will be in error. Differential encoding of data at the transmit end eliminates the need for absolute phase coherency of the recovered carrier at the receive end. If a coherent reference generated by a phase lock loop experiences a phase inversion while demodulating in a differentially coded format, the errors would be limited to the symbol during which the inversion occurred and the following symbol. Differential coding uses the phase of the "previously transmitted symbol" as a reference point to compare to the current symbol. The change in phase from one symbol to

–16– REV. A

the next contains the message information and is used to demodulate the signal instead of the absolute phase of the signal. The transmitter and receiver must use the same symbol derivation scheme.

Differential encoding in the AD9853 occurs while data still exists as a serial data stream. When in straight QPSK or 16-QAM, the serial data stream passes to the symbol mapper/format encoder stage without modification. When differential encoding is engaged, the serial data stream is modified prior to the symbol mapper/format stage according to Table VI. Only I1 and Q1 are modified, even in the D16-QAM mode whose symbols are composed of Q1, I1, Q0, I0. In D16-QAM, only the two MSBs of the 4-bit symbol are modified; furthermore, the "previously transmitted symbol" referred to in Table VI are the two MSBs of the previous 4-bit symbol.

Symbol mapping for QPSK and DQPSK are identical. Symbol mapping for 16-QAM and D16-QAM are slightly different (see Figure 37) in accordance with MCNS (DOCSIS) specifications.

Special Note: For most modulation modes, a minimum preamble is required. For DQPSK the minimum preamble is one symbol (2 bits) and for either 16-QAM or D16-QAM the minimum preamble is one symbol (4 bits). For FSK or QPSK, no preamble is required.

User should be additionally aware that in the DQPSK mode, the preamble is not differentially encoded in accordance with MCNS (DOCSIS) specifications. If the preamble must be differentially encoded, it can "pre-encoded" using the derivation in Table VI. In D16-QAM, the preamble is always differentially encoded as is the "payload" data.

When initiating a new differentially encoded transmission, the "previously transmitted symbol" is always the last symbol of the preamble.

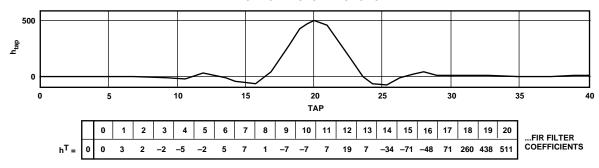

#### PROGRAMMABLE PULSE-SHAPING FIR FILTERS

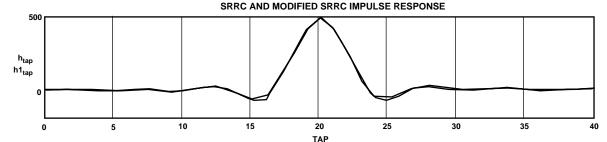

The I and Q data paths of the modulator each contain a pulse shaping filter. Each is a 41-tap, linear phase FIR. They are used to provide bandwidth containment and pulse shaping of the data in order to minimize intersymbol interference. The filter coefficients are programmable, so any realizable linear phase response characteristic may be implemented. The linear phase restriction is due to the fact that the user may only define the center coefficient and the lower 20 coefficients. The hardware fills in the upper 20 coefficients as a mirror image of the lower 20. This forces a linear phase response. It should also be noted that the pulse shaping filter upsamples the symbol rate by a factor of four.

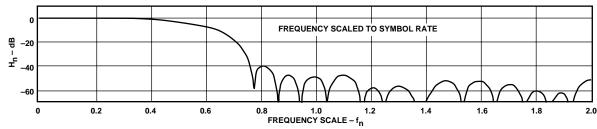

Normally, a *square-root raised cosine* (SRRC) response is desired. In fact, the AD9853 Evaluation Board software driver implements an SRRC response. When using the SRRC response, an excess bandwidth factor ( $\alpha$ ) is defined that affects the low pass roll-off characteristic of the filter (where  $0 \le \alpha \le 1$ ). When  $\alpha = 0$ , the SRRC is an ideal low-pass filter with a "brick wall" at one-half of the symbol rate (the Nyquist bandwidth of the data). Although this provides maximum bandwidth containment, it has the adverse affect of causing the tails of the time domain response to be large, which increases intersymbol interference (ISI). On the other hand, when  $\alpha = 1$ , the SRRC yields a smooth roll-off characteristic that significantly reduces the time domain tails, which improves ISI. Unfortunately, the cost of this benefit is a doubling of the bandwidth of the data signal. Values of  $\alpha$  between

0 and 1 yield a tradeoff between excess bandwidth in the frequency domain and tail suppression in the time domain.

The FIR filter coefficients for the SRRC response may be calculated using a variety of methods. One such method uses the *Inverse Fourier Transform Integral* to calculate the impulse response (time domain) from the SRRC frequency response (frequency domain). An example of this method is shown in Figure 33. Of course, this method requires that the SRRC frequency response be known beforehand.

The FIR filters in the AD9853 are implemented in hardware using a fixed point architecture of 10-bit, twos complement integers. Thus, each of the filter coefficients, a<sub>i</sub>, is an integer such that:

$$-512 \le a_i \le 511$$

[i = 0, 1, ..., 40]

#### PROGRAMMABLE INTERPOLATION FILTERS

The AD9853 employs two stages of interpolation filters in each of the I and Q channels of the modulator. These filters are implemented as Cascaded Integrator-Comb (CIC) filters. CIC filters are unique in that they not only provide a low-pass frequency response characteristic, but also provide the ability to have one sampling rate at the input and another sampling rate at the output. In general, a CIC filter may either be used as an interpolator (low-to-high sample rate conversion) or as a decimator (high-to-low sample rate conversion). In the case of the AD9853, the CIC filters are configured as interpolators, only. Furthermore, the interpolation is done in two separate stages with each stage designed so that the rate change is programmable. The first interpolator stage offers rate change ratios of 3 to 31, while the second stage offers rate change ratios of 2 to 63

As stated in the previous section, the data coming out of the FIR filters is oversampled by four. Spectral images appear at their output (a direct result of the sampling process). These images are replicas of the baseband spectrum which are repeated at intervals of four times the symbol rate (the rate at which the FIR filters sample the data). The images are an unwanted byproduct of the sampling process and effectively represent a source of noise.

Normally, the output of the FIR filters would be fed directly to the input of the I and Q modulator. This means that the spectral images produced by the FIRs would become part of the modulated signal—definitely not a desirable consequence. This is where the CIC filters play their role. Since they have a low-pass characteristic, they can be used to eliminate the spectral images produced by the FIRs.

#### Frequency Response of the CIC Filters

The frequency response of a CIC filter is predictable. It can be shown that the system function of a CIC filter is:

$$H(z) = \left(\sum_{k=0}^{RM-1} z^{-k}\right)^{N}$$

Where N is the number of cascaded integrator (or comb) sections, R is the rate change ratio, and M is the number of unit delays in each integrator/comb stage. For the AD9853, two of these variables are fixed as a result of the hardware implementation; specifically, N = 4 and M = 1. As mentioned earlier, R (the rate change ratio) is programmable.

REV. A -17-

#### SQUARE-ROOT RAISED COSINE (SRRC) FIR FILTER

#### COMPUTE AND PLOT SRRC FILTER COEFFICIENTS:

$$tap := 0..TAPS - 1 \qquad t_{tap} := \frac{1}{FreqScale} \cdot \left(tap - \frac{TAPS - 1}{2}\right) \qquad ...MAP \ THE \ FILTER \ TAP \ INDEX \ TO \ TIME \ DOMAIN (CENTERED \ AT T=0)$$

$$h(t) := \int_{0}^{BW} SRRC(f) \cdot cos(2 \cdot \pi \cdot f \cdot t) df \qquad ...INVERSE \ FOURIER \ INTEGRAL \ COMPUTE \ SRRC \ IMPULSE \ RESPONSE \ (TIME \ DOMAIN) \ FROM \ THE \ SRRC \ FREQUENCY \ RESPONSE \ (FREQUENCY \ DOMAIN). \ THE \ COS() \ FUNCTION \ REPLACES \ THE \ NORMAL \ COMPLEX \ EXPONENTIAL \ BECAUSE \ WE \ ARE \ RESTRICTED \ TO \ REAL \ FILTER \ COEFFICIENTS.$$

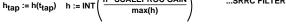

$$h := h(t, \cdot) \quad h := INT \left(h \cdot SCALEPROC \ GAIN\right) \qquad ...SRRC \ FILTER \ COEFFICIENTS \ INTEGERIZED \ AND \ SCALED$$

$$...SRRC \ FILTER \ COEFFICIENTS \ INTEGERIZED \ AND \ SCALED$$

#### SRRC IMPULSE RESPONSE

#### COMPUTE AND PLOT SRRC FREQUENCY RESPONSE:

freq\_pts := 250

$$\Delta f := \frac{0.5}{\text{freq_pts} - 1}$$

...DEFINE NUMBER OF FREQUENCY POINTS AND FREQUENCY STEP SIZE (FOR PLOTTING PURPOSES)

n := 0..freq\_pts - 1  $f_n := \Delta f \cdot n$  ...CREATE VECTOR OF UNIFORMLY SPACED FREQUENCY POINTS ( $f_{\text{max}} = 0.5$ ; A REQUIREMENT OF THE GAIN() FUNCTION),

K := (| gain(h,0) |)^{-1}  $H_n := K \cdot | \text{gain}(h,f_n) |$  ...NORMALIZED FREQUENCY RESPONSE

#### SRRC NORMALIZED FREQUENCY RESPONSE

#### **GLOBAL DECLARATIONS**

#### CONSTANTS: $\alpha \equiv 0.5$ ...EXCESS BANDWIDTH FACTOR FOR SRRC FREQUENCY RESPONSE $BW \equiv 0.5 \cdot (1 + \alpha)$ ...BANDWIDTH OF SRRC FILTER (RELATIVE TO SYMBOL RATE) ...PROCESSING GAIN OF CIC FILTERS (USED TO CORRELATE RESULTS WITH AD9853 EVAL. BD.) PROC\_GAIN 1 ...SETS MAX VALUE OF SRRC FILTER BASED ON FINITE WORD SIZE ...NUMBER OF FIR PULSE SHAPING FILTER TAPS SCALF = 511 TAPS = 41 $\mathsf{FreqScale} \equiv \mathsf{4}$ ...UPSAMPLING RATIO OF FIR PULSE SHAPING FILTER (RELATIVE TO THE SYMBOL RATE) **FUNCTIONS:** InRange $(x,a,b) \equiv (x \ge a) \cdot (x \le b)$ ...RETURNS 1 IF a <= x <= b, 0 OTHERWISE ...RETURNS NEAREST INTEGER TO x ...RATIO TO DECIBEL CONVERSION FUNCTION $INT(x) \equiv floor (x + 0.5)$ $dB(x) \equiv if (|x| = 0, 200, 20 \cdot log (|x|))$ SRRC(f) $\equiv$ passband $\leftarrow$ 0.5 · (1 - $\alpha$ ) stopband $\leftarrow$ 0.5 · (1 + $\alpha$ ) ...SRRC FREQUENCY RESPONSE FUNCTION (f IS RELATIVE TO THE SYMBOL RATE) if InRange (f, 0, stopband) 1 if InRange (f, 0, passband) $\left[- \cdot (2 \cdot f + \alpha - 1)\right]$ if InRange (f, passband, stopband)

Figure 33. Mathcad Simulation of a 41-Tap SRRC Filter

-18-

REV. A

The frequency response, H(f), of a CIC filter is found by evaluating H(z) at  $z = e^{j(2\pi f/R)}$ :

$$H(f) = \left(\sum_{k=0}^{RM-1} e^{-j(2\pi f/R)k}\right)^{N}$$

where f is relative to the input sample rate of the CIC filter. With this formula, we can accurately predict the frequency response of the CIC filters.

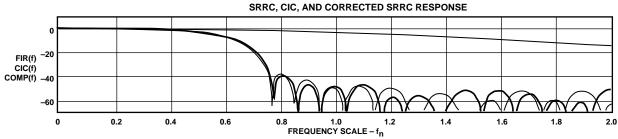

#### Compensating for CIC Roll-Off

As discussed previously, the CIC filters offer a low-pass characteristic that can be used to eliminate the spectral images produced by the FIR filters. Unfortunately, the CIC response is not flat over the frequency range of the baseband signal. Thus, the inherent attenuation (or roll-off) of the CIC filters distorts the baseband data signal. So even though the CIC filters help to eliminate the images described earlier, they introduce another form of error to the baseband signal—frequency-dependent amplitude distortion. This ultimately manifests itself as a higher level of Error Vector Magnitude (EVM) at the output of the I and Q modulator. Also, the larger the bandwidth of the baseband signal, the more pronounced the CIC roll-off, the greater the amplitude distortion and the worse the EVM performance. This is a serious problem because if a value of  $\alpha = 1$  is used for the SRRC response of the FIR filters, a doubling of the bandwidth of the baseband signal results and hence, a degradation in EVM performance.

Fortunately, there is a way to compensate for the effects of CIC roll-off. Since the frequency response of the CIC filters is predictable, it is possible to compensate for the CIC roll-off characteristic by adjusting the response of the FIR filters accordingly. The adjustment is accomplished by modifying the FIR filter response with a response that is the inverse of that of the CIC filters. This is done by precompensating the FIR filters.

To perform CIC compensation, we simply define a function  $(H_{\text{COMP}})$  that has a response which is the inverse of the CIC response. Specifically,

$$H_{COMP}(f) = \frac{1}{H(f)}$$

By multiplying the original FIR filter frequency response by  $H_{\text{COMP}}$ , we obtain the necessary compensation.

Unfortunately, it's not quite this simple. Recall that the coefficients of the baseband filter were computed using an inverse Fourier transform integral which included the SRRC function. In order to compensate for the CIC filter response, the SRRC function must be multiplied by the  $H_{\rm COMP}$  function. But the frequency scale of the SRRC response is computed based on frequencies relative to the symbol rate, while the  $H_{\rm COMP}$  function is computed relative to the input sampling rate of the CIC filter. The input CIC sampling rate happens to be the same as the sample rate of the FIR filter (see Figure 36), or four times the symbol rate. Thus, we have a frequency scaling problem.

This problem is easily corrected by introducing a frequency scaling factor (FreqScale = 4) into the  $H_{COMP}$  function so that

the frequency scales of the two functions match. Thus, the actual  $H_{\text{COMP}}$  function required is given by:

$$H_{COMP} = \frac{1}{H\left(\frac{f}{FreqScale}\right)}$$

It should be noted that in compensating for the CIC roll-off, only the first stage CIC filter need be considered. This is due to the fact that at the output of the first stage CIC filter the bandwidth of the signal is reduced to the point that the roll-off introduced by the second stage is negligible in the region of the baseband signal.

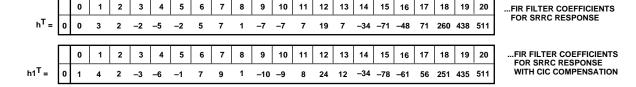

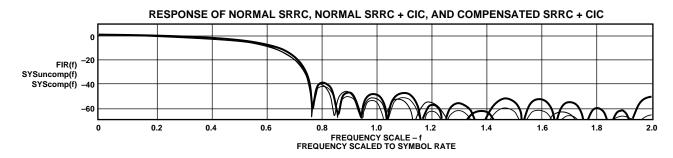

The CIC compensation method is demonstrated by example (using MathCad) in Figures 34 and 35. An interpolation rate (R) of 6 is used in the example. The improvement obtained by compensating for the CIC response is graphically demonstrated in Figure 35 which shows:

- the SRRC filter response (which is the desired overall response)

- the composite response of the SRRC in series with the CIC filter (distorted response)

- the composite response of the compensated SRRC in series with the CIC (corrected response)

Note that the ideal SRRC response and the compensated composite response are virtually identical in the region of the passband. Thus, the goal of correcting for the CIC filter response has been accomplished.

There is one subtlety to be noted in the example. The CIC compensation is only applied to the first 90% of the bandwidth of the baseband signal (note the variable  $\beta$  inside the integral). It was found that compensation over the full 100% of the bandwidth produced a reduction in the suppression of signals in the stopband region of the SRRC. This resulted in creating more distortion than by not correcting for the CIC roll-off in the first place. However, by slightly reducing the bandwidth over which correction is applied, the stopband suppression is once again restored and a significant improvement in EVM performance is obtained.

# **Determining the Necessary Interpolator Rate Change Ratio** The AD9853 contains three stages of digital interpolation:

- 1) Fixed 4× Pulse Shaping FIR Filter.

- 2) Programmable 3 to 31 First Interpolation Filter.

- 3) Programmable 2 to 63 Second Interpolation Filter.

After the serial input data stream has been encoded into QPSK or 16-QAM symbols, the symbol interpolation rate of the AD9853 is determined by the product of the three interpolating stages listed above. In QPSK mode, the minimum symbol interpolation rate that will work is  $4 \times 3 \times 2 = 24$ ; for 16-QAM the minimum is  $4 \times 4 \times 3 = 48$ . The maximum symbol interpolation rate is  $4 \times 31 \times 63 = 7812$ . The symbol rate at the encoder output for QPSK is equal to 1/2 the bit rate of the data and for 16-QAM it is 1/4 the bit rate. Figure 36 is a partial block diagram of the AD9853 and follows the path of the data stream from the input of the I and Q encoder block to the output of the DAC.

REV. A -19-

# MODIFICATION OF SQUARE-ROOT RAISED COSINE (SRRC) FIR FILTER RESPONSE TO COMPENSATE FOR CASCADED INTEGRATOR-COMB (CIC) FILTER RESPONSE

#### COMPUTE SRRC FILTER COEFFICIENTS:

$$tap := 0..TAPS - 1 \qquad t_{tap} := \frac{1}{FreqScale} \cdot \left(tap - \frac{TAPS - 1}{2}\right) \qquad ... \text{MAP THE FILTER TAP INDEX TO TIME DOMAIN (CENTERED AT t = 0)}$$

$$h(t) := \int_{0}^{BW} SRRC(f) \cdot cos(2 \cdot \pi \cdot f \cdot t) df \qquad \qquad ... \text{INVERSE FOURIER INTEGRAL COMPUTES SRRC IMPULSE RESPONSE (TIME DOMAIN) FROM THE SRRC FREQUENCY RESPONSE (FREQUENCY DOMAIN).}$$

$$THE COS() \text{ FUNCTION REPLACES THE NORMAL COMPLEX EXPONENTIAL BECAUSE WE ARE RESTICTED TO REAL FILTER COEFFICIENTS.}$$

$$... \text{SRRC FILTER COEFFICIENTS INTEGERIZED AND SCALED}$$

$$... \text{SRRC FILTER COEFFICIENTS INTEGERIZED AND SCALED}$$

# COMPUTE SRRC FILTER COEFFICIENTS MODIFIED FOR CORRECTION OF CIC RESPONSE:

R := 6 ...CIC INTERPOLATION RATIO (USER PROGRAMMABLE)

$$h1(t) := \int_{0}^{BW} SRRC (f) \cdot if \left( f \leq \beta \cdot BW, \right) \left( \frac{H(0,R)}{H\left(\frac{f}{FreqScale}, R\right)} \right) \left( \frac{1}{1} \right) \cdot cos(2 \cdot \pi \cdot f \cdot t) df \quad ...INVERSE FOLE \\ RESPONSE. \\ FRACTION O$$

...INVERSE FOURIER INTERGRAL MODIFIES THE SRRC RESPONSE BY THE RECIPROCAL OF THE NORMALIZED CIC FREQUENCY RESPONSE. THE MODIFICATION IS ONLY PERFORMED OVER THE FRACTION OF THE SRRC BANDWIDTH AS SPECIFIED BY  $\beta.$

$$h1_{tap} := h1(t_{tap})$$

$h1 := INT \left(\frac{h1 \cdot PROC\_GAINSCALE}{max(h1)}\right)$  ...MODIFIED SRRC FILTER COEFFICIENTS INTEGERIZED AND SCALED TO 10-BIT RANGE

#### DISPLAY FREQUENCY RESPONSE PLOTS:

...NORMALIZED FREQUENCY RANGE [A REQUIREMENT OF MATHCAD'S GAIN() FUNCTION] f:= 0.0.001.. 0.5 ... SCALE FACTORS TO ADJUST SRRC, SCALEsrrc := (| gain(h,0) |)<sup>-1</sup> SCALEcompsrrc :=  $(|gain(h1,0)|)^{-1}$ SCALEcic := (| H(0,R) |)-1 COMPENSATED SRRC, AND CIC FREQUENCY RESPONSES TO UNITY AT f = 0 SCALEcic := 7.716 · 10-4 SCALEsrrc := 5.559 · 10-4 SCALEcompsrrc := 5.79 · 10<sup>-4</sup> FIR(f) := dB(SCALEsrrc ' | gain(h,f) |) ...FUNCTION TO COMPUTE NORMALIZED, UNCOMPENSATED FIR RESPONSE (SRRC) IN dB ...FUNCTION TO COMPUTE NORMALIZED CIC RESPONSE IN dB  $CIC(f) := dB(SCALEcic \cdot | H(f,R) |)$ COMP(f) := dB(SCALEcompsrrc · | gain(h1,f) |) ....FUNCTION TO COMPUTE NORMALIZED, COMPENSATED FIR RESPONSE (SRRC + CIC<sup>-1</sup>) IN dB SYSuncomp(f) := FIR(f) + CIC(f) ...FUNCTION TO COMPUTE OVERALL SYSTEM RESPONSE OF SRRC AND CIC TOGETHER IN dB SYScomp(f) := COMP(f) + CIC(f)...FUNCTION TO COMPUTE OVERALL SYSTEM RESPONSE OF COMPENSATED SRRC AND CIC TOGETHER

Figure 34. Mathcad Simulation of 41-Tap SRRC Filter with CIC Compensation

-20-

REV. A

#### **GLOBAL DECLARATIONS**

```

CONSTANTS:

\alpha \equiv 0.5

...EXCESS BANDWIDTH FACTOR FOR SRRC FREQUENCY RESPONSE

\beta \equiv 0.9

...PORTION OF SRRC BANDWIDTH OVER WHICH APPLY CIC CORRECTION (0<\beta <= 1) ...BANDWIDTH OF SRRC FILTER (RELATIVE TO SYMBOLRATE)

\mathsf{BW} \equiv \mathsf{0.5} \cdot (\mathsf{1+\alpha})

...NUMBER OF FIR PULSE SHAPING FILTER TAPS

TAPS ≡ 41

...SETS MAX VALUE OF FIR PULSE SHAPING FILTER BASED ON FINITE WORD SIZE ...UPSAMPLING RATIO OF FIR PULSE SHAPING FILTER (RELATIVE TO THE SYMBOL RATE)

SCALE ≡ 511

\mathsf{FreqScale} \equiv \mathsf{4}

...PROCESSING GAIN OF CIC FILTERS (USED TO CORRELATE RESULTS WITH AD9853 EVAL. BD.)

PROC_GAIN≡1

...NUMBER OF COMB/INTEGRATOR STAGES IN CIC FILTER

M≡1

...UNIT DELAYS PER STAGE OF CIC FILTER

FUNCTIONS:

\overline{\text{InRange } (x,a,b) \equiv (x \ge a) \cdot (x \le b)}

...RETURNS 1 IF a<= x <= b, 0 OTHERWISE

...RETURNS NEAREST INTEGER TO X

...RATIO TO DECIBEL CONVERSION FUNCTION

INT(x) \equiv floor(x + 0.5)

dB(x) \equiv if(|x| = 0, -200, 20 \cdot log(|x|))

...Z TRANSFORM

z(f) \equiv e^{2j \cdot \pi \cdot f}

SRRC(f) = passband \leftarrow 0.5 \cdot (1 - \alpha)

stopband \leftarrow 0.5 \cdot (1 + \alpha)

...SRRC FREQUENCY RESPONSE FUNCTION (f IS RELATIVE TO THE SYMBOL RATE)

1 if InRange (f, 0, stopband)

if InRange (f, 0, passband)

_ 1) if InRange (f, passband, stopband)

...CIC FILTER TIME INDEX FREQUENCY RESPONSE FUNCTION

```

Figure 35. MathCad Simulation (Continued)

REV. A –21–

Figure 36. Block Diagram of AD9853 Data Path and Clock Stages

The goal of interpolation is to up-sample the baseband information to the system clock rate and to suppress aliases in the passband. The system clock rate is the sample rate of the sine and cosine signal carriers generated by the DDS in the quadrature modulator stage. Alias suppression is accomplished by the CIC filters as described previously. For timing synchronization, the overall interpolation rate must be set such that the bit rate of the baseband signal be an even integer factor of the system clock rate. The importance of the relationship between the data and system clock rates can not be overstressed. It is restated here for clarity:

The SYSTEM CLOCK RATE must be an EVEN INTEGER MULTIPLE of the DATA BIT RATE.

Following is a design example that demonstrates the principles outlined above.

System Requirements:

Baseband Bit Rate

Carrier Frequency

Modulation Scheme

System Power

1.024 Mb/s

49 MHz

16-QAM

3.3 V

It should be noted that with a 3.3 V power supply, the maximum system clock rate of the AD9853 is 126 MHz. This sets an upper bound on the system clock.

The first consideration is to make sure that the required carrier frequency is within the AD9853's output frequency range. The carrier frequency should be  $\leq 40\%$  of the system clock rate. The given carrier frequency requirement of 49 MHz means that a minimum system clock rate of 122.5 MHz is required; a value within the range of the AD9853's 126 MHz capability.

We must next ensure that the system clock rate is an even integer multiple of the input bit rate. Dividing the system clock rate (122.5 MHz) by the data rate (1.024 Mbps) yields 119.63. Obviously this is not an integer, so we must select the nearest even integer value (in this case, 120) as the data rate multiplier. Thus, a system clock rate of 122.88 MHz is required (120  $\times$  1.024 Mbps). With 6× REFCLK engaged, the reference clock input will be 1/6th of the system clock rate, or 20.48 MHz.

Finally, the two interpolator rates must be determined. Since the FIR filter and interpolator stages will be operating on 16-QAM symbols, the data rate must be converted from bits/second to symbols/second (baud). Each 16-QAM symbol is composed of four serial data bits. Therefore, the baud rate at the input to the FIR filter is 1.024 Mbps/4=256k baud. The FIR pulse shaping filters up-sample by a factor of 4. This fixes the FIR sample clock at 256k baud  $\times$  4, or 1.024 MSPS. With the FIR sampling at a 1.024 MSPS rate, and a previously determined system clock rate of 122.88 MHz, the interpolators must up-sample by a factor of 120 (122.88/1.024=120).

Rule of Thumb: divide the interpolating burden as equally as possible among the two interpolators.

Since the required rate change ratio is 120, select a value of 10 for interpolator #1 and 12 for interpolator #2 ( $10 \times 12 = 120$ ). This satisfies the requirements for the two programmable interpolator stages.

Thus far we have established the rate change ratios for the interpolators. However, there is an additional consideration. By default, the interpolators have an intrinsic gain (or loss) that is dependent on the selected interpolation rate. Since there is the potential to have overall CIC gains of greater than unity, care must be taken to avoid the occurrence of overflow in the interpolators.

#### **Interpolator Scaling**

Proper signal processing in the AD9853 depends on data propagating through the pulse-shaping filter and interpolator stages with as flat a baseband response as possible. In addition to the frequency response issue, it is also necessary to ensure that the numerical data propagating through the interpolators does not result in an overflow condition.

As mentioned earlier, the interpolators are implemented using a CIC filter. In the AD9853, the CIC filter is designed using fixed-point processing and two cascaded CIC filter sections (Interpolator #1 and Interpolator #2). It is important to understand that in a CIC filter, the integration portion of the circuit will require the accumulation of values based on the rate change factor, R. This means that the size of the data word grows in a manner dependent on the choice of R. In the case of Interpolator #1, the circuit is designed around a maximum R of 32 and this results in an output register width of 28 bits. The design of Interpolator #2 requires an output register width of 25 bits.