## 10–Bit, 208 MSPS A/D Converter

## Preliminary Technical Data

2/25/00

## AD9410

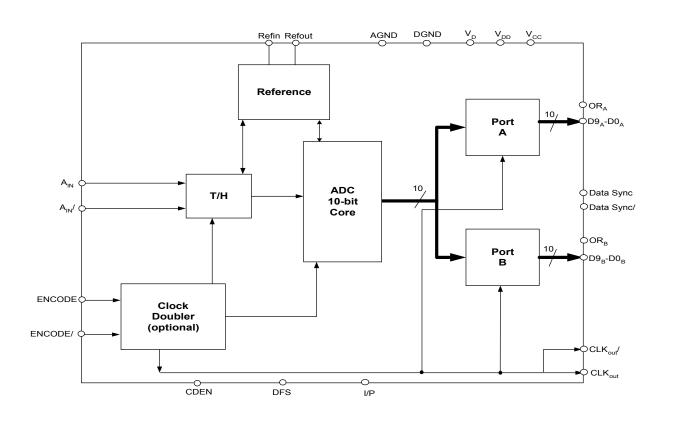

The AD9410 is an 10-bit monolithic sampling analog-to-digital converter with an on-chip track-and-hold circuit and is optimized for high speed conversion and ease of use. The product operates at a 208 Msps conversion rate with outstanding dynamic performance over its full operating range.

The ADC requires a single 5.0V and 3.3V power supply and up to a 208MHz differential clock input for full–performance operation. No external reference or driver components are required for many applications. The digital outputs are TTL/CMOS compatible and a separate output power supply pin supports interfacing with 3.3V logic.

The clock input is differential and TTL/CMOS compatible. The 10-bit digital outputs can be operated from +3.3V (2.5V to 3.6V) supplies. An on-chip clock doubler allows up to 208 Msps conversion rates with a 104MHz input clock. Two output buses support demultiplexed data up to 104 Msps rates.

Fabricated on an advanced BiCMOS process, the AD9410 is available in a 80 pin surface mount plastic package (80 Power2 Quad) specified over the industrial temperature range (-40°C to +85°C).

#### FEATURES

10-Bit, 208Msps ADC On-Chip Reference and Track/Hold Selectable on-chip clock doubler 500 MHz Analog Bandwidth SNR = 54dB with 99MHz analog input 1.5 Vp-p Analog Input Range +5.0V and +3.3V Supply Operation +3.3V CMOS/TTL outputs Power: 1.8 W Typical at 208 Msps Demultiplexed outputs each at 104 Msps Output data format option Data Sync input and Data Clock output provided Interleaved or parallel data output option.

#### APPLICATIONS

Communications and Radar Basestations and 'Zero-IF' subsystems Wireless Local Loop (WLL) Local Multipoint Distribution Service (LMDS) High-End Imaging Systems and projectors

#### REV. PrB

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. © Analog Devices, Inc., 2000

One Technology Way, P.O Box 9106, Norwood, MA 02062–9106, USA Tel: 617/329–4700 Fax: 617–326–8703

# **AD9410—TARGET SPECIFICATIONS**

ELECTRICAL CHARACTERISTICS<sup>1</sup> (V<sub>DD</sub> = 3.0V, V<sub>CC</sub> = 5.0V; external reference; Clock input = 208 Msps, unless otherwise noted)

| <b>D</b>                                    |       | Test  |                      | D9410BS   |                  | <b>.</b>   |

|---------------------------------------------|-------|-------|----------------------|-----------|------------------|------------|

| Parameter                                   | Temp  | Level | Min                  | Typical   | Max              | Units      |

| RESOLUTION                                  |       |       |                      | 10        |                  | bits       |

| DC ACCURACY                                 |       |       |                      |           |                  |            |

| Differential Nonlinearity                   | +25°C | Ι     |                      | $\pm 1.0$ |                  | LSB        |

|                                             | Full  | VI    |                      |           |                  | LSB        |

| Integral Nonlinearity                       | +25°C | Ι     |                      | ±1.0      |                  | LSB        |

|                                             | Full  | VI    |                      |           |                  | LSB        |

| Gain Error                                  | +25°C | Ι     |                      | ±2        |                  | % FS       |

|                                             | Full  | VI    |                      |           |                  | % FS       |

| Gain Tempco                                 | Full  | V     |                      | 100       |                  | ppm/°C     |

| ANALOG INPUT                                |       |       |                      |           |                  |            |

| Input Voltage Range                         | Full  | V     |                      | ±768      |                  | mV p–p     |

| (with respect to AIN))                      |       |       |                      |           |                  |            |

| Common Mode Voltage                         | Full  | V     |                      | 3.0       |                  | V          |

| Input Offset Voltage                        | +25°C | Ι     |                      |           |                  | mV         |

|                                             | Full  | Ι     |                      |           |                  | mV         |

| Reference Voltage                           | +25°C | Ι     | 2.4                  | 2.5       | 2.6              | V          |

| Input Resistance                            | +25°C | Ι     | 700                  | 850       | 1100             | Ω          |

|                                             | Full  | Ι     | 700                  | 850       | 1100             | Ω          |

| Input Capacitance                           | +25°C | V     |                      | 3         |                  | pF         |

| Input Bias Current                          | +25°C | Ι     |                      | 4         |                  | μA         |

| 1                                           | Full  | Ι     |                      |           |                  | μA         |

| Analog Bandwidth, Full Power                | +25°C | V     |                      | 500       |                  | MHz        |

| SWITCHING PERFORMANCE                       | -20 0 | •     |                      |           |                  |            |

| Maximum Conversion Rate                     | Full  | VI    | 200                  |           |                  | Msps       |

| Minimum Conversion Rate                     | Full  | IV    |                      |           | 100              | Msps       |

| Encode Pulse Width High (t <sub>EH</sub> )  | +25°C | IV    |                      |           |                  | ns         |

| Encode Pulse Width Low $(t_{EL})$           | +25°C | IV    |                      |           |                  | ns         |

| Aperture Delay $(t_A)$                      | +25°C | V     |                      | 0.85      |                  | ns         |

| Aperture Uncertainty (Jitter)               | +25°C | V     |                      | 1.0       |                  | ps rms     |

| Output Valid Time $(t_V)$                   | Full  | VI    | 4.0                  |           |                  | ns         |

| Output Propagation Delay (t <sub>PD</sub> ) | Full  | VI    |                      |           | 7.0              | ns         |

| Output Rise Time $(t_R)$                    | Full  | VI    |                      | 1.8       | $\boldsymbol{X}$ | ns         |

| Output Fall Time $(t_F)$                    | Full  | VI    |                      | 1.4       |                  | ns         |

| DIGITAL INPUTS                              |       |       |                      |           |                  |            |

| Logic "1" Voltage                           | Full  | IV    |                      |           | Č,               | V          |

| Logic "0" Voltage                           | Full  | IV    |                      |           |                  | V          |

| Logic "1" Current                           | Full  | VI    | Y                    |           | $\pm 10$         | μA         |

| Logic "0" Current                           | Full  | VI    |                      |           | ±10              | μA         |

| Input Capacitance                           | +25°C | V     |                      | 3         |                  | pF         |

| DIGITAL OUTPUTS                             |       |       |                      |           |                  | 1          |

| Logic "1" Voltage ( $V_{DD} = +3.3V$ )      | Full  | VI    | V <sub>DD</sub> -0.5 |           |                  | V          |

| Logic "0" Voltage $(V_{DD} = +3.3V)$        | Full  | VI    | . 00 0.0             |           | 0.05             | v          |

| Output Coding                               |       |       | Binary or            | Two's Co  |                  | ľ          |

| POWER SUPPLY                                |       |       |                      |           | r                |            |

| Power Dissipation                           | Full  | VI    |                      | 1.8       |                  | W          |

| Power Supply Rejection Ratio                | +25°C | I     |                      | 1.0       |                  | mV/V       |

| (PSRR)                                      |       |       |                      |           |                  | ···· , , , |

| Parameter                          | Тетр  | Test<br>Level | AD9410BSQ<br>Min Typical Max | Units    |

|------------------------------------|-------|---------------|------------------------------|----------|

|                                    | remp  | Level         | ivini Typicai iviax          | Cints    |

| DYNAMIC PERFORMANCE                | 12590 | 17            | 4.0                          |          |

| Transient Response                 | +25°C | V             | tbf                          | ns<br>ns |

| Overvoltage Recovery Time          | +25°C | V             | tbf                          |          |

| Signal-to-Noise Ratio (SNR)        |       |               |                              |          |

| (Without Harmonics)                |       |               |                              |          |

| $f_{IN} = 41 \text{ MHz}$          | +25°C | Ι             | 55                           | dB       |

| $f_{IN} = 100 \text{ MHz}$         | +25°C | Ι             | 54                           | dB       |

| Signal-to-Noise Ratio (SINAD)      |       |               |                              |          |

| (With Harmonics)                   |       |               |                              |          |

| $f_{IN} = 41 \text{ MHz}$          | +25°C | Ι             | 54                           | dB       |

| $f_{IN} = 100 \text{ MHz}$         | +25°C | Ι             | 53                           | dB       |

| Effective Number of Bits           |       |               |                              |          |

| $f_{IN} = 41 \text{ MHz}$          | +25°C | Ι             | 8.6                          | bits     |

| $f_{IN} = 100 \text{ MHz}$         | +25°C | Ι             | 8.5                          | bits     |

| 2nd Harmonic Distortion            |       |               |                              |          |

| $f_{IN} = 41 \text{ MHz}$          | +25°C | Ι             | 65                           | dBc      |

| $f_{IN} = 100 \text{ MHz}$         | +25°C |               | 65                           | dBc      |

| 3rd Harmonic Distortion            |       |               |                              |          |

| $f_{IN} = 41 \text{ MHz}$          | +25°C | I             | 65                           | dBc      |

| $f_{\rm IN} = 100 \text{ MHz}$     | +25°C | Ĩ             | 65                           | dBc      |

| Two–Tone Intermod Distortion (IMD) |       |               |                              |          |

| $f_{IN} = 41 \text{ MHz}$          | +25°C | v             | 58                           | dBc      |

| $f_{IN} = 100 \text{ MHz}$         | +25°C | v             | 58                           | dBc      |

NOTES

1

Target Specifications only for product development purposes. On-chip clock doubler supports encode rates from 190Msps to 208Msps, which translates into 95MHz to 104MHz clock input. 2.

#### **ORDERING GUIDE**

| Model                    | Temperature<br>Range    | Package Option   |

|--------------------------|-------------------------|------------------|

| AD9410BSQ<br>AD9410-EVAL | -40°C to +85°C<br>+25°C | Evaluation Board |

| AD9410-EVAL              | 723 C                   | Evaluation Board |

\*

#### **EXPLANATION OF TEST LEVELS**

#### **Test Level**

- I 100% production tested.

- Π 100% production tested at +25°C and sample tested at specified temperatures.

- Ш Sample tested only.

- IV Parameter is guaranteed by design and characterization testing.

- V Parameter is a typical value only.

- VI 100% production tested at +25°C; guaranteed by design and characterization testing for industrial temperature range.

### ABSOLUTE MAXIMUM RATINGS\*

| V <sub>D</sub>               | +4 V                                   |

|------------------------------|----------------------------------------|

| V <sub>cc</sub>              | +6 V                                   |

| V <sub>DD</sub>              |                                        |

| Analog Inputs                | $0V$ to $V_{CC} + 0.5 V$               |

| Digital Inputs               | $\dots 0$ V to V <sub>DD</sub> + 0.5 V |

| VREF IN                      | $0V$ to $V_{\rm D} + 0.5$ V            |

| Digital Output Current       | 20 mA                                  |

| Operating Temperature        | $-55^{\circ}C$ to $+125^{\circ}C$      |

| Storage Temperature          | $-65^{\circ}C$ to $+150^{\circ}C$      |

| Maximum Junction Temperature | +175°C                                 |

| Maximum Case Temperature     | +150°C                                 |

\* Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions outside of those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

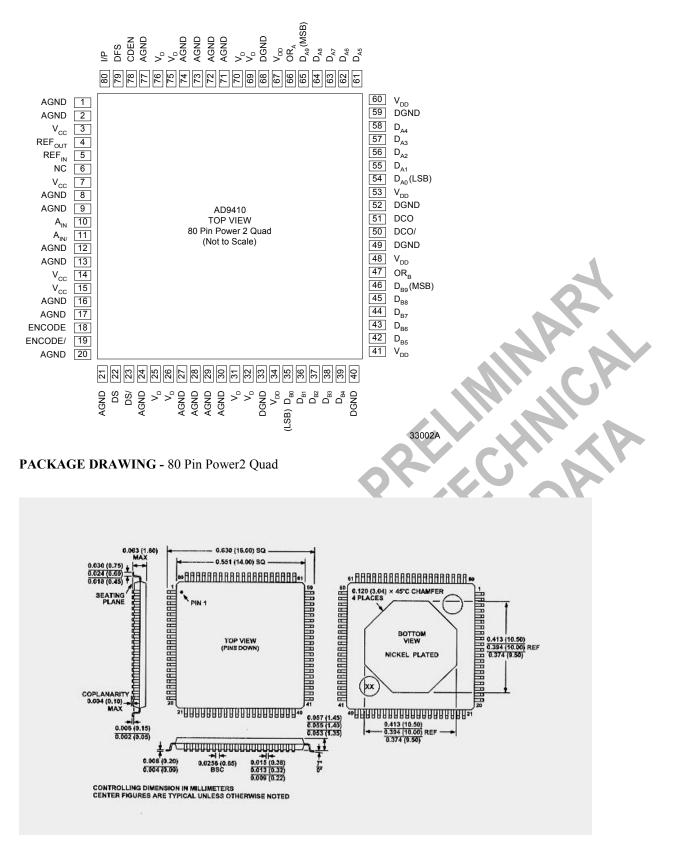

#### PIN DESCRIPTIONS

| Pin Number                                                  | Name                    | Function                                                                                                                                                                                                                                                                                                    |  |

|-------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1,2,8,9,12,13,16,17,20,21,24,<br>27,28,29,30,71,72,73,74,77 | AGND                    | Analog ground.                                                                                                                                                                                                                                                                                              |  |

| 4                                                           | REF <sub>OUT</sub>      | Internal Reference output.                                                                                                                                                                                                                                                                                  |  |

| 5                                                           | REF <sub>IN</sub>       | Internal Reference input.                                                                                                                                                                                                                                                                                   |  |

| 6                                                           | NC                      | Do not connect.                                                                                                                                                                                                                                                                                             |  |

| 3,7,14,15                                                   | V <sub>CC</sub>         | 5V supply. (regulated to within +/- 10%)                                                                                                                                                                                                                                                                    |  |

| 10                                                          | A <sub>IN</sub>         | Analog input – true.                                                                                                                                                                                                                                                                                        |  |

| 11                                                          | A <sub>IN/</sub>        | Analog input – compliment.                                                                                                                                                                                                                                                                                  |  |

| 18                                                          | ENCODE                  | Clock input – true.                                                                                                                                                                                                                                                                                         |  |

| 19                                                          | ENCODE/                 | Clock input – compliment.                                                                                                                                                                                                                                                                                   |  |

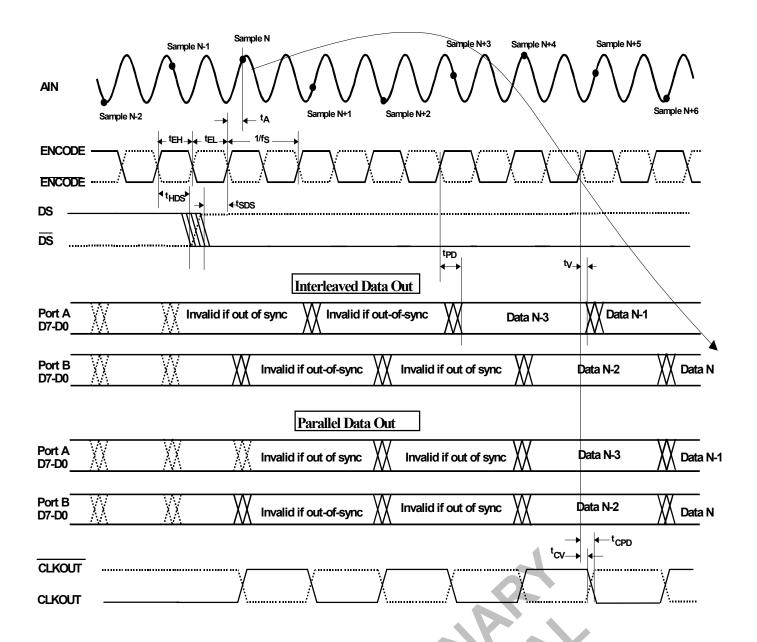

| 22                                                          | DS                      | Data sync (input) – true. Aligns output channels so that data from channel<br>B represents a sample that is prior from data in channel A, taking into<br>account the pipeline delay. (See timing diagram). Tie LOW if not used.                                                                             |  |

| 23                                                          | DS/                     | Data sync (input) – compliment. Tie HIGH if not used.                                                                                                                                                                                                                                                       |  |

| 25,26,31,32,69,70,75,76                                     | V <sub>D</sub>          | 3.3V analog supply. (regulated to within +/- 5%)                                                                                                                                                                                                                                                            |  |

| 33,40,49,52,59,68                                           | DGND                    | Digital ground.                                                                                                                                                                                                                                                                                             |  |

| 34,41,48,53,60,67                                           | V <sub>DD</sub>         | 3.3V digital output supply.                                                                                                                                                                                                                                                                                 |  |

| 35-39                                                       | $D_{\rm B0}-D_{\rm B4}$ | Digital data output for channel B. (LSB=DB <sub>0</sub> )                                                                                                                                                                                                                                                   |  |

| 42-46                                                       | $D_{B5}-D_{B9}$         | Digital data output for channel B (MSB=DB <sub>9</sub> ).                                                                                                                                                                                                                                                   |  |

| 47                                                          | OR <sub>B</sub>         | Data over range for channel B.                                                                                                                                                                                                                                                                              |  |

| 50                                                          | DCO/                    | Clock output – compliment.                                                                                                                                                                                                                                                                                  |  |

| 51                                                          | DCO                     | Clock output – true.                                                                                                                                                                                                                                                                                        |  |

| 54-58                                                       | $D_{A0}-D_{A4}$         | Digital data output for channel A. $(LSB = DA_0)$                                                                                                                                                                                                                                                           |  |

| 61-65                                                       | $D_{A5} - D_{A9}$       | Digital data output for channel A. (MSB=DA <sub>9</sub> ).                                                                                                                                                                                                                                                  |  |

| 66                                                          | OR <sub>A</sub>         | Data over range for channel A.                                                                                                                                                                                                                                                                              |  |

| 78                                                          | CDEN                    | Clock doubler enable. HIGH = Enable, samples at 2X rate when ENCODE = 100Msps +/-5%. LOW = Not enabled                                                                                                                                                                                                      |  |

| 79                                                          | DFS                     | Data format select. HIGH = Two's compliment, LOW = Binary.                                                                                                                                                                                                                                                  |  |

| 80                                                          | I/P                     | Interlaced or parallel output mode. HIGH = data arrives in channel A at falling edge of clock and data arrives in channel B at rising edge of clock (It is recommended to place a 6k ohm resistor between the pin and the HIGH 5V supply.), LOW = data arrives in channels A and B at rising edge of clock. |  |

#### PIN CONFIGURATION

Note: It is recommended not to place trace lines underneith for future migration to a lower cost package

### AD9410

Figure 1. Timing Diagram – Dual Channel Mode with Clock Doubler Disabled.

ELCHN!

#### Erratta

| Date    | Revision | Changes to Datasheet                                                                                                                    |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 2/18/99 | R0.3     | Removed Pinout and pin desicription. They have changed due to heat dissipation concerns. To be finalized.                               |

| 4/12/99 | R0.4     | Added pin out, pin description, pin configuration and package drawing. Updated ordering part number and target AC specifications.       |

| 4/30/99 | R0.5     | Updated package drawing, front page copy and block diagram, page 2 specs, absolute max's, polarity definitions of DFS and I/P switched. |

| 9/16/99 | R0.6     | Eval board part number, updated package drawing.                                                                                        |

| 2/15/00 | R0.7     | Changed Pin 6 to do not connect.                                                                                                        |

| 2/25/00 | R0.8     | Updated speed to 208Msps. Noted clock doubler operation window. Changed data sync definition.<br>Inserted timing diagram                |

|         |          |                                                                                                                                         |