# High Speed Oversampling CMOS ADC w/16-Bit Resolution at a 2.5 MHz Output Word Rate

# AD9260

#### FEATURES

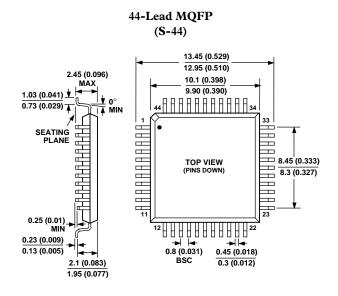

Monolithic 16-Bit, Oversampled A/D Converter 8× Oversampling Mode, 20 MSPS Clock 2.5 MHz Output Word Rate 1.01 MHz Signal Passband w/0.004 dB Ripple Signal-to-Noise Ratio: 88.5 dB Total Harmonic Distortion: -96 dB Spurious Free Dynamic Range: 100 dB Input Referred Noise: 0.6 LSB Selectable Oversampling Ratio:  $1 \times, 2 \times, 4 \times, 8 \times$ Selectable Power Dissipation: 150 mW to 585 mW 85 dB Stopband Attenuation 0.004 dB Passband Ripple Linear Phase Single +5 V Analog Supply, +5 V/+3 V Digital Supply Synchronize Capability for Parallel ADC Interface **Twos-Complement Output Data** 44-Lead MQFP

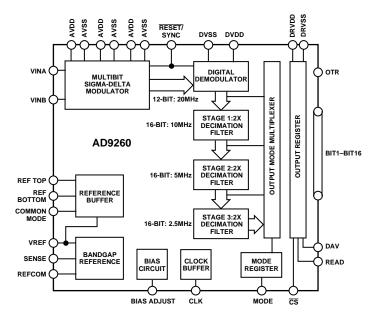

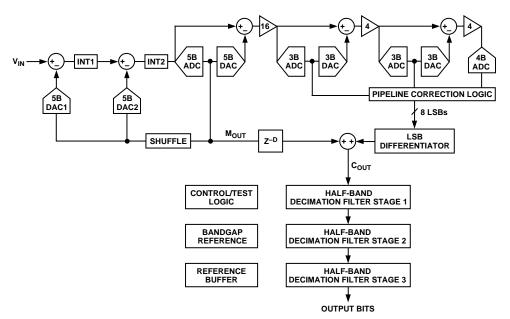

#### FUNCTIONAL BLOCK DIAGRAM

#### **PRODUCT DESCRIPTION**

The AD9260 is a 16-bit, high speed oversampled analog-todigital converter (ADC) that offers exceptional dynamic range over a wide bandwidth. The AD9260 is manufactured on an advanced CMOS process. High dynamic range is achieved with an oversampling ratio of 8× through the use of a proprietary technique that combines the advantages of sigma-delta and pipeline converter technologies.

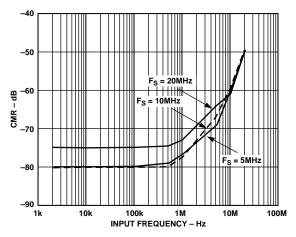

The AD9260 is a switched-capacitor ADC with a nominal fullscale input range of 4 V. It offers a differential input with 60 dB of common-mode rejection of common-mode signals. The signal range of each differential input is  $\pm 1$  V centered on a 2.0 V common-mode level.

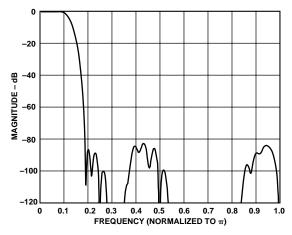

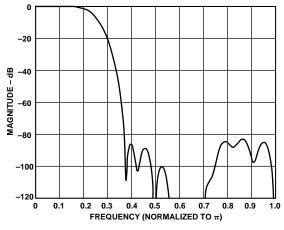

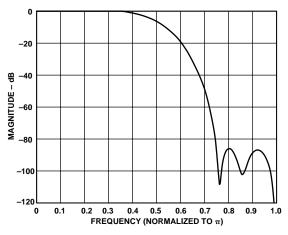

The on-chip decimation filter is configured for maximum performance and flexibility. A series of three half-band FIR filter stages provide  $8\times$  decimation filtering with 85 dB of stopband attenuation and 0.004 dB of passband ripple. An onboard digital multiplexer allows the user to access data from the various stages of the decimation filter.

The on-chip programmable reference and reference buffer amplifier are configured for maximum accuracy and flexibility. An external reference can also be chosen to suit the users specific dc accuracy and drift requirements.

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

The AD9260 operates on a single +5 V supply, typically consuming 585 mW of power. A power scaling circuit is provided allowing the AD9260 to operate at power consumption levels as low as 150 mW at reduced clock and data rates. The AD9260 is available in a 44-lead MQFP package and is specified to operate over the industrial temperature range.

#### **PRODUCT HIGHLIGHTS**

The AD9260 is fabricated on a very cost effective CMOS process. High speed, precision mixed-signal analog circuits are combined with high density digital filter circuits.

The AD9260 offers a complete single-chip 16-bit sampling ADC with a 2.5 MHz output data rate in a 44-lead MQFP.

**Selectable Internal Decimation Filtering**—The AD9260 provides a high performance decimation filter with 0.004 dB passband ripple and 85 dB of stopband attenuation. The filter is configurable with options for  $1\times$ ,  $2\times$ ,  $4\times$ , and  $8\times$  decimation.

**Power Scaling**—The AD9260 consumes a low 585 mW of power at 16-bit resolution and 2.5 MHz output data rate. Its power can be scaled down to as low as 150 mW at reduced clock rates.

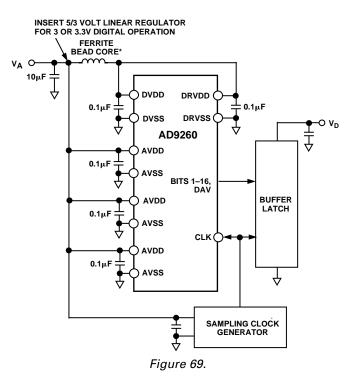

**Single Supply**— Both of the analog and digital portions of the AD9260 can operate off of a single +5 V supply simplifying system power supply design. The digital logic will also accommodate a single +3 V supply for reduced power.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site: http://www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 1998

# AD9260-SPECIFICATIONS

# **CLOCK INPUT FREQUENCY RANGE**

| Parameter—Decimation Factor (N)                          | AD9260 (8) | AD9260 (4) | AD9260 (2) | AD9260 (1) | Units   |

|----------------------------------------------------------|------------|------------|------------|------------|---------|

| CLOCK INPUT (Modulator Sample Rate, $f_{\text{CLOCK}}$ ) | 1          | 1          | 1          | 1          | kHz min |

|                                                          | 20         | 20         | 20         | 20         | MHz max |

| OUTPUT WORD RATE (FS = $f_{CLOCK}/N$ )                   | 0.125      | 0.250      | 0.500      | 1          | kHz min |

|                                                          | 2.5        | 5          | 10         | 20         | MHz max |

Specifications subject to change without notice

# **DC SPECIFICATIONS** (AVDD = +5 V, DVDD = +3 V, DRVDD = +3 V, $f_{CLOCK}$ = 20 MSPS, $V_{REF}$ = +2.5 V, Input CML = 2.0 V $T_{MIN}$ to $T_{MAX}$ unless otherwise noted, $R_{BIAS}$ = 2 k $\Omega$ )

| Parameter—Decimation Factor (N)                 | AD9260 (8)          | AD9260 (4)      | AD9260 (2)      | AD9260 (1)        | Units                               |

|-------------------------------------------------|---------------------|-----------------|-----------------|-------------------|-------------------------------------|

| RESOLUTION                                      | 16                  | 16              | 16              | 12                | Bits min                            |

| INPUT REFERRED NOISE (TYP)                      |                     |                 |                 |                   |                                     |

| 1.0 V Reference<br>2.5 V Reference <sup>1</sup> | 1.40<br>0.68 (90.6) | 2.4<br>1.2 (86) | 6.0<br>3.7 (76) | 1.3<br>1.0 (63.2) | LSB rms typ<br>LSB rms typ (dB typ) |

| ACCURACY                                        |                     |                 |                 |                   |                                     |

| Integral Nonlinearity (INL)                     | ±0.75               | ±0.75           | ±0.75           | ±0.3              | LSB typ                             |

| Differential Nonlinearity (DNL)                 | ±0.50               | $\pm 0.50$      | $\pm 0.50$      | ±0.25             | LSB typ                             |

| No Missing Codes                                | 16                  | 16              | 16              | 12                | Bits Guaranteed                     |

| Offset Error                                    | 0.9 (0.5)           | (0.5)           | (0.5)           | (0.5)             | % FSR max (typ $@$ +25°C)           |

| Gain Error <sup>2</sup>                         | 2.75 (0.66)         | (0.66)          | (0.66)          | (0.66)            | % FSR max (typ $@$ +25°C)           |

| Gain Error <sup>3</sup>                         | 1.35 (0.7)          | (0.7)           | (0.7)           | (0.7)             | % FSR max (typ @ +25°C)             |

| TEMPERATURE DRIFT                               |                     |                 |                 |                   |                                     |

| Offset Error                                    | 2.5                 | 2.5             | 2.5             | 2.5               | ppm/°C typ                          |

| Gain Error <sup>2</sup>                         | 22                  | 22              | 22              | 22                | ppm/°C typ                          |

| Gain Error <sup>3</sup>                         | 7.0                 | 7.0             | 7.0             | 7.0               | ppm/°C typ                          |

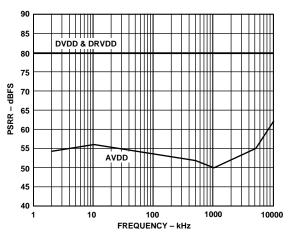

| POWER SUPPLY REJECTION                          |                     |                 |                 |                   |                                     |

| AVDD, DVDD, DRVDD (+5 V $\pm$ 0.25 V)           | 0.06                | 0.06            | 0.06            | 0.06              | % FSR max                           |

| ANALOG INPUT                                    |                     |                 |                 |                   |                                     |

| Input Span                                      |                     |                 |                 |                   |                                     |

| $V_{REF} = 1.0 V$                               | 1.6                 | 1.6             | 1.6             | 1.6               | V p-p Diff. max                     |

| $V_{REF} = 2.5 V$                               | 4.0                 | 4.0             | 4.0             | 4.0               | V p-p Diff. max                     |

| Input (VINA or VINB) Range                      | +0.5                | +0.5            | +0.5            | +0.5              | V min                               |

|                                                 | +AVDD - 0.5         | +AVDD - 0.5     | +AVDD - 0.5     | +AVDD - 0.5       | V max                               |

| Input Capacitance                               | 10.2                | 10.2            | 10.2            | 10.2              | pF typ                              |

| INTERNAL VOLTAGE REFERENCE                      |                     |                 |                 |                   |                                     |

| Output Voltage (1 V Mode)                       | 1                   | 1               | 1               | 1                 | V typ                               |

| Output Voltage Error (1 V Mode)                 | $\pm 14$            | $\pm 14$        | $\pm 14$        | $\pm 14$          | mV max                              |

| Output Voltage (2.5 V Mode)                     | 2.5                 | 2.5             | 2.5             | 2.5               | V typ                               |

| Output Voltage Error (2.5 V Mode)               | ±35                 | ±35             | ±35             | ±35               | mV max                              |

| Load Regulation <sup>4</sup>                    |                     |                 |                 |                   |                                     |

| 1 V REF                                         | 0.5                 | 0.5             | 0.5             | 0.5               | mV max                              |

| 2.5 V REF                                       | 2.0                 | 2.0             | 2.0             | 2.0               | mV max                              |

| REFERENCE INPUT RESISTANCE                      | 8                   | 8               | 8               | 8                 | kΩ                                  |

| Parameter—Decimation Factor (N) | AD9260 (8) | AD9260 (4) | AD9260 (2) | AD9260 (1) | Units   |

|---------------------------------|------------|------------|------------|------------|---------|

| POWER SUPPLIES                  |            |            |            |            |         |

| Supply Voltages                 |            |            |            |            |         |

| AVDD                            | +5         | +5         | +5         | +5         | V (±5%) |

| DVDD and DRVDD                  | +5.5       | +5.5       | +5.5       | +5.5       | V max   |

|                                 | +2.7       | +2.7       | +2.7       | +2.7       | V min   |

| Supply Current                  |            |            |            |            |         |

| IAVDD                           | 115        | 115        | 115        | 115        | mA typ  |

|                                 |            |            |            | 134        | mA max  |

| IDVDD                           | 12.5       | 10.3       | 6.5        | 2.4        | mA typ  |

|                                 |            |            |            | 3.5        | mA max  |

| IDRVDD                          | 0.450      | 0.850      | 1.7        | 2.6        | mA typ  |

| POWER CONSUMPTION               | 613        | 608        | 600        | 585        | mW typ  |

|                                 |            |            |            | 630        | mW max  |

NOTES

<sup>1</sup>VINA and VINB Connect to DUT CML.

<sup>2</sup>Including Internal 2.5 V reference.

<sup>3</sup>Excluding Internal 2.5 V reference.

<sup>4</sup>Load regulation with 1 mA load Current (in addition to that required by AD9260).

Specifications subject to change without notice.

# AC SPECIFICATIONS (AVDD = +5 V, DVDD = +3 V, DRVDD = +3 V, $f_{CLOCK}$ = 20 MSPS, $V_{REF}$ = +2.5 V, Input CML = 2.0 V $T_{MIN}$ to $T_{MAX}$ unless otherwise noted, $R_{BIAS}$ = 2 k $\Omega$ )

| Parameter—Decimation Factor (N)       | AD9260(8) | AD9260(4) | AD9260(2) | AD9260(1) | Units  |

|---------------------------------------|-----------|-----------|-----------|-----------|--------|

| DYNAMIC PERFORMANCE                   |           |           |           |           |        |

| INPUT TEST FREQUENCY: 100 kHz (typ)   |           |           |           |           |        |

| Signal-to-Noise Ratio (SNR)           |           |           |           |           |        |

| Input Amplitude = $-0.5$ dBFS         | 88.5      | 82        | 74        | 63        | dB typ |

| Input Amplitude = $-6.0$ dBFS         | 82.5      | 78        | 68        | 58        | dB typ |

| SNR and Distortion (SINAD)            |           |           |           |           |        |

| Input Amplitude = $-0.5$ dBFS         | 87.5      | 82        | 74        | 63        | dB typ |

| Input Amplitude = $-6.0$ dBFS         | 82        | 77.5      | 69        | 58        | dB typ |

| Total Harmonic Distortion (THD)       |           |           |           |           |        |

| Input Amplitude = $-0.5$ dBFS         | -96       | -96       | -97       | -98       | dB typ |

| Input Amplitude = $-6.0$ dBFS         | -93       | -98       | -96       | -98       | dB typ |

| Spurious Free Dynamic Range (SFDR)    |           |           |           |           |        |

| Input Amplitude = $-0.5$ dBFS         | 100       | 98        | 98        | 88        | dB typ |

| Input Amplitude = $-6.0$ dBFS         | 94        | 100       | 94        | 84        | dB typ |

| INPUT TEST FREQUENCY: 500 kHz         |           |           |           |           |        |

| Signal-to-Noise Ratio (SNR)           |           |           |           |           |        |

| Input Amplitude = $-0.5$ dBFS         | 86.5      | 82        | 74        | 63        | dB typ |

|                                       | 80.5      |           |           |           | dB min |

| Input Amplitude = $-6.0$ dBFS         | 82.5      | 77        | 68        | 58        | dB typ |

| SNR and Distortion (SINAD)            |           |           |           |           |        |

| Input Amplitude = $-0.5$ dBFS         | 86.0      | 81        | 74        | 63        | dB typ |

|                                       | 80.0      |           |           |           | dB min |

| Input Amplitude = $-6.0$ dBFS         | 82.0      | 77        | 68        | 58        | dB typ |

| Total Harmonic Distortion (THD)       |           |           |           |           |        |

| Input Amplitude = $-0.5$ dBFS         | -97.0     | -92       | -89       | -86       | dB typ |

|                                       | -90.0     |           |           |           | dB max |

| Input Amplitude = -6.0 dBFS           | -95.5     | -96       | -89       | -86       | dB typ |

| Spurious Free Dynamic Range (SFDR)    |           |           |           |           |        |

| Input Amplitude = $-0.5$ dBFS         | 99.0      | 92        | 91        | 88        | dB typ |

|                                       | 90.0      |           |           |           | dB max |

| Input Amplitude = $-6.0 \text{ dBFS}$ | 98        | 100       | 91        | 82        | dB typ |

# AD9260—SPECIFICATIONS AC SPECIFICATIONS (Continued)

| Parameter—Decimation Factor (N)                                                                                | AD9260 (8) | AD9260 (4) | AD9260 (2) | AD9260 (1) | Units      |

|----------------------------------------------------------------------------------------------------------------|------------|------------|------------|------------|------------|

| DYNAMIC PERFORMANCE (Continued)                                                                                |            |            |            |            |            |

| INPUT TEST FREQUENCY: 1.0 MHz (typ)                                                                            |            |            |            |            |            |

| Signal-to-Noise Ratio (SNR)                                                                                    |            |            |            |            |            |

| Input Amplitude = $-0.5$ dBFS                                                                                  | 85         | 82         | 74         | 63         | dB typ     |

| Input Amplitude = $-6.0$ dBFS                                                                                  | 80         | 76         | 68         | 58         | dB typ     |

| SNR and Distortion (SINAD)                                                                                     |            |            |            |            |            |

| Input Amplitude = $-0.5 \text{ dBFS}$                                                                          | 84.5       | 81         | 74         | 63         | dB typ     |

| Input Amplitude = $-6.0$ dBFS                                                                                  | 80         | 76         | 69         | 58         | dB typ     |

| Total Harmonic Distortion (THD)                                                                                |            |            |            |            |            |

| Input Amplitude = $-0.5$ dBFS                                                                                  | -102       | -96        | -82        | -79        | dB typ     |

| Input Amplitude = $-6.0$ dBFS                                                                                  | -96        | -94        | -84        | -77        | dB typ     |

| Spurious Free Dynamic Range (SFDR)                                                                             |            |            |            |            |            |

| Input Amplitude = $-0.5$ dBFS                                                                                  | 105        | 98         | 83         | 80         | dB typ     |

| Input Amplitude = $-6.0$ dBFS                                                                                  | 98         | 96         | 87         | 80         | dB typ     |

| INPUT TEST FREQUENCY: 2.0 MHz (typ)                                                                            |            |            |            |            |            |

| Signal-to-Noise Ratio (SNR)                                                                                    |            |            |            |            |            |

| Input Amplitude = $-0.5$ dBFS                                                                                  |            | 82         | 74         | 63         | dB typ     |

| Input Amplitude = $-6.0$ dBFS                                                                                  |            | 76         | 68         | 58         | dB typ     |

| SNR and Distortion (SINAD)                                                                                     |            |            |            |            |            |

| Input Amplitude = $-0.5 \text{ dBFS}$                                                                          |            | 81         | 73         | 62         | dB typ     |

| Input Amplitude = $-6.0$ dBFS                                                                                  |            | 76         | 69         | 58         | dB typ     |

| Total Harmonic Distortion (THD)                                                                                |            |            |            |            |            |

| Input Amplitude = $-0.5$ dBFS                                                                                  |            | -101       | -80        | -75        | dB typ     |

| Input Amplitude = $-6.0 \text{ dBFS}$                                                                          |            | -95        | -80        | -76        | dB typ     |

| Spurious Free Dynamic Range (SFDR)                                                                             |            |            |            |            |            |

| Input Amplitude = $-0.5$ dBFS                                                                                  |            | 104        | 80         | 78         | dB typ     |

| Input Amplitude = $-6.0$ dBFS                                                                                  |            | 100        | 83         | 79         | dB typ     |

| INPUT TEST FREQUENCY: 5.0 MHz (typ)                                                                            |            |            |            |            |            |

| Signal-to-Noise Ratio (SNR)                                                                                    |            |            |            |            |            |

| Input Amplitude = $-0.5$ dBFS                                                                                  |            |            |            | 59         | dB typ     |

| Input Amplitude = $-6.0$ dBFS                                                                                  |            |            |            | 57         | dB typ     |

| SNR and Distortion (SINAD)                                                                                     |            |            |            |            |            |

| Input Amplitude = $-0.5$ dBFS                                                                                  |            |            |            | 58         | dB typ     |

| Input Amplitude = $-6.0$ dBFS                                                                                  |            |            |            | 57         | dB typ     |

| Total Harmonic Distortion (THD)                                                                                |            |            |            |            |            |

| Input Amplitude = $-0.5$ dBFS                                                                                  |            |            |            | -58        | dB typ     |

| Input Amplitude = $-6.0$ dBFS                                                                                  |            |            |            | -67        | dB typ     |

| Spurious Free Dynamic Range (SFDR)                                                                             |            |            |            |            |            |

| Input Amplitude = $-0.5$ dBFS                                                                                  |            |            |            | 59         | dB typ     |

| Input Amplitude = $-6.0 \text{ dBFS}$                                                                          |            |            |            | 70         | dB typ     |

| INTERMODULATION DISTORTION                                                                                     |            |            |            |            |            |

| $f_{IN}1 = 475 \text{ kHz}, f_{IN}2 = 525 \text{ kHz}$                                                         | -93        | -91        | -91        | -83        | dBFS typ   |

| $f_{IN} = 475 \text{ kHz}, f_{IN} = 525 \text{ kHz}$<br>$f_{IN} = 950 \text{ kHz}, f_{IN} = 1.050 \text{ MHz}$ | -95        | -91        | -85        | -83        | dBFS typ   |

|                                                                                                                | -95        | -00        | -05        | -05        | ubi s typ  |

| DYNAMIC CHARACTERISTICS                                                                                        |            |            |            |            |            |

| Full Power Bandwidth                                                                                           | 75         | 75         | 75         | 75         | MHz typ    |

| Small Signal Bandwidth ( $A_{IN} = -20 \text{ dBFS}$ )                                                         | 75         | 75         | 75         | 75         | MHz typ    |

| Aperture Jitter                                                                                                | 2          | 2          | 2          | 2          | ps rms typ |

Specifications subject to change without notice.

# **DIGITAL FILTER CHARACTERISTICS**

| Parameter                                       | AD9260                                                             | Units    |  |

|-------------------------------------------------|--------------------------------------------------------------------|----------|--|

| 8× DECIMATION (N = 8)                           |                                                                    |          |  |

| Passband Ripple                                 | 0.00125                                                            | dB max   |  |

| Stopband Attenuation                            | 82.5                                                               | dB min   |  |

| Passband                                        | 0                                                                  | MHz min  |  |

|                                                 | $0.605 \times (f_{CLOCK}/20 \text{ MHz})$                          | MHz max  |  |

| Stopband                                        | $1.870 \times (f_{CLOCK}/20 \text{ MHz})$                          | MHz min  |  |

|                                                 | $18.130 \times (f_{\text{CLOCK}}/20 \text{ MHz})$                  | MHz max  |  |

| Passband/Transition Band Frequency              |                                                                    |          |  |

| (-0.1 dB Point)                                 | $0.807 \times (f_{CLOCK}/20 \text{ MHz})$                          | MHz max  |  |

| (-3.0  dB Point)                                | $1.136 \times (f_{CLOCK}/20 \text{ MHz})$                          | MHz max  |  |

| Absolute Group Delay <sup>1</sup>               | $8.20 \times (20 \text{ MHz/f}_{CLOCK})$                           | us max   |  |

| Group Delay Variation                           | 0                                                                  | μs max   |  |

| Settling Time (to $\pm 0.0007\%$ ) <sup>1</sup> | $13.35 \times (20 \text{ MHz/f}_{\text{CLOCK}})$                   | μs max   |  |

|                                                 | 15.55 × (20 WILL/ICLOCK)                                           | µo IIIax |  |

| $4 \times \text{DECIMATION} (N = 4)$            |                                                                    |          |  |

| Passband Ripple                                 | 0.001                                                              | dB max   |  |

| Stopband Attenuation                            | 82.5                                                               | dB min   |  |

| Passband                                        | 0                                                                  | MHz min  |  |

|                                                 | $1.24 \times (f_{CLOCK}/20 \text{ MHz})$                           | MHz max  |  |

| Stopband                                        | $3.75 \times (f_{CLOCK}/20 \text{ MHz})$                           | MHz min  |  |

| •                                               | $16.25 \times (f_{CLOCK}/20 \text{ MHz})$                          | MHz max  |  |

| Passband/Transition Band Frequency              |                                                                    |          |  |

| (-0.1 dB Point)                                 | $1.61 \times (f_{CLOCK}/20 \text{ MHz})$                           | MHz max  |  |

| (-3.0 dB Point)                                 | $2.272 \times (f_{CLOCK}/20 \text{ MHz})$                          | MHz max  |  |

| Absolute Group Delay <sup>1</sup>               | $2.90 \times (20 \text{ MHz/f}_{CLOCK})$                           | μs max   |  |

| Group Delay Variation                           | 0                                                                  | μs max   |  |

| Settling Time $(to \pm 0.0007\%)^1$             | $5.05 \times (20 \text{ MHz/f}_{\text{CLOCK}})$                    | μs max   |  |

|                                                 | Stos X (20 THILL CLOCK)                                            | po mun   |  |

| $2 \times \text{DECIMATION} (N = 2)$            |                                                                    |          |  |

| Passband Ripple                                 | 0.0005                                                             | dB max   |  |

| Stopband Attenuation                            | 85.5                                                               | dB min   |  |

| Passband                                        | 0                                                                  | MHz min  |  |

|                                                 | $2.491 \times (f_{CLOCK}/20 \text{ MHz})$                          | MHz max  |  |

| Stopband                                        | $7.519 \times (f_{CLOCK}/20 \text{ MHz})$                          | MHz min  |  |

|                                                 | $12.481 \times (f_{CLOCK}/20 \text{ MHz})$                         | MHz max  |  |

| Passband/Transition Band Frequency              |                                                                    |          |  |

| (-0.1 dB Point)                                 | $3.231 \times (f_{CLOCK}/20 \text{ MHz})$                          | MHz max  |  |

| (-3.0 dB Point)                                 | $4.535 \times (f_{CLOCK}/20 \text{ MHz})$                          | MHz max  |  |

| Absolute Group Delay <sup>1</sup>               | $0.80 \times (20 \text{ MHz/f}_{\text{cLOCK}})$                    | μs max   |  |

| Group Delay Variation                           | 0                                                                  | μs max   |  |

| Settling Time $(to \pm 0.0007\%)^1$             | $1.40 \times (20 \text{ MHz/f}_{\text{CLOCK}})$                    | μs max   |  |

|                                                 |                                                                    | po mus   |  |

| $1 \times \text{DECIMATION} (N = 1)$            |                                                                    |          |  |

| Propagation Delay: t <sub>PROP</sub>            | 13                                                                 | ns max   |  |

| Absolute Group Delay                            | $(225 \times (20 \text{ MHz/f}_{\text{CLOCK}})) + t_{\text{PROP}}$ | ns max   |  |

NOTES <sup>1</sup>To determine "overall" Absolute Group Delay and/or Settling Time inclusive of delay from the sigma-delta modulator, add Absolute Group Delay and/or Settling Time pertaining to specific decimation mode to the Absolute Group Delay specified in 1× decimation.

Specifications subject to change without notice.

# **AD9260–Digital Filter Characteristics**

Figure 1a. 8× FIR Filter Frequency Response

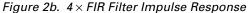

Figure 2a. 4 × FIR Filter Frequency Response

Figure 3a. 2 × FIR Filter Frequency Response

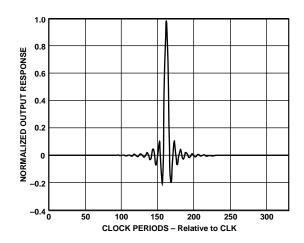

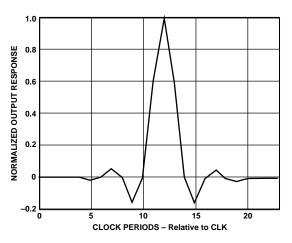

Figure 1b. 8 × FIR Filter Impulse Response

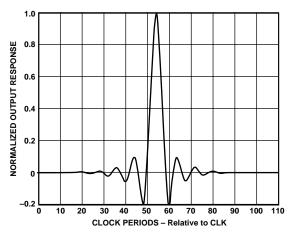

Figure 3b. 2 × FIR Filter Impulse Response

Table I. Integer Filter Coefficients for First Stage DecimationFilter (23-Tap Halfband FIR Filter)

Table III. Integer Filter Coefficients for Third Stage Decimation Filter (107-Tap Halfband FIR Filter)

| Lower<br>Coefficient | Upper<br>Coefficient | Integer<br>Value |

|----------------------|----------------------|------------------|

| H(1)                 | H(23)                | -1               |

| H(2)                 | H(22)                | 0                |

| H(3)                 | H(21)                | 13               |

| H(4)                 | H(20)                | 0                |

| H(5)                 | H(19)                | -66              |

| H(6)                 | H(18)                | 0                |

| H(7)                 | H(17)                | 224              |

| H(8)                 | H(16)                | 0                |

| H(9)                 | H(15)                | -642             |

| H(10)                | H(14)                | 0                |

| H(11)                | H(13)                | 2496             |

| H(12)                |                      | 4048             |

| Table II. Integer Filter Coefficients for Second Stage Decima- |

|----------------------------------------------------------------|

| tion Filter (43-Tap Halfband FIR Filter)                       |

| Lower<br>Coefficient | Upper<br>Coefficient | Integer<br>Value |  |

|----------------------|----------------------|------------------|--|

| H(1)                 | H(43)                | 3                |  |

| H(2)                 | H(42)                | 0                |  |

| H(3)                 | H(41)                | -12              |  |

| H(4)                 | H(40)                | 0                |  |

| H(5)                 | H(39)                | 35               |  |

| H(6)                 | H(38)                | 0                |  |

| H(7)                 | H(37)                | -83              |  |

| H(8)                 | H(36)                | 0                |  |

| H(9)                 | H(35)                | 172              |  |

| H(10)                | H(34)                | 0                |  |

| H(11)                | H(33)                | -324             |  |

| H(12)                | H(32)                | 0                |  |

| H(13)                | H(31)                | 572              |  |

| H(14)                | H(30)                | 0                |  |

| H(15)                | H(29)                | -976             |  |

| H(16)                | H(28)                | 0                |  |

| H(17)                | H(27)                | 1680             |  |

| H(18)                | H(26)                | 0                |  |

| H(19)                | H(25)                | -3204            |  |

| H(20)                | H(24)                | 0                |  |

| H(21)                | H(23)                | 10274            |  |

| H(22)                |                      | 16274            |  |

NOTE: The composite filter coefficients (i.e., impulse response) in the 4× decimation mode can be determined by convolving the first stage filter taps with a "zero stuffed" version of the second stage filter taps. Similarly, the composite filter coefficients in the 8× decimation mode can be determined by convolving the taps of the composite 4× decimation mode (as previously determined) with a "zero stuffed" version of the third stage filter taps.

| Lower<br>Coefficient | Upper<br>Coefficient | Integer<br>Value |

|----------------------|----------------------|------------------|

| H(1)                 | H(107)               | -1               |

| H(2)                 | H(106)               | 0                |

| H(3)                 | H(105)               | 2                |

| H(4)                 | H(104)               | 0                |

| H(5)                 | H(103)               | -2               |

| H(6)                 | H(102)               | 0                |

| H(7)                 | H(101)               | 3                |

| H(8)                 | H(100)               | 0                |

| H(9)                 | H(99)                | -3               |

| H(10)                | H(98)                | 0                |

| H(11)                | H(97)                | ů<br>1           |

| H(12)                | H(96)                | 0                |

| H(12)<br>H(13)       | H(95)                | 3                |

| H(14)                | H(93)<br>H(94)       | 0                |

| H(14)<br>H(15)       | H(93)                | -12              |

|                      |                      |                  |

| H(16)                | H(92)                | 0                |

| H(17)                | H(91)                | 27               |

| H(18)                | H(90)                | 0                |

| H(19)                | H(89)                | -50              |

| H(20)                | H(88)                | 0                |

| H(21)                | H(87)                | 85               |

| H(22)                | H(86)                | 0                |

| H(23)                | H(85)                | -135             |

| H(24)                | H(84)                | 0                |

| H(25)                | H(83)                | 204              |

| H(26)                | H(82)                | 0                |

| H(27)                | H(81)                | -297             |

| H(28)                | H(80)                | 0                |

| H(29)                | H(79)                | 420              |

| H(30)                | H(78)                | 0                |

| H(31)                | H(77)                | -579             |

| H(32)                | H(76)                | 0                |

| H(33)                | H(75)                | 784              |

| H(34)                | H(74)                | 0                |

| H(35)                | H(73)                | -1044            |

| H(36)                | H(72)                | 0                |

| H(37)                | H(71)                | 1376             |

| H(38)                | H(70)                | 0                |

| H(39)                | H(69)                | -1797            |

| H(40)                | H(68)                | 0                |

| H(41)                | H(67)                | 2344             |

| H(42)                | H(66)                | 0                |

| H(43)                | H(65)                | -3072            |

| H(44)                | H(64)                | 0                |

| H(45)                | H(63)                | 4089             |

| H(46)                | H(62)                | 0                |

| H(40)<br>H(47)       | H(62)<br>H(61)       | 0<br>-5624       |

| H(47)<br>H(48)       | H(01)<br>H(60)       | -5024            |

|                      |                      |                  |

| H(49)                | H(59)                | 8280             |

| H(50)                | H(58)                | 0                |

| H(51)                | H(57)                | -14268           |

| H(52)                | H(56)                | 0                |

| H(53)                | H(55)                | 43520            |

| H(54)                |                      | 68508            |

# AD9260-SPECIFICATIONS

### **DIGITAL SPECIFICATIONS** (AVDD = +5 V, DVDD = +5 V, $T_{MIN}$ to $T_{MAX}$ unless otherwise noted)

| Parameter                                                           | AD9260   | Units  |

|---------------------------------------------------------------------|----------|--------|

| CLOCK <sup>1</sup> AND LOGIC INPUTS                                 |          |        |

| High Level Input Voltage                                            |          |        |

| (DVDD = +5 V)                                                       | +3.5     | V min  |

| (DVDD = +3 V)                                                       | +2.1     | V max  |

| Low Level Input Voltage                                             |          |        |

| (DVDD = +5 V)                                                       | +1.0     | V min  |

| (DVDD = +3 V)                                                       | +0.9     | V max  |

| High Level Input Current ( $V_{IN} = DVDD$ )                        | $\pm 10$ | μA max |

| Low Level Input Current ( $V_{IN} = 0 V$ )                          | $\pm 10$ | μA max |

| Input Capacitance                                                   | 5        | pF typ |

| LOGIC OUTPUTS (with DRVDD = $5 \text{ V}$ )                         |          |        |

| High Level Output Voltage ( $I_{OH}$ = 50 µA)                       | +4.5     | V min  |

| High Level Output Voltage ( $I_{OH} = 0.5 \text{ mA}$ )             | +2.4     | V min  |

| Low Level Output Voltage <sup>2</sup> ( $I_{OL} = 0.3 \text{ mA}$ ) | +0.4     | V max  |

| Low Level Output Voltage ( $I_{OL}$ = 50 $\mu$ A)                   | +0.1     | V max  |

| Output Capacitance                                                  | 5        | pF typ |

| LOGIC OUTPUTS (with DRVDD = $3 \text{ V}$ )                         |          |        |

| High Level Output Voltage ( $I_{OH} = 50 \mu A$ )                   | +2.4     | V min  |

| Low Level Output Voltage ( $I_{OL} = 50 \mu A$ )                    | +0.7     | V max  |

NOTES

<sup>1</sup>Since CLK is referenced to AVDD, +5 V logic input levels only apply. <sup>2</sup>The AD9260 is not guaranteed to meet  $V_{OL}$  = 0.4 V max for standard TTL load of  $I_{OL}$  = 1.6 mA.

Specifications subject to change without notice.

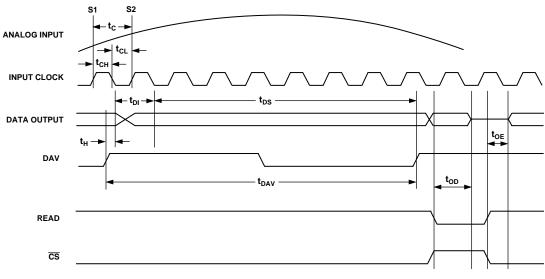

Figure 4. Timing Diagram

### **SWITCHING SPECIFICATIONS** (AVDD = +5 V, DVDD = +5 V, C<sub>L</sub> = 20 pF, T<sub>MIN</sub> to T<sub>MAX</sub> unless otherwise noted)

| Parameters                      | Symbol           | AD9260                        | Units  |

|---------------------------------|------------------|-------------------------------|--------|

| Clock Period                    | t <sub>C</sub>   | 50                            | ns min |

| Data Available (DAV) Period     | t <sub>DAV</sub> | $t_{\rm C} \times {\rm Mode}$ | ns min |

| Data Invalid                    | t <sub>DI</sub>  | 40% t <sub>DAV</sub>          | ns max |

| Data Setup Time                 | t <sub>DS</sub>  | $t_{DAV} - t_{H} - t_{DI}$    | ns min |

| Clock Pulsewidth High           | t <sub>CH</sub>  | 22.5                          | ns min |

| Clock Pulsewidth Low            | t <sub>CL</sub>  | 22.5                          | ns min |

| Data Hold Time                  | t <sub>H</sub>   | 3.5                           | ns min |

| Three-State Output Disable Time | t <sub>OD</sub>  | 8                             | ns typ |

| Three-State Output Enable Time  | t <sub>OE</sub>  | 45                            | ns typ |

Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS\*

|                                                 | ****    |      |             |          |

|-------------------------------------------------|---------|------|-------------|----------|

|                                                 | With    |      |             |          |

| D .                                             | Respect |      |             | <b>.</b> |

| Parameter                                       | to      | Min  | Max         | Units    |

| AVDD                                            | AVSS    | -0.3 | +6.5        | V        |

| DVDD                                            | DVSS    | -0.3 | +6.5        | V        |

| AVSS                                            | DVSS    | -0.3 | +0.3        | V        |

| AVDD                                            | DVDD    | -6.5 | +6.5        | V        |

| DRVDD                                           | DRVSS   | -0.3 | +6.5        | V        |

| DRVSS                                           | AVSS    | -0.3 | +0.3        | V        |

| REFCOM                                          | AVSS    | -0.3 | +0.3        | V        |

| CLK, MODE, READ,                                |         |      |             |          |

| $\overline{\text{CS}}, \overline{\text{RESET}}$ | DVSS    | -0.3 | DVDD + 0.3  | V        |

| Digital Outputs                                 | DRVSS   | -0.3 | DRVDD + 0.3 | V        |

| VINA, VINB,                                     |         |      |             |          |

| CML, BIAS                                       | AVSS    | -0.3 | AVDD + 0.3  | V        |

| VREF                                            | AVSS    | -0.3 | AVDD + 0.3  | V        |

| SENSE                                           | AVSS    | -0.3 | AVDD + 0.3  | V        |

| CAPB, CAPT                                      | AVSS    | -0.3 | AVDD + 0.3  | V        |

| Junction Temperature                            |         |      | +150        | °C       |

| Storage Temperature                             |         | -65  | +150        | °C       |

| Lead Temperature                                |         |      |             |          |

| (10 sec)                                        |         |      | +300        | °C       |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may effect device reliability.

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9260 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

#### **ORDERING GUIDE**

| Model                | Temperature    | Package                          | Package |

|----------------------|----------------|----------------------------------|---------|

|                      | Range          | Description                      | Option* |

| AD9260AS<br>AD9260EB | –40°C to +85°C | 44-Lead MQFP<br>Evaluation Board | S-44    |

\*S = Metric Quad Flatpack.

#### THERMAL CHARACTERISTICS

$\begin{array}{l} Thermal \ Resistance \\ 44-Lead \ MQFP \\ \theta_{JA} = 53.2^{\circ}C/W \\ \theta_{JC} = 19^{\circ}C/W \end{array}$

#### **DEFINITIONS OF SPECIFICATION** INTEGRAL NONLINEARITY (INL)

INL refers to the deviation of each individual code from a line drawn from "negative full scale" through "positive full scale." The point used as "negative full scale" occurs 1/2 LSB before the first code transition. "Positive full scale" is defined as a level 1 1/2 LSB beyond the last code transition. The deviation is measured from the middle of each particular code to the true straight line.

# DIFFERENTIAL NONLINEARITY (DNL, NO MISSING CODES)

An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. Guaranteed no missing codes to 14-bit resolution indicates that all 16384 codes, respectively, must be present over all operating ranges.

NOTE: Conventional INL and DNL measurements don't really apply to  $\Sigma\Delta$  converters: the DNL looks continually better if longer data records are taken. For the AD9260, INL and DNL numbers are given as representative.

#### ZERO ERROR

The major carry transition should occur for an analog value 1/2 LSB below VINA = VINB. Zero error is defined as the deviation of the actual transition from that point.

#### GAIN ERROR

The first code transition should occur at an analog value 1/2 LSB above negative full scale. The last transition should occur at an analog value 1 1/2 LSB below the nominal full scale. Gain error is the deviation of the actual difference between first and last code transitions and the ideal difference between first and last code transitions.

#### **TEMPERATURE DRIFT**

The temperature drift for zero error and gain error specifies the maximum change from the initial (+25°C) value to the value at  $T_{MIN}$  or  $T_{MAX}$ .

#### POWER SUPPLY REJECTION

The specification shows the maximum change in full scale from the value with the supply at the minimum limit to the value with the supply at its maximum limit.

#### APERTURE JITTER

Aperture jitter is the variation in aperture delay for successive samples and is manifested as noise on the input to the A/D.

# SIGNAL-TO-NOISE AND DISTORTION (S/N+D, SINAD) RATIO

S/N+D is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The value for S/N+D is expressed in decibels.

#### **EFFECTIVE NUMBER OF BITS (ENOB)**

For a sine wave, SINAD can be expressed in terms of the number of bits. Using the following formula,

$$N = (SINAD - 1.76)/6.02$$

it is possible to get a measure of performance expressed as N, the effective number of bits.

Thus, effective number of bits for a device for sine wave inputs at a given input frequency can be calculated directly from its measured SINAD.

#### TOTAL HARMONIC DISTORTION (THD)

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal and is expressed as a percentage or in decibels.

#### SIGNAL-TO-NOISE RATIO (SNR)

SNR is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, excluding the first six harmonics and dc. The value for SNR is expressed in decibels.

#### SPURIOUS FREE DYNAMIC RANGE (SFDR)

SFDR is the difference in dB between the rms amplitude of the input signal and the peak spurious signal.

#### TWO-TONE SFDR

The ratio of the rms value of either input tone to the rms value of the peak spurious component. The peak spurious component may or may not be an IMD product. May be reported in dBc (i.e., degrades as signal level is lowered), or in dBFS (always related back to converter full scale).

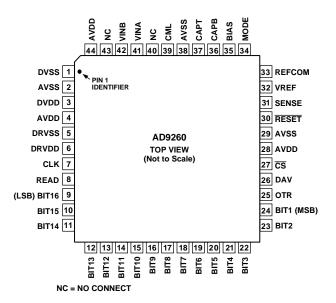

#### PIN CONFIGURATION

#### PIN FUNCTION DESCRIPTIONS

| Pin No.   | Name                     | Description                                            |  |

|-----------|--------------------------|--------------------------------------------------------|--|

| 1         | DVSS                     | Digital Ground.                                        |  |

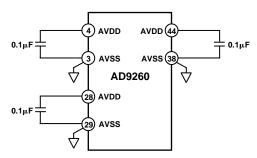

| 2, 29, 38 | AVSS                     | Analog Ground.                                         |  |

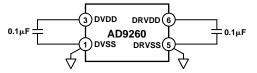

| 3         | DVDD                     | +3 V to +5 V Digital Supply.                           |  |

| 4, 28, 44 | AVDD                     | +5 V Analog Supply.                                    |  |

| 5         | DRVSS                    | Digital Output Driver Ground.                          |  |

| 6         | DRVDD                    | +3 V to +5 V Digital Output Driver Supply.             |  |

| 7         | CLK                      | Clock Input.                                           |  |

| 8         | READ                     | Part of DSP Interface—Pull Low to Disable Output Bits. |  |

| 9         | BIT16                    | Least Significant Data Bit (LSB).                      |  |

| 10-23     | BIT15-BIT2               | Data Output Bit.                                       |  |

| 24        | BIT1                     | Most Significant Data Bit (MSB).                       |  |

| 25        | OTR                      | Out of Range—Set When Converter or Filter Overflows.   |  |

| 26        | DAV                      | Data Available.                                        |  |

| 27        | $\overline{\mathrm{CS}}$ | Chip Select ( $\overline{CS}$ ): Active LOW.           |  |

| 30        | RESET                    | RESET: Active LOW.                                     |  |

| 31        | SENSE                    | Reference Amplifier SENSE: Selects REF Level.          |  |

| 32        | VREF                     | Input Span Select Reference I/O.                       |  |

| 33        | REFCOM                   | Reference Common.                                      |  |

| 34        | MODE                     | Mode Select—Selects Decimation Mode.                   |  |

| 35        | BIAS                     | Power Bias.                                            |  |

| 36        | CAPB                     | Noise Reduction Pin—Decouples Reference Level.         |  |

| 37        | CAPT                     | Noise Reduction Pin—Decouples Reference Level.         |  |

| 39        | CML                      | Common-Mode Level (AVDD/2.5).                          |  |

| 40, 43    | NC                       | No Connect (Ground for Shielding Purposes).            |  |

| 41        | VINA                     | Analog Input Pin (+).                                  |  |

| 42        | VINB                     | Analog Input Pin (–).                                  |  |

## **AD9260–Typical Performance Characteristics**

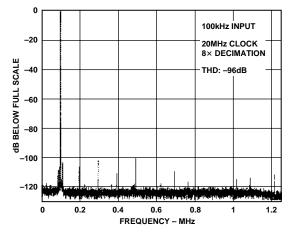

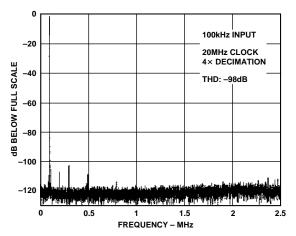

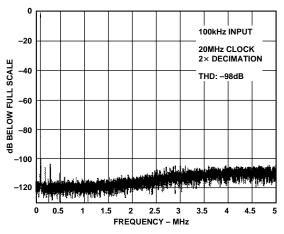

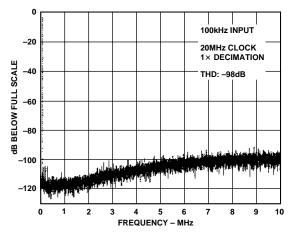

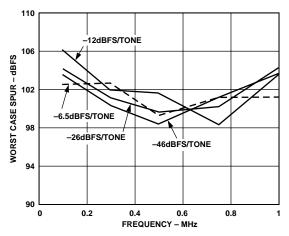

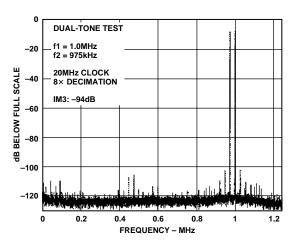

(AVDD = DVDD = DRVDD = +5.0 V, 4 V Input Span, Differential DC Coupled Input with CML = 2.0 V, f<sub>CLOCK</sub> = 20 MSPS, Full Bias)

Figure 5. Spectral Plot of the AD9260 at 100 kHz Input, 20 MHz Clock, 8× OSR (2.5 MHz Output Data Rate)

Figure 6. Spectral Plot of the AD9260 at 100 kHz Input, 20 MHz Clock,  $4 \times OSR$  (5 MHz Output Data Rate)

Figure 7. Spectral Plot of the AD9260 at 100 kHz Input, 20 MHz Clock, 2× OSR (10 MHz Output Data Rate)

Figure 8. Spectral Plot of the AD9260 at 100 kHz Input, 20 MHz Clock, Undecimated (20 MHz Output Data Rate)

Figure 9. Dual Tone SFDR vs. Input Frequency ( $F_1 = F_2$ , ( $F_1 - F_2$ , Span = 10% Center Frequency, Mode = 8×)

Figure 10. Two-Tone Spectral Performance of the AD9260 Given Inputs at 9 75 kHz and 1.0 MHz, 20 MHz Clock, 8× Decimation

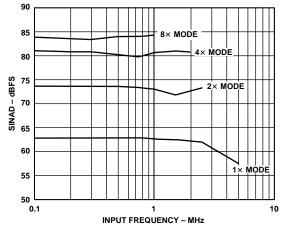

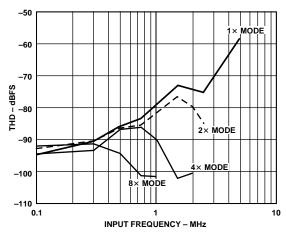

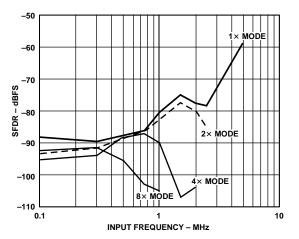

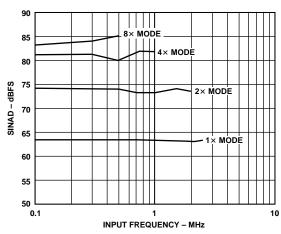

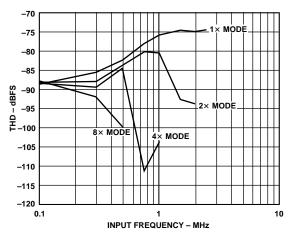

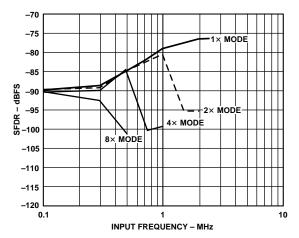

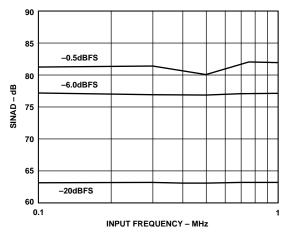

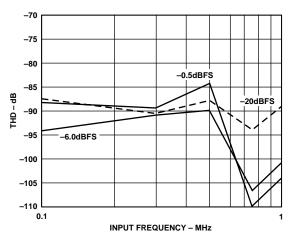

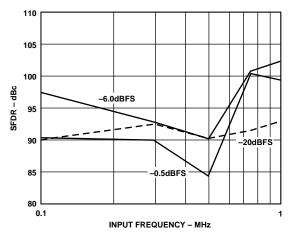

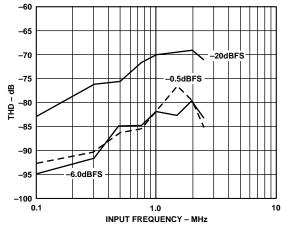

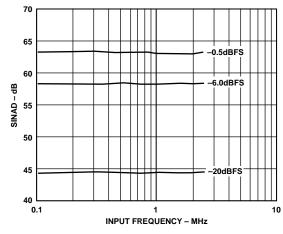

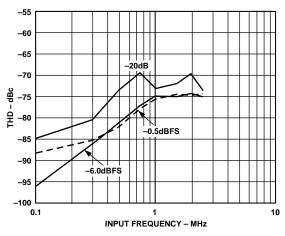

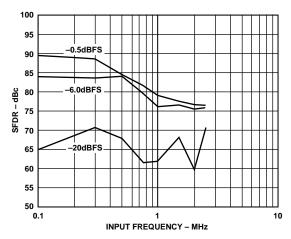

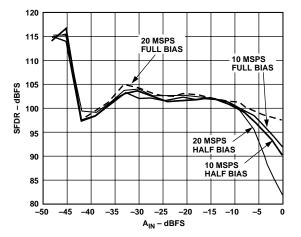

### **Typical AC Characterization Curves vs. Decimation Mode**

(AVDD = DVDD = DRVDD = +5 V, 4 V Input Span, Differential DC Coupled Input with CML = 2 V, A<sub>IN</sub> = 0.5 dBFS Full Bias)

Figure 11. SINAD vs. Input Frequency  $(f_{CLOCK} = 20 \text{ MSPS})^1$

Figure 12. THD vs. Input Frequency (f<sub>CLOCK</sub> = 20 MSPS)

Figure 13. SFDR vs. Input Frequency ( $f_{CLOCK} = 20$  MSPS)

$^{1}8\times$  SINAD performance limited by noise contribution of input differential op amp driver.

Figure 14. SINAD vs. Input Frequency  $(f_{CLOCK} = 10 \text{ MSPS})^1$

Figure 15. THD vs. Input Frequency (f<sub>CLOCK</sub> = 10 MSPS)

Figure 16. SFDR vs. Input Frequency (f<sub>CLOCK</sub> = 10 MSPS)

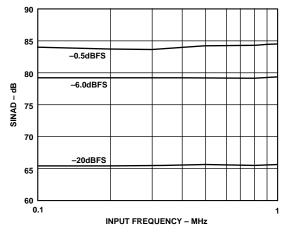

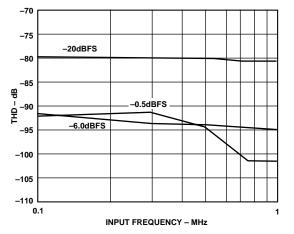

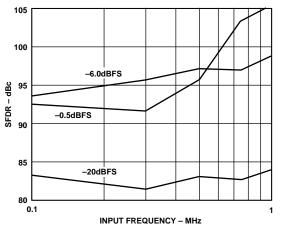

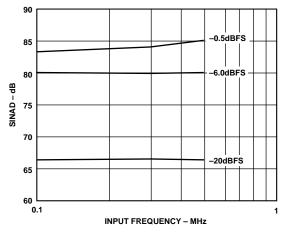

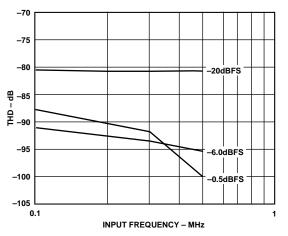

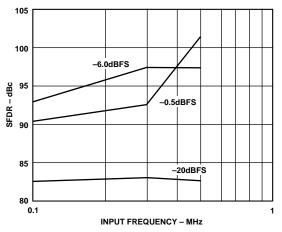

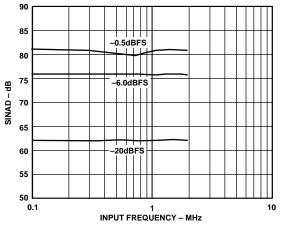

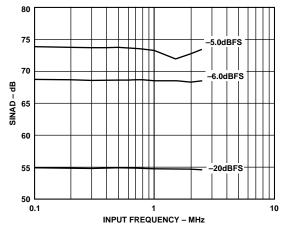

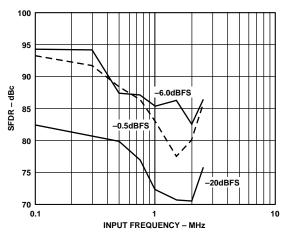

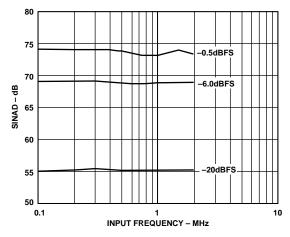

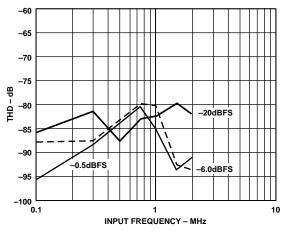

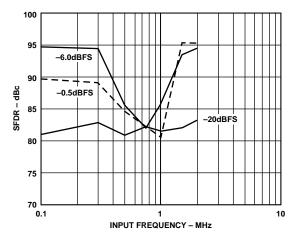

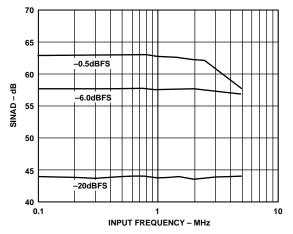

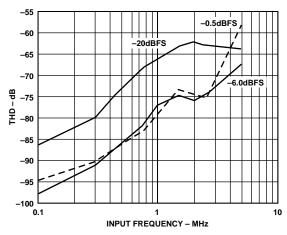

### Typical AC Characterization Curves for $8 \times$ Mode

(AVDD = DVDD = DRVDD = +5 V, 4 V Input Span, Differential DC Coupled Input with CML = 2 V, Full Bias)

Figure 17. SINAD vs. Input Frequency (f<sub>CLOCK</sub> = 20 MSPS)<sup>1</sup>

Figure 18. THD vs. Input Frequency (f<sub>CLOCK</sub> = 20 MSPS)

Figure 19. SFDR vs. Input Frequency (f<sub>CLOCK</sub> = 20 MSPS)

Figure 20. SINAD vs. Input Frequency  $(f_{CLOCK} = 10 \text{ MSPS})^{1}$

Figure 21. THD vs. Input Frequency (f<sub>CLOCK</sub> = 10 MSPS)

Figure 22. SFDR vs. Input Frequency (f<sub>CLOCK</sub> = 10 MSPS)

<sup>1</sup>SINAD performance limited by noise contribution of input differential op amp driver.

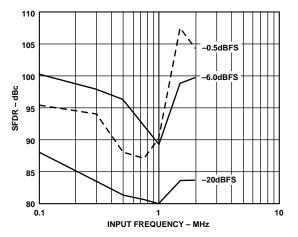

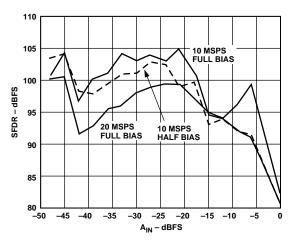

## Typical AC Characterization Curves for $4 \times$ Mode

(AVDD = DVDD = DRVDD = +5 V, 4 V Input Span, Differential DC Coupled Input with CML = 2 V, Full Bias)

Figure 23. SINAD vs. Input Frequency (f<sub>CLOCK</sub> = 20 MSPS)

Figure 24. THD vs. Input Frequency ( $f_{CLOCK} = 20$  MSPS)

Figure 25. SFDR vs. Input Frequency (f<sub>CLOCK</sub> = 20 MSPS)

Figure 26. SINAD vs. Input Frequency ( $f_{CLOCK} = 10 \text{ MSPS}$ )

Figure 27. THD vs. Input Frequency ( $f_{CLOCK} = 10 \text{ MSPS}$ )

Figure 28. SFDR vs. Input Frequency (f<sub>CLOCK</sub> = 10 MSPS)

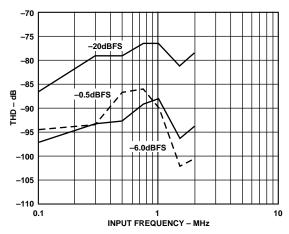

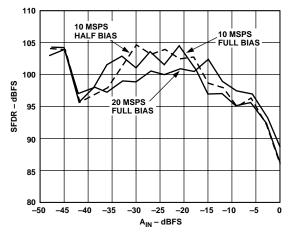

# Typical AC Characterization Curves for $2 \times$ Mode

(AVDD = DVDD = DRVDD = +5 V, 4 V Input Span, Differential DC Coupled Input with CML = 2 V, Full Bias)

Figure 29. SINAD vs. Input Frequency (f<sub>CLOCK</sub> = 20 MSPS)

Figure 30. THD vs. Input Frequency (f<sub>CLOCK</sub> = 20 MSPS)

Figure 31. SFDR vs. Input Frequency (f<sub>CLOCK</sub> = 20 MSPS)

Figure 32. SINAD vs. Input Frequency ( $f_{CLOCK} = 10 \text{ MSPS}$ )

Figure 33. THD vs. Input Frequency ( $f_{CLOCK} = 10 \text{ MSPS}$ )

Figure 34. SFDR vs. Input Frequency (f<sub>CLOCK</sub> = 10 MSPS)

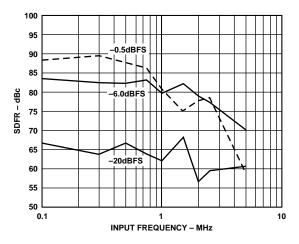

### Typical AC Characterization Curves for $1 \times$ Mode

(AVDD = DVDD = DRVDD = +5 V, 4 V Input Span, Differential DC Coupled Input with CML = 2 V, Full Bias)

Figure 35. SINAD vs. Input Frequency (f<sub>CLOCK</sub> = 20 MSPS)

Figure 36. THD vs. Input Frequency ( $f_{CLOCK} = 20$  MSPS)

Figure 37. SFDR vs. Input Frequency (f<sub>CLOCK</sub> = 20 MSPS)

Figure 38. SINAD vs. Input Frequency ( $f_{CLOCK} = 10 \text{ MSPS}$ )

Figure 39. THD vs. Input Frequency (f<sub>CLOCK</sub> = 10 MSPS)

Figure 40. SFDR vs. Input Frequency (f<sub>CLOCK</sub> = 10 MSPS)

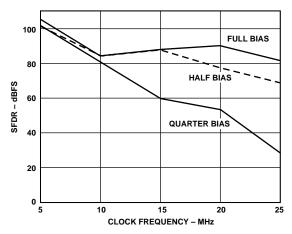

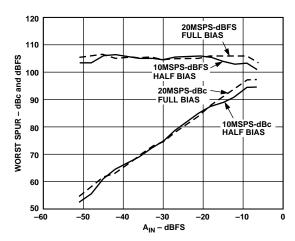

### **Typical AC Characterization Curves**

(AVDD = DVDD = DRVDD = +5 V, 4 V Input Span,  $A_{IN} = -0.5 dBFS$ , Differential DC Coupled Input with CML = 2 V)

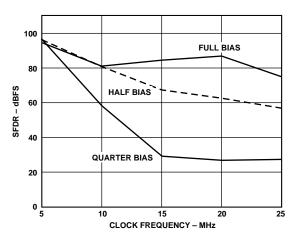

Figure 41. SFDR vs. Clock Rate ( $f_{IN}$  = 100 kHz in 8× Mode)

Figure 42. SFDR vs. Clock Rate ( $f_{IN}$  = 500 kHz in 4× Mode)

Figure 43. SFDR vs. Clock Rate ( $f_{IN}$  = 1.0 MHz in 2× Mode)

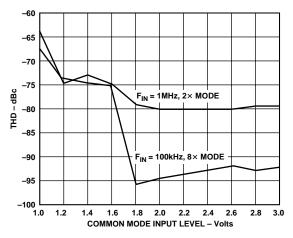

Figure 44. THD vs. Common-Mode Input Level (CML)

Figure 45. CMR vs. Input Frequency ( $V_{CML} = 2 V p - p$ , 1× Mode)

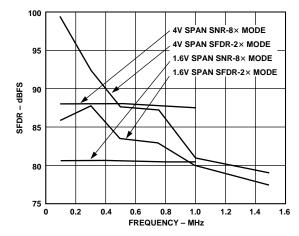

Figure 46. 4 V vs. 1.6 V Span SNR/SFDR (f<sub>CLOCK</sub> = 20 MSPS)

### **Additional AC Characterization Curves**

(AVDD = DVDD = DRVDD = +5 V, 4 V Input Span, A<sub>IN</sub> = -0.5 dBFS, Differential DC Coupled Input with CML = 2 V, Full Bias, unless otherwise noted)

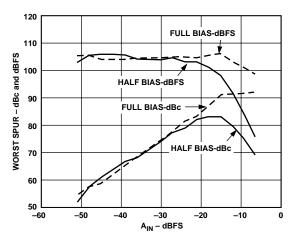

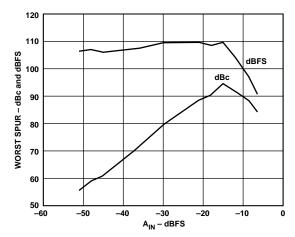

Figure 47. Single-Tone SFDR vs. Amplitude (f<sub>IN</sub> =100 kHz, 8× Mode)

Figure 48. Single-Tone SFDR vs. Amplitude ( $f_{IN}$  =1.0 MHz, 2× Mode)

Figure 49. Single-Tone SFDR vs. Amplitude ( $f_{IN} = 500 \text{ kHz}$ , 2× Mode)

Figure 50. Two-Tone SFDR ( $F_1 = 475 \text{ kHz}$ ,  $F_2 = 525 \text{ MHz}$ ,  $8 \times \text{ Mode}$ )

Figure 51. Two-Tone SFDR ( $F_1 = 0.95 \text{ kHz}$ ,  $F_2 = 1.05 \text{ MHz}$ ,  $8 \times \text{Mode 20 MSPS}$ )

Figure 52. Two-Tone SFDR ( $F_1 = 1.9 \text{ MHz}$ ,  $F_2 = 2.1 \text{ MHz}$ ,  $4 \times \text{ Mode 20 MSPS}$ )

Figure 53. Simplified Block Diagram

#### THEORY OF OPERATION

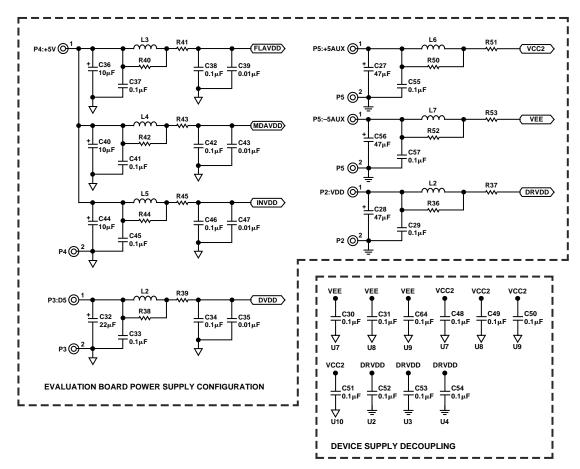

The AD9260 utilizes a new analog-to-digital converter architecture to combine sigma-delta techniques with a high speed, pipelined A/D converter. This topology allows the AD9260 to offer the high dynamic range associated with sigma-delta converters while maintaining very wide input signal bandwidth (1.25 MHz) at a very modest 8× oversampling ratio. Figure 53 provides a block diagram of the AD9260. The differential analog input is fed into a second order, multibit sigma-delta modulator. This modulator features a 5-bit flash quantizer and 5-bit feedback. In addition, a 12-bit pipelined A/D quantizes the input to the 5-bit flash to greater accuracy. A special digital modulation loop combines the output of the 12-bit pipelined A/D with the delayed output of the 5-bit flash to produce the equivalent response of a second order loop with a 12-bit quantizer and 12-bit feedback. The combination of a second order loop and multibit feedback provides inherent stability: the AD9260 is not prone to idle tones or full-scale idiosyncracies sometimes associated with higher order single bit sigmadelta modulators.

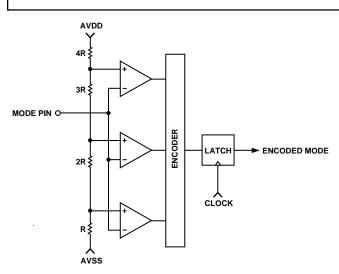

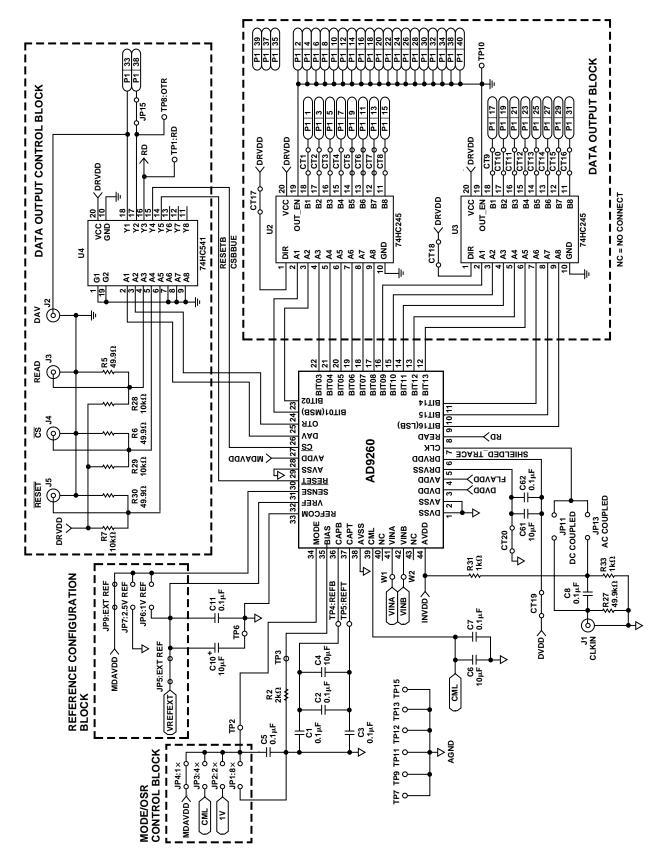

The output of this 12-bit modulator is fed into the digital decimation filter. The voltage level on the MODE pin establishes the configuration for the digital filter. The user may bring the data out undecimated (at the clock rate), or at a decimation factor of  $2\times$ ,  $4\times$ , or a full  $8\times$ . The spectra for these four cases are shown in Figures 5, 6, 7 and 8, all for a 100 kHz full-scale input and 20 MHz clock. The spectra of the undecimated output clearly shows the second order shaping characteristic of the quantization noise as it rises at frequencies above 1.25 MHz.

The on-chip decimation filter provides excellent stopband rejection to suppress any stray input signal between 1.25 MHz and 18.75 MHz, substantially easing the requirements on any antialiasing filter for the analog input path. The decimation filters are integrated with symmetric FIR filter structures, providing a linear phase response and excellent passband flatness. The digital output driver register of the AD9260 features both READ and CHIP SELECT pins to allow easy interfacing. The digital supply of the AD9260 is designed to operate over a 2.7 V to 5.25 V supply range, though 3 V supplies are recommended to minimize digital noise on the board. A DATA AVAILABLE pin allows the user to easily synchronize to the converter's decimated output data rate. OUT-OF-RANGE (OTR) indication is given for an overflow in the pipelined A/D converter or digital filters. A RESETB function is provided to synchronize the converter's decimated data and clear any overflow condition in the analog integrators.

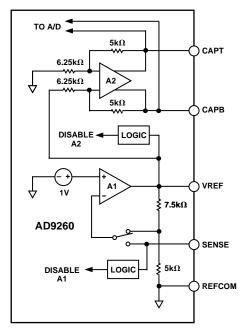

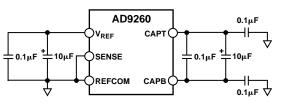

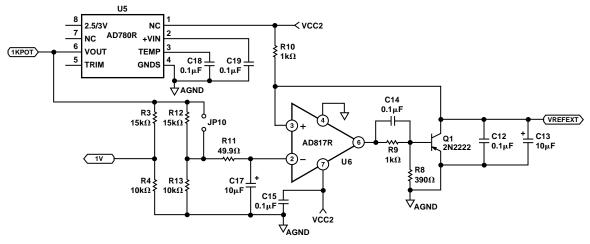

An on-chip reference and reference buffer are included on the AD9260. The reference can be configured in either a 2.5 V mode (providing a 4 V pk-pk differential input full scale), a 1 V mode (providing a 1.6 V pk-pk differential input full scale), or programmed with an external resistor divider to provide any voltage level between 1 V and 2.5 V. *However, optimum noise and distortion performance for the AD9260 can only be achieved with a* 2.5 V reference as shown in Figure 46.

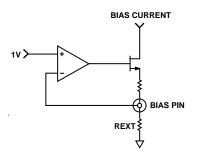

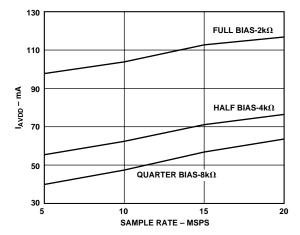

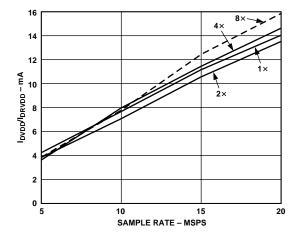

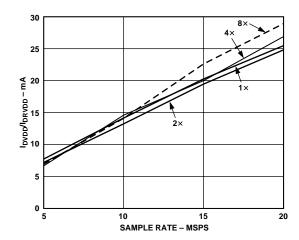

For users wishing to operate the part at reduced clock frequencies, the bias current of the AD9260 is designed to be scalable. This scaling is accomplished through use of the proper external resistor tied to the BIAS pin: the power can be reduced roughly proportionately to clock frequency by as much as 75% (for clock rates of 5 MHz). Refer to Figures 41–43 and 47–51 for characterization curves showing performance tradeoffs.

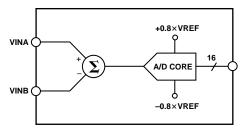

#### ANALOG INPUT AND REFERENCE OVERVIEW

Figure 54, a simplified model of the AD9260, highlights the relationship between the analog inputs, VINA, VINB and the reference voltage VREF. Like the voltage applied to the top of the resistor ladder in a flash A/D converter, the value VREF defines the maximum input voltage to the A/D converter. An internal reference buffer in the AD9260 scales the reference voltage VREF before it is applied internally to the AD9260

A/D core. The scale factor of this reference buffer is 0.8. Consequently, the maximum input voltage to the A/D core is  $+0.8 \times$  VREF. The minimum input voltage to the A/D core is automatically defined to be  $-0.8 \times$  VREF. With this scale factor, the maximum differential input span of 4 V p-p is obtained with a VREF voltage of 2.5 V. A smaller differential input span may be obtained by using a VREF voltage of less than 2.5 V at the expense of ac performance (refer to Figure 46).

Figure 54. Simplified Input Model

#### **INPUT SPAN**

The AD9260 is implemented with a differential input structure. This structure allows the common-mode level (average voltage of the two input pins) of the input signal to be varied independently of the input span of the converter over a wide range, as shown in Figure 44. Specifically, the input to the A/D core is the difference of the voltages applied at the VINA and VINB input pins. Therefore, the equation,

$$VCORE = VINA - VINB \tag{1}$$

defines the output of the differential input stage and provides the input to the A/D core.

The voltage, VCORE, must satisfy the condition,

$$-0.8 \times VREF \le VCORE \le +0.8 \times VREF$$

(2)

where VREF is the voltage at the VREF pin.

#### INPUT COMPLIANCE RANGE

In addition to the limitations on the differential span of the input signal indicated in Equation 2, an additional limitation is placed on the inputs by the analog input structure of the AD9260. The analog input structure bounds the valid operating range for VINA and VINB. The condition,

$$AVSS + 0.5 V < VINA < AVDD - 0.5 V$$

$$AVSS + 0.5 V < VINB < AVDD + 0.5 V$$

(3)

where AVSS is nominally 0 V and AVDD is nominally +5 V, defines this requirement. Thus the valid inputs for VINA and VINB are any combination that satisfies both Equations 2 and 3. Note, the clock clamping method used in the differential driver circuit shown in Figure 57 is sufficient for protecting the AD9260 in an undervoltage condition.

For additional information showing the relationships between VINA, VINB, VREF and the digital output of the AD9260, see Table V.

Refer to Table IV for a summary of the various analog input and reference configurations.

#### ANALOG INPUT OPERATION

The analog input structure of the AD9260 is optimized to meet the performance requirements for some of the most demanding communication and data acquisition applications. This input structure is composed of a switched-capacitor network that samples the input signal applied to pins VINA and VINB on every rising edge of the CLK pin. The input switched capacitors are charged to the input voltage during each period of CLK. The resulting charge, q, on these capacitors is equal to  $C \times V_{IN}$ , where C is the input capacitor. The change in charge on these capacitors, delta q, as the capacitors are charged from a previous sample of the input signal to the next sample, is approximated in the following equation,

$$delta \ q \sim \mathbf{C} \times delta V_N = \mathbf{C} \times (V_N - \mathbf{V}_{N-2}) \tag{4}$$

where  $V_N$  represents the present sample of the input signal and  $V_{N-2}$  represents the sample taken two clock cycles earlier. The average current flow into the input (provided from an external source) is given in the following equation,

$$I = delta \ q/T \sim C \times (V_N - V_{N-2}) \times f_{CLOCK}$$

(5)

where *T* represents the period of CLK and  $f_{CLOCK}$  represents the frequency of CLK. Equations 4 and 5 provide simplifying approximations of the operation of the analog input structure of the AD9260. A more exact, detailed description and analysis of the input operation is provided below.

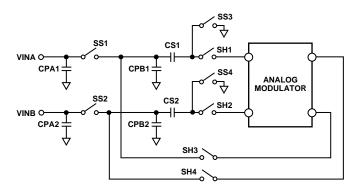

#### Figure 55. Detailed Analog Input Structure

Figure 55 illustrates the analog input structure of the AD9260. For the moment, ignore the presence of the parasitic capacitors CPA and CPB. The effects of these parasitic capacitors will be discussed near the end of this section. The switched capacitors, CS1 and CS2, sample the input voltages applied on pins VINA and VINB. These capacitors are connected to input pins VINA and VINB when CLK is low. When CLK rises, a sample of the input signal is taken on capacitors CS1 and CS2. When CLK is high, capacitors CS1 and CS2 are connected to the Analog Modulator. The modulator precharges capacitors CS1 and CS2 to minimize the amount of charge required from any circuit used in combination with the AD9260 to drive input pins VINA and VINB. This reduces the input drive requirements of the analog circuitry driving pins VINA and VINB. The Analog Modulator precharges the voltages across capacitors CS1 and CS2, approximately equal to a delayed version of the input signal. When capacitors CS1 and CS2 are connected to input pins VINA and VINB, the differential charge, Q(n), on these capacitors is given in the following equation,

$$Q(n) = q1 - q2 = CS \times VCORE$$

(6)

where q1 and q2 are the individual charges stored on capacitors CS1 and CS2 respectively, and CS is the capacitance value of CS1 and CS2. When capacitors CS1 and CS2 are connected to the Analog Modulator during the preceding "precharge" clock phase, the capacitors are precharged equal to an approximation of a previous sample of the input signal. Consequently the differential charge on these capacitors while CLK is high is given in the following equation,

$$Q(n-1) = CS \times VCORE(delay) + CS \times Vdelta$$

(7)

where VCORE(delay) is the value of VCORE sampled during a previous period of CLK, and *Vdelta* is the sigma-delta error voltage left on the capacitors. Vdelta is a natural artifact of the sigma-delta feedback techniques utilized in the Analog Modulator of the AD9260. It is a small random voltage term that changes every clock period and varies from 0 to  $\pm 0.05 \times$  VREF.

The analog circuitry used to drive the input pins of the AD9260 must respond to the charge glitch that occurs when capacitors CS1 and CS2 are connected to input pins VINA and VINB. This circuitry must provide additional charge, qdelta, to capacitors CS1 and CS2, which is the difference between the precharged value, Q(n-1), and the new value, Q(n), as given in the following equation,

$$Qdelta = Q(n) - Q(n-1)$$

(8)

$$Qdelta = CS \times [VCORE-VCORE(delay) + Vdelta]$$

(9)

#### DRIVING THE INPUT

#### **Transient Response**

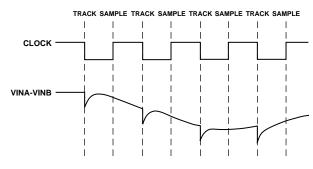

The charge glitch occurs once at the beginning of every period of the input CLK (falling edge), and the sample is taken on capacitors CS1 and CS2 exactly one-half period later (rising edge). Figure 56 presents a typical input waveform applied to input Pins VINA and VINB of the AD9260.

Figure 56. Typical Input Waveform

Figure 56 illustrates the effect of the charge glitch when a source with nonzero output impedance is used to drive the input pins. This source must be capable of settling from the charge glitch in one-half period of the CLK. Unfortunately, the MOS switches used in any CMOS-switched capacitor circuit (including those in the AD9260) include nonlinear parasitic junction capacitances connected to their terminals. Figure 55 also illustrates the parasitic capacitances, Cpa1, Cpb1, Cpa2 and Cpb2, associated with the input switches.

Parasitic capacitor Cpa1 and Cpa2 are always connected to Pins VINA and VINB and therefore do not contribute to the glitch energy. Parasitic capacitors Cpb1 and Cpb2, on the other hand,

cause a charge glitch that adds to that of input capacitors CS1 and CS2 when they are connected to input Pins VINA and VINB. The nonlinear junction capacitance of Cpb1 and Cpb2 cause charge glitch energy that is nonlinearily related to the input signal. Therefore, linear settling is difficult to achieve unless the input source completely settles during one-half period of CLK. A portion of the glitch impulse energy "kicked" back at the source is not linearly related to the input signal. Therefore, the best way to ensure that the input signal settles linearly is to use wide bandwidth circuitry, which settles as completely as possible from the glitch during one-half period of the CLK.

The AD9260 utilizes a proprietary clock-boosted boot-strapping technique to reduce the nonlinear parasitic capacitances of the internal CMOS switches. This technique improves the linearity of the input switches and reduces the nonlinear parasitic capacitance. Thus, this technique reduces the nonlinear glitch energy. The capacitance values for the input capacitors and parasitic capacitors for the input structure of the AD9260, as illustrated in Figure 55, are listed as follows.

CS = 3.2 pF, Cpa = 6 pF, Cpb = 1 pF (where CS is the capacitance value of capacitors CS1 and CS2, Cpa is the value of capacitors Cpa1 and Cpa2, and Cpb is the value of capacitors Cpb1 and Cpb2). The total capacitance at each input pin is  $C_{IN} = CS + Cpa + Cpb = 10.2 \text{ pF}.$

#### **Input Driver Considerations**

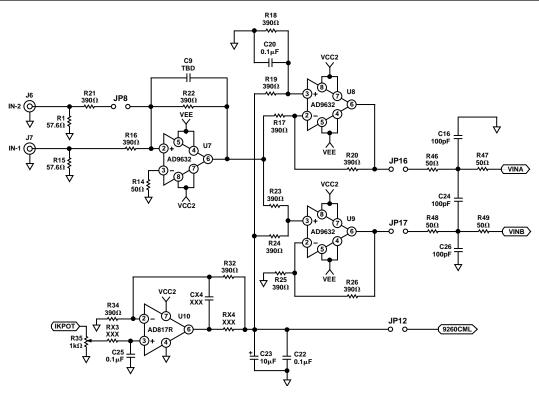

The optimum noise and distortion performance of the AD9260 can ONLY be achieved when the AD9260 is driven differentially with a 4 V input span. Since not all applications have a signal preconditioned for differential operation, there is often a need to perform a single-ended-to-differential conversion. In the case of the AD9260, a single-ended-to-differential conversion is best realized using a differential op amp driver. Although a transformer will perform a similar function for ac signals, its usefulness is precluded by its inability to directly drive the AD9260 and thus the additional requirement of an active low noise, low distortion buffer stage.

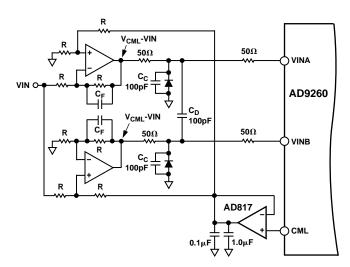

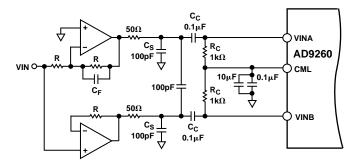

#### Single-Ended to Differential Op Amp Driver

There are two particular single-ended-to-differential op amp driver circuits useful for driving the AD9260. The first driver circuit shown in Figure 57 is optimized for dc coupling applications requiring optimum distortion performance. This differential op amp driver circuit is configured to convert and level shift a 2 V p-p single-ended, ground referenced signal to a 4 V p-p differential signal centered at the common-mode level of the AD9260. The circuit is based on two op amps which are configured as matched unity gain difference amplifiers. The singleended input signal is applied to opposing inputs of the difference amplifiers, thus providing differential outputs. The commonmode offset voltage is applied to the noninverting resistor leg of each difference amplifier providing the required offset voltage. This offset voltage is derived from the common-mode level (CML) pin of the AD9260 via a low output impedance buffer amplifier capable of driving a 1 µF capacitive load. The common-mode offset can be varied over a 1.8 V to 2.5 V span without any serious degradation in distortion performance as shown in Figure 44, thus providing some flexibility in improving output compression distortion from some  $\pm 5$  op amps with limited positive voltage swing.

Figure 57. DC-Coupled Differential Driver with Level-Shifting

To protect the AD9260 from an undervoltage fault condition from op amps specified for  $\pm 5$  V operation, two 50  $\Omega$  series resistors and a diode to AGND are inserted between each op amp output and the AD9260 inputs. The AD9260 will inherently be protected against any overvoltage condition if the op amps share the same positive power supply (i.e., AVDD) as the AD9260. Note, the gain accuracy and common-mode rejection of each difference amplifier in this driver circuit can be enhanced by using a matched thin-film resistor network (i.e., Ohmtek ORNA5000F) for the op amps. Resistor values should be 500  $\Omega$  or less to maintain the lowest possible noise. Recall, the AD9260's small signal bandwidth is 75 MHz, hence any noise falling within the baseband bandwidth of the AD9260 defined by its sample and decimation rate, as well as "images" of its baseband response occurring at multiples of the sample rate, will degrade its overall noise performance.

The noise performance of each unity gain differential driver circuit is limited by its inherent noise gain of two. For unity gain op amps ONLY, the noise gain can be reduced from two to one beyond the input signals passband by adding a shunt capacitor,  $C_F$ , across each op amp's feedback resistor. This will essentially establish a low-pass filter which reduces the noise gain to one beyond the filter's  $f_{-3 \text{ dB}}$  while simultaneously bandlimiting the input signal to  $f_{-3 \text{ dB}}$ . Note, the pole established by this filter can also be used as the real pole of an antialiasing filter. Since the noise contribution of two op amps from the same product family are typically equal but uncorrelated, the total output-referred noise of each op amp will add root-sum square leading to a

further 3 dB degradation in the circuit's noise performance. Further out-of-band noise reduction can be realized with the addition of single-ended and differential capacitors,  $C_S$  and  $C_D$ .