# 2 Pair/1 Pair ETSI Compatible **HDSL Analog Front End**

AD6472

**FEATURES**

Integrated Front End for Single Pair or Two Pair HDSL **Systems**

**Meets ETSI Specifications** Supports 1168 Kbps and 2.32 Mbps **Transmit and Receive Signal Path Functions** Receive Hybrid Amplifier, PGA and ADC

Transmit DAC, Filter and Differential Outputs

**Programmable Filters**

**Control and Ancillary Functions**

**Timing Recovery DAC**

Normal Loopback and Low Power Modes Simple Interface-to-Digital Transceivers

Single 5 V Power Supply

Power Consumption: 320 mW—(Excluding Driver)

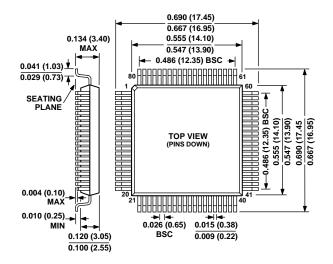

Package: 80-Lead MQFP

Operating Temperature: -40°C to +85°C

# **GENERAL DESCRIPTION**

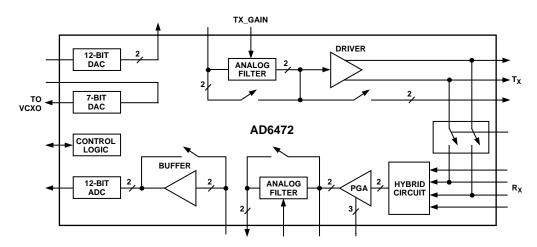

The AD6472 is a single chip analog front end for two pair or single pair HDSL applications that use 1168 Kbps or 2.32 Mbps data rates.

The AD6472 integrates all the transmit and receive functional blocks together with the timing recovery DAC.

The digital interface is designed to support industry standard digital transceivers.

While providing the full analog front end for ETSI standards (two pair or single pair HDSL applications) the AD6472 supports other applications because the architecture allows for bypassing the functional blocks.

The normal, low power, and loopback modes and the digital interface combine to make the AD6472 simple to integrate into systems.

## FUNCTIONAL BLOCK DIAGRAM

# $AD6472 - SPECIFICATIONS \ \, (T_A = T_{MIN} \ \, to \ \, T_{MAX} \ \, unless \ \, otherwise \ \, noted)$

| Parameter                                                                                                                                                                                                      | Min                                       | Тур                               | Max               | Units                            | Condition                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------|-------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRANSMIT CHANNEL                                                                                                                                                                                               |                                           |                                   |                   |                                  |                                                                                                                                                                                                                                            |

| SNR<br>THD                                                                                                                                                                                                     | 68<br>66                                  | 71<br>71                          |                   | dB<br>dB                         | The complete transmit path spectrum and pulse shape comply with ETSI requirements.                                                                                                                                                         |

| TRANSMIT DAC Clock Frequency Resolution Update Rate Output Voltage                                                                                                                                             |                                           | 12<br>2                           | 18.688<br>1168    | MHz<br>Bits<br>kHz<br>V p-p Diff | The transmit DAC maximum update rate is half the maximum output data rate, i.e., $1168 \text{ kHz}$ . The maximum transmit clock is $16 \times 1168 = 18.688 \text{ MHz}$ .                                                                |

| TRANSMIT FILTER Corner Frequency (3 dB) <sup>1</sup> Accuracy Gain                                                                                                                                             |                                           | $320$ $535$ $\pm 5$ $9.53$ $3.53$ | ±10               | kHz<br>kHz<br>%<br>dB<br>dB      | MODE_SEL1 = 0<br>MODE_SEL1 = 1                                                                                                                                                                                                             |

| LINE DRIVER<br>VCM<br>Output Power<br>Output Voltage                                                                                                                                                           |                                           | 2.5<br>13.5<br>6                  |                   | V<br>dBm<br>V p-p Diff           | Transformer Turns Ratio = 1:2.3 at 50 kHz<br>When Loaded by ETSI (RTR/TM3036)<br>HDSL Test Loops                                                                                                                                           |

| TRANSMIT VOLTAGE LEVEL                                                                                                                                                                                         |                                           | 6<br>3                            |                   | V p-p Diff<br>V p-p Diff         | TX_GAIN = 0<br>TX_GAIN = 1                                                                                                                                                                                                                 |

| RECEIVE CHANNEL SNR THD                                                                                                                                                                                        | 68<br>66                                  | 71<br>71                          |                   | dB<br>dB                         |                                                                                                                                                                                                                                            |

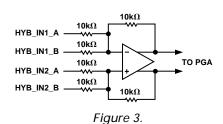

| HYBRID INTERFACE Input Voltage Range Input Impedance                                                                                                                                                           |                                           | 10                                | 5                 | V p-p Diff<br>kΩ                 | $V_{CM} = 2.5 \text{ V. See Figure 3}$                                                                                                                                                                                                     |

| PROGRAMMABLE GAIN AMPLIFIER Overall Gain Accuracy Gain Step Gain Step Accuracy                                                                                                                                 |                                           | ±1<br>3<br>±0.25                  |                   | dB<br>dB<br>dB                   | Condition -6 dB to +9 dB                                                                                                                                                                                                                   |

| RECEIVE FILTER Corner Frequency (-3 dB) <sup>1</sup> Accuracy                                                                                                                                                  |                                           | 320<br>640<br>±5                  | ±10               | kHz<br>kHz<br>%                  | MODE_SEL1 = 0<br>MODE_SEL1 = 1                                                                                                                                                                                                             |

| TIMING RECOVERY DAC Resolution Output Low Output High                                                                                                                                                          | 7                                         | 0.5<br>4.5                        |                   | Bits<br>V<br>V                   | Guaranteed Monotonic                                                                                                                                                                                                                       |

| DIGITAL INTERFACE Input Logic High, $V_{IH}$ Input Logic Low, $V_{IL}$ Output Logic High, $V_{OH}$ Output Logic Low, $V_{OL}$ Input Logic High, $V_{IH}$ Input Logic Low, $V_{IL}$ Output Logic High, $V_{OH}$ | $3.3$ $V_{DD} - 0.3$ $2.0$ $V_{DD} - 0.3$ |                                   | 0.8<br>0.4<br>0.2 | V<br>V<br>V<br>V<br>V<br>V       | $5$ V Supply, $V_{\rm MIN}$ to $V_{\rm MAX}$ $3.3~{\rm V~Supply},~V_{\rm MIN}~{\rm to}~V_{\rm MAX}$                                                                                                                                        |

| POWER SUPPLY VOLTAGE                                                                                                                                                                                           | 4.75<br>3.15                              | 5<br>3.3                          | 5.25<br>3.45      | V<br>V                           | V <sub>MIN</sub> to V <sub>MAX</sub><br>5 V Supply<br>3.3 V Supply                                                                                                                                                                         |

| POWER SUPPLY CURRENT Normal Mode, Excl. Driver OVRSAMP Mode Line Driver Low Power Mode                                                                                                                         |                                           | 65<br>73<br>50<br>17              |                   | mA<br>mA<br>mA<br>mA             | $\begin{array}{c} V_{MIN} \text{ to } V_{MAX}, \ T_{MIN} \text{ to } T_{MAX} \\ 5 \text{ V Supply, MODE\_SEL1} = 0 \\ 5 \text{ V Supply, MODE\_SEL1} = 1, \text{MODE\_SEL0} = 1 \\ With 50 \ \Omega \text{ Differential Load} \end{array}$ |

| OPERATING TEMPERATURE RANGE                                                                                                                                                                                    | -40                                       |                                   | +85               | °C                               | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                                                                                                                       |

#### NOTES

Specifications subject to change without notice.

$<sup>^1\</sup>mbox{The ADC}$  clock period  $t(1\div\mbox{ f})$  is used for the dynamic tuning of the Tx and Rx filters.

# **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage0.3 V to +6.0 V                                       |

|---------------------------------------------------------------------|

| Input Voltage0.5 V to $V_{DD}$ + 0.5 V                              |

| Output Voltage Swing $-0.5 \text{ V}$ to $V_{DD}$ + $0.5 \text{ V}$ |

| Operating Temperature Range (Ambient)40°C to +85°C                  |

| Storage Temperature Range65°C to +150°C                             |

| Lead Temperature (5 sec) MQFP+280°C                                 |

<sup>\*</sup>Stresses above those listed in this section may cause permanent damage to the device. This is a stress rating only, functional operation of the device at these or any other conditions above those in the operation section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Thermal Characteristics**

80-Lead Plastic Quad Flatpack Package  $\dots \theta_{JA} = 45^{\circ}\text{C/W}$

# **ORDERING GUIDE**

| Model    | Temperature    | Package                       | Package |

|----------|----------------|-------------------------------|---------|

|          | Range          | Description                   | Option  |

| AD6472BS | −40°C to +85°C | 80-Lead Plastic Quad Flatpack | S-80A   |

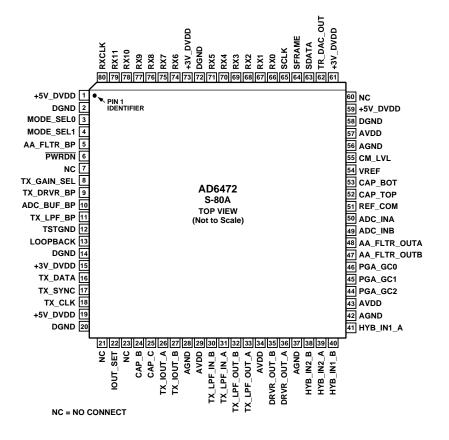

#### PIN CONFIGURATION

# CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD6472 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. 0 -3-

# AD6472

# PIN CONFIGURATIONS

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| DGND Digital Ground. 42 AGND Analog Ground. 45 MODE SEL0 Bit Rate—Filter Corner Select. 43 AVDD 45 V Analog Supply. 4 MODE_SEL1 Bit Rate—Filter Corner Select. 44 PGA_GC2 PGA Gain Select Bits. 5 AA_FLTR_BP Antitaliasing Filter Bypass. 45 PGA_GC1 PGA Gain Select Bits. 7 NC NC No Connect. 47 AA_FLTR_OUTB Differential Output of the Antialiasing Filter Bypass. 48 AA_FLTR_OUTB Differential Output of the Antialiasing Filter Bypass. 48 AA_FLTR_OUTB Differential Output of the Antialiasing Filter. 7 Differential Dutput of the Antialiasing Filter. 8 Differential Input to the AD_GLNB DIFFERENTIAL DIFFERENTI |        |

| MODE_SEL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |

| MODE_SEL1   Bit Rate—Filter Corner Select.   44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| 5AA_FLTR_BP<br>PWRDNAntialiasing Filter Bypass.45PGA_GC1<br>PGA_GC0PGA Gain Select Bits.6PWRDNPower-Down Active Low.46PGA_GC0PGA Gain Select Bits.7NCNo Connect.47AA_FLTR_OUTBPGA Gain Select Bits.8TX_GAIN_SEL<br>9 TX_DRVR_BP<br>10 ADC_BUF_BPTransmit Attenuation (6 dB) Select.Differential Output of the Antialiasing Filter.10ADC_BUF_BPADC_BUF_BPADC_BUF_BPDifferential Output of the Antialiasing Filter.11TX_LPF_BPTransmit Filter Bypass.49ADC_INBDifferential Input to the AD Differential DIFF                                                                                                                                                                                                                                                                                                                                                                  |        |

| PWRDN   Power-Down Active Low.   46   PGA_GC0   PGA Gain Select Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |

| 7NCNo Connect.47AA_FLTR_OUTBDifferential Output of the Antialiasing Filter.8TX_DRVR_BPTransmit Attenuation (6 dB) Select.AA_FLTR_OUTADifferential Output of the Antialiasing Filter.10ADC_BUF_BPADC Buffer Bypass.49ADC_INBDifferential Input to the AD antialiasing Filter.11TX_LPF_BPTransmit Filter Bypass.49ADC_INADifferential Input to the AD Differential In                                                                                                                                                                                                                                                  |        |

| TX_DRVR_BP ADC_BUF_BP ADC_BUffer Bypass. ADC_Buffer Bypass. ADC_Buffer Bypass. ADC_INB Differential Input to the AD DIFFERDIAL DIFFERDIA |        |

| ADC_BUF_BP ADC_BUF_BP Transmit Filter Bypass.  TX_LPF_BP Transmit Filter Bypass.  TSTGND Factory test pin. Connect to DGND. LOOPBACK Loopback Select. Loopback Select.  Digital Ground.  TX_DATA TX_SYNC Transmit Data Input. TX_CLK Transmit Clock Inpu |        |

| 11 TX_LPF_BP 12 TSTGND 13 LOOPBACK 14 DGND 15 +3 V_DVDD 16 TX_SYNC 17 Transmit Data Input. 18 TX_CLK 19 DGND 19 Jigital Ground. 19 +5 V_DVDD 20 DGND 21 NC 22 IOUT_SET 23 NC 24 CAP_B 25 CAP_C 26 TX_IOUT_A 27 TX_IOUT_B 28 AGND 29 AVDD 21 TX_LPF_IN R 21 TRANSMIT Filter Bypass. 49 ADC_INB 26 Differential Input to the AD 26 DGND 27 Alpe In NB 28 AGND 29 AVDD 20 DGND 21 TX_LPF_IN R 20 DGND 21 TX_LPF_IN R 21 TX_DAC Complementary Current Output. 24 AGND 25 AGND 26 Reference Common. 26 DGND 27 TX_LPF_IN R 28 AGND 30 TX_LPF_IN R 30 Differential Input to the AD 30 Transmit Filter Bypass. 49 ADC_INB 30 Differential Input to the AD 30 Transmit Filter Bypass. 49 ADC_INB 30 Differential Input to the AD 30 TRALPF IN R 49 ADC_INB 30 DC_INB 30 Differential Input to the AD 30 TRALPF IN R 49 ADC_INB 30 DC_INB 30 DGND 30 Differential Input to the AD 30 TRALPF IN R 49 ADC_INB 30 DC_INB 30 DAC_INB 30 DAC_INB 30 DAC_INB 30 DAC_INB 30 DAC_INB 30 DC_INB 30 Differential Input to the AD 30 DC_INB 30 Differential Input to LPE 30 ADC_INB 3DC_INB 3DC_ |        |

| TSTGND  TSTGND | _      |

| 13 LOOPBACK Loopback Select. 14 DGND Digital Ground. 15 +3 V_DVDD +3.3 V Digital Supply. 16 TX_DATA Transmit Data Input. 17 TX_SYNC Transmit Clock Input. 18 TX_CLK Transmit Clock Input. 19 +5 V_DVDD +5 V Digital Supply. 20 DGND Digital Ground. 21 NC No Connect. 22 IOUT_SET DAC Output Current Full Scale (With Resistor to Ground). 23 NC No Connect. 24 CAP_B Decoupling Pin for Internal Node. 25 CAP_C Decoupling Pin for Internal Node. 26 TX_IOUT_B TXDAC Complementary Current Output. 27 TX_IOUT_B TXDAC Complementary Current Output. 28 AGND Analog Ground. 29 AVDD +5 V Analog Supply. 30 TX_IPE_IN_B Differential Input to IPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| Digital Ground.  14 DGND 15 +3 V_DVDD 16 TX_DATA 17 TX_SYNC 18 TX_CLK 19 +5 V_DVDD 19 Digital Ground. 19 +5 V_DVDD 20 DGND 21 NC 22 IOUT_SET 25 DAC Output Current Full Scale (With Resistor to Ground). 26 TX_IOUT_A 27 TX_IOUT_A 28 AGND 29 AVDD 29 AVDD 20 DGND 21 TX_I PE IN B 20 Digital Ground. 29 AVDD 20 DGND 21 TX_IDUT_B 25 CAP_C 26 TX_IOUT_B 26 TX_IOUT_B 27 TX_IOUT_B 28 AGND 10 Digital Ground. 29 AVDD 15 Jigital Ground. 26 TX_IDE IN B 15 LOOFDACK 10 Digital Ground. 26 TX_IDIT_B 15 CAP_B Digital Supply. 27 TX_IDIT_B 15 CAP_B Digital Ground. 28 AGND 29 AVDD 29 AVDD 29 AVDD 20 DGND 21 NC 22 CAP_TOP 24 CAP_B Decoupling Pin for ADC Recovery Dactor Digital Output Data. 29 AVDD 20 DGND 21 NC 22 IOUT_SET 23 NC 24 CAP_B 25 CAP_C 26 TX_IOUT_A 26 TX_IOUT_B 27 TX_IOUT_B 28 AGND 29 AVDD 30 TX_I PE IN B 30 Differential Input to I DE 30 Decoupling Pin for ADC Recovery Dactor Recovery Dactor Decoupling Pin for ADC Recovery Dactor Recovery Dactor To Decoupling Pin for ADC Recovery Dactor Recovery Dactor To Decoupling Pin for ADC Recovery Dactor Recovery Dactor To Decoupling Pin for ADC Recovery Dactor Recovery Dactor To Decoupling Pin for Internal Node. 26 TX_IOUT_B 27 TX_IOUT_B 28 AGND 39 AVDD 40 Analog Ground. 43 V_DVD 45 V Dactor Recovery Dactor To Decoupling Pin for Internal Node. 65 SCLK 65 SCLK 66 RX0 66 RX0 67 RX1 66 Differential Input to I DE 67 RX1 67 RX1 67 Decoupling Pin for ADC Recovery Dactor Recovery Dactor To Decoupling Pin for Internal Pode 68 RX0 69 Decoupling Pin for Internal Pode 69 TX_I PE IN B 60 Decoupling Pin for Internal Node 60 NC 61                                                                                                                                                                                                                                                                                                               | ٥.     |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| TX_DATA Transmit Data Input. TX_SYNC Transmit Data Frame Sync Input. TX_SYNC Transmit Data Frame Sync Input. TX_SYNC Transmit Data Frame Sync Input. TX_CLK Transmit Clock Input. TX_CLK Transmit Clock Input. TX_CDATA TY_SYNC Transmit Data Frame Sync Input. TY_SYNC Transmit Data Input. TY_SYNC Transmit Data Frame Sync Input. TY_SYNC Transmit Data Frame Sync Input. TY_SYNC Transmit Data Input. TY_SYNC Transmit Data Frame Sync Input. TY_SYNC Transmit Data Input. TY_SY |        |

| TX_SYNC Transmit Data Frame Sync Input. Tx_SYNC Tx_OVDD Ty_Str Tx_Supply Voltage, Nomin Analog Ground. Ty AvDD Ty_AvDD |        |

| TX_CLK Transmit Clock Input.  18 TX_CLK Transmit Clock Input.  19 +5 V_DVDD TX_DGND TX |        |

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11 \   |

| 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IIy.)  |

| Digital Ground.   Serial Data Input to LPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| No Connect.   Some connect.    |        |

| DAC Output Current Full Scale (With Resistor to Ground).   Scale (With Resistor to G   |        |

| NC No Connect.  ACAP_B Decoupling Pin for Internal Node.  CAP_C Decoupling Pin for Internal Node.  TX_IOUT_A TXDAC Complementary Current Output.  TXDAC Complementary Current Output.  AGND Analog Ground.  Analog Ground.  TX_IOUT_B TX_IOUT_B TX_IOUT_B Differential Input to I_PE  TX_IOUT_B TX_IOUT_B TX_IOUT_B Differential Input to I_PE  TX_IOUT_B TX_IOUT_B TX_IOUT_B DECOUPLED TX_IOUT_B DIFFERENTIAL INPUT to I_PE  TX_IOUT_B TX_IOUT_B TIME DIFFERENTED TIME TX_IOUT_B DIFFERENTED TX_IOUT_B DIFFERENTED TIME TX_IOUT_B DIFFERENTED TX_IOUT |        |

| 24 CAP_B 25 CAP_C 26 TX_IOUT_A  27 TX_IOUT_B  28 AGND  29 AVDD  29 AVDD  20 CAP_B Decoupling Pin for Internal Node. Decoupling Pin for Internal Node. Decoupling Pin for Internal Node. TXDAC Complementary Current Output.  62 TR_DAC_OUT Voltage. Serial Data Input to Timing ery DAC.  63 SDATA  64 SFRAME Frame Sync for Timing Recovery DAC Output.  65 SCLK  Clock for Timing Recovery DAC Output.  66 RX0 Digital Output Data. Digital Output Data. Digital Output Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| 25 CAP_C 26 TX_IOUT_A  TXDAC Complementary Current Output.  TXDAC Complementary Curre |        |

| 25 CAP_C 26 TX_IOUT_A 27 TX_IOUT_B 28 AGND 29 AVDD 30 TX_IPF_IN_B 26 TX_IOUT_B 27 TX_IOUT_B 28 AGND 30 TX_IPF_IN_B 30 TX_IPF_IN_B 30 TX_IPF_IN_B 30 DEcoupling Pin for Internal Node. 48 SDATA 49 Serial Data Input to Timing ery DAC. 40 SFRAME 40 SFRAME 41 SFRAME 42 SFRAME 43 SCLK 44 SFRAME 45 SCLK 46 SFRAME 46 SCLK 46 RX0 47 Digital Output Data. 46 Digital Output Data. 47 Digital Output Data. 48 Digital Output Data. 49 Digital Output Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ut     |

| TX_IOUT_B  TX_DAC Complementary Current Output.  TXDAC Complementary Current Output.  | Pacov- |

| TX_IOUT_B  TXDAC Complementary Current Output.  Analog Ground.  Analog Ground.  TX_IPE_IN_B  TX_IPE_IN_B  TXDAC Complementary Current Output.  64 65 65 SCLK  Clock for Timing Rec Clock for Timing Re | recov- |

| 28 AGND AvDD AvDD AvDD Differential Input to LPE  Output.  65 SCLK Clock for Timing Recovery Serial Data.  RX0 Digital Output Data.  Digital Output Data.  Digital Output Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | very.  |

| 28 AGND Analog Ground. 29 AVDD +5 V Analog Supply. 30 TX LPF IN B Differential Input to LPF  Analog Ground. 66 RX0 Digital Output Data. Digital Output Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OAC.   |

| 29 AVDD +5 V Analog Supply. 30 TX LPF IN B Differential Input to LPF 67 RX1 Digital Output Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| 30   TX TPF IN R   Differential Innut to LPF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| TX_LPF_IN_A  TX_LPF_IN_A  Differential Input to LPF.  68 RX2  Digital Output Data.  Digital Output Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| 32   TX_LPF_OUT_B  Differential Output from Transmit 70   DV4   Digital Output Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

| (If Direct Dypassed).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |

| TX_LPF_OUT_A   Differential Output from Transmit   T1   RX5   Digital Output Data.   Digital Ground.   Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| (=====================================                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 34 AVDD +5 V Analog Supply. 73 +3 V_DVDD +3 V Digital Supply. 35 DRVR_OUT_B Differential Driver Output. 74 RX6 Digital Output Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| 36 DRVR_OUT_A Differential Driver Output. 75 RX7 Digital Output Data. 37 AGND Analog Ground. 76 RX8 Digital Output Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| The state of the s |        |

| The state of the s |        |

| 40 HYB_IN1_B Hybrid Inverting Input. 79 RX11 Digital Output Data. 80 RXCLK Clock Input for ADC Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

-4- REV. 0

AD6472

### **Circuit Description**

The AD6472 is an HDSL analog front end for either 2-pair or single pair applications.

### **Transmit Channel**

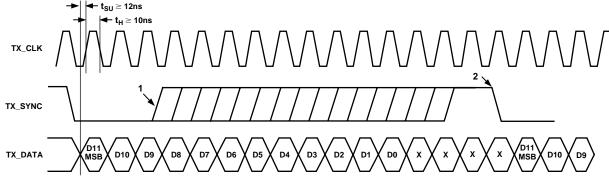

The AD6472 receives, from a DSP transceiver core, a serial 2s complement data stream. The data are 16-bit words and the MSB is received first.

The 12-bit DAC converts the digital data to an analog signal. Although HDSL uses four level 2B1Q modulation, the 12-bit DAC is necessary because of the linearity requirements of the echo canceling circuit.

The active filters have dynamic tuning and selectable filter corners that meet transmit mask requirements for both two-pair and single pair applications. A 6 dB attenuation option is included as part of the filter to increase the driver output dynamic range. Bypassing the active filter means giving up the 6 dB option, and reduces the maximum TX output voltage to 2 V p-p diff.

The filtered transmit signal is then processed by the driver amplifier. The DAC output controls the driver output level. The designer can choose to bypass the driver amplifier; in this case the driver amplifier will be powered down, and the TX output will be at the TX\_LPF\_OUT pins.

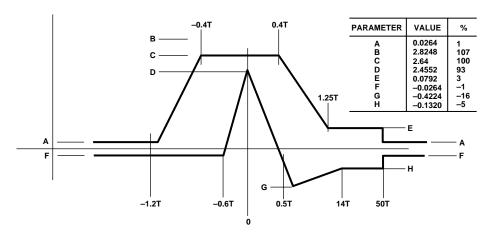

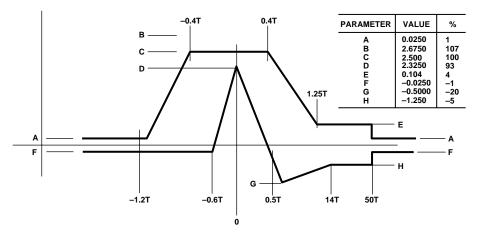

The AD6472 meets the requirements of the ETSI masks (both frequency and time domains for pulse shape). This includes the worst case in RTR/TM 3036.

Table I. Transmit Spectra

| Rate | Application    | Nyquist Frequency | Time Interval |

|------|----------------|-------------------|---------------|

| Kbps |                | kHz               | Τ (μs)        |

| 1168 | 2-Pair E1      | 292               | 1710          |

| 2320 | Single Pair E1 | 580               | 862           |

Figure 1. 2-pair Transmit Pulse Shape Mask Normalized

Figure 2. Single Pair Transmit Pulse Shape Mask Normalized

REV. 0 –5–

# AD6472

# **Receive Channel**

**Hybrid Amplifier**The hybrid amplifier perfo

The hybrid amplifier performs balanced to unbalanced conversion.

# Programmable Gain Amplifier (PGA)

The PGA can be programmed to amplify the receive signal from between -6 dB and 9 dB. Refer to Table II for PGA gain control information.

### **Transmit and Receive Filters**

Refer to Table III for transmit and receive channels filter control information. The receive channel filters meet ETSI requirements.

# Analog-to-Digital Converter (ADC)

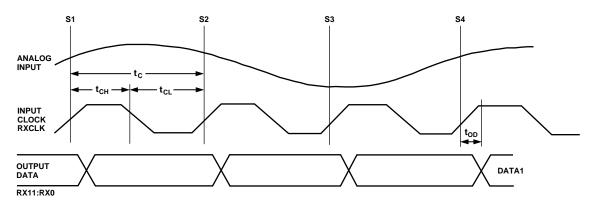

The receive channel ADC has a pipeline architecture with 12-bit resolution. The ADC can be clocked at 2320 kHz, maximum. Output data is provided in 2s complement form.

# Timing Recovery D/A

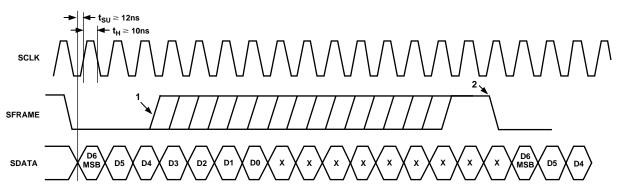

The AD6472 has an integrated D/A converter to control an external VCXO used for timing recovery. The D/A is 7 bits and monotonic. The D/A accepts 7 bits inverted format input data serially with the MSB first.

# **Configuration Control**

Table IV presents control information that you use to configure the AD6472.

Table II.

|         | Binary Count |         |           |