## MicroConverter™Technical Note - uC001 Using the ADuC812 I<sup>2</sup>C Interface

### **INTRODUCTION**

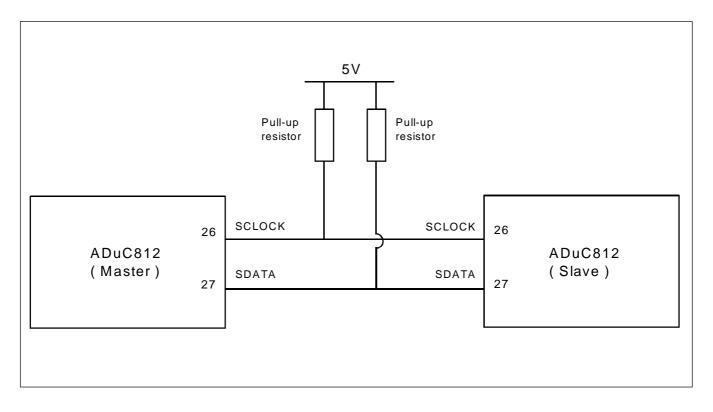

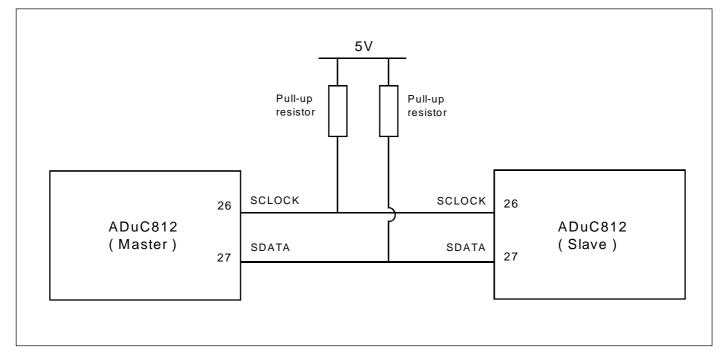

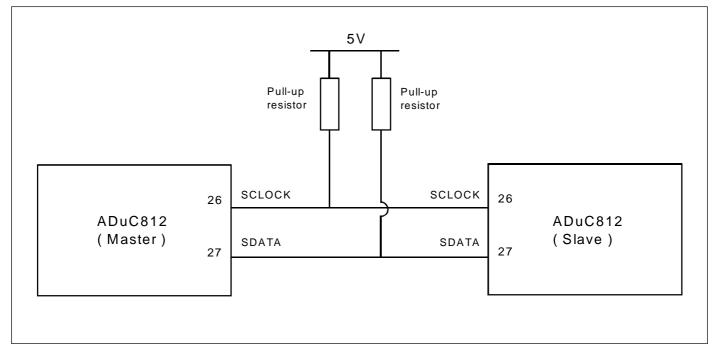

This Application Note describes the hardware and software implementation of an  $I^2C$  channel using the ADuC812 's on-chip  $I^2C$  interface. The  $I^2C$  channel described is a simple single master to single slave implementation as shown in figure 1 below.

Figure 1. I<sup>2</sup>C Block Diagram

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Ver 1.0 May 1999

™ MicroConverter is a Trademark of Analog Devices, Inc.

I<sup>®</sup> I<sup>°</sup>C is a Registered Trademark of Philips Semiconductors Inc.

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

## **I2C INTERFACE OVERVIEW**

The I<sup>2</sup>C (Inter Integrated Circuit ) is a two-wire serial communication system developed by Philips which allows multiple masters and multiple slaves connected via two wires (SCLOCK, SDATA).

The SCLOCK signal controls the data transfer between master and slave. The SDATA signal is used to transmit or receive data. Both lines are bidirectional. The bit-rate is controlled by the SCLOCK line.

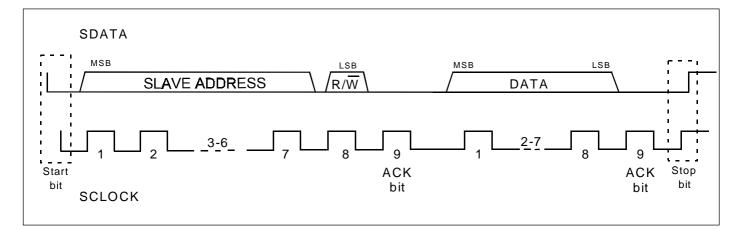

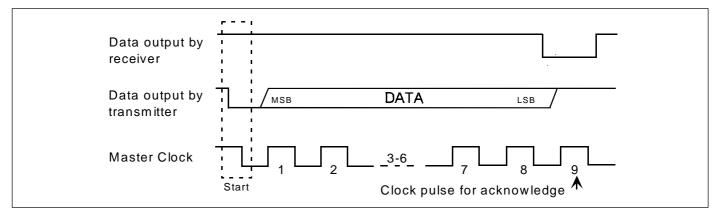

In an  $I^2C$  interface there is at least a single master and a single slave although  $I^2C$  can also support multi-master multi-slave configurations. The master generates the clock whereas the slave is driven by the clock. A typical data transfer sequence is shown in figure 2.

Figure 2. Typical I<sup>2</sup>C transfer sequence

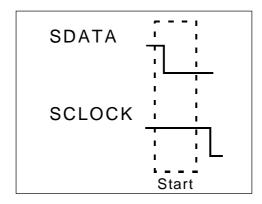

This sequence starts with a Start bit which is generated by the master. A start condition is indicated by a HIGH to LOW transition on the SDATA line while SCLOCK is HIGH as shown in figure 3.

Figure 3. Start Condition on the I2C bus

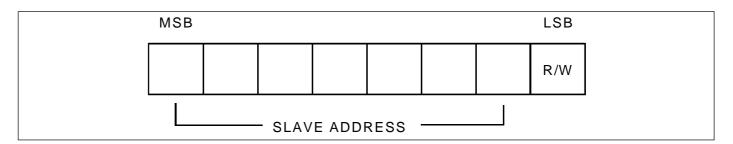

After the start condition the master sends a byte (MSB first) on the SDATA line which contains the slave address and a  $R/\overline{W}$  status bit. The first seven bits make up the slave address. The eight bit which is the LSB (least significant bit) determines the direction of the message (see figure 4). A '0' means that the master will write data to a selected slave. A '1' in this bit means that the master will read data from the slave. These operations will only occur once a valid acknowledge bit has been first received from the slave.

Figure 4. First byte after the START condition

When the master sends the address, each slave device in the system compares the first seven bits after the start condition with its own address. If they match, the slave device considers itself addressed by the master and replies by sending an acknowledge (see figure 5). An acknowledge is seen as a LOW level on the SDATA line at the 9th clock period and should be generated by the slave at the end of each byte in the transmission.

Figure 5. Acknowledge on the I<sup>2</sup>C bus

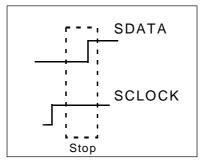

If there is no acknowledge or if the transfer is completed, the master generates a STOP condition defined by a LOW to HIGH transition on the SDATA line while SCLOCK is HIGH (see figure 6).

### Figure 6. Stop Condition on the I<sup>2</sup>C bus

## **I2C IMPLEMENTATION ON THE ADuC812**

This section describes the I<sup>2</sup>C implementation on the ADuC812 MicroConverter. The ADuC812 I2C interface provides both hardware slave and software master operating modes. The SCLOCK and SDATA are pins 26 and 27 respectively. On power on or reset, the I<sup>2</sup>C interface defaults to slave operation.

Three Special Function Registers (SFRs) are used to control this interface :

**I2CADD** : Holds the 7-bit address of the ADuC812 device on the bus (default value = 55H).

#### 7-bit address procedure :

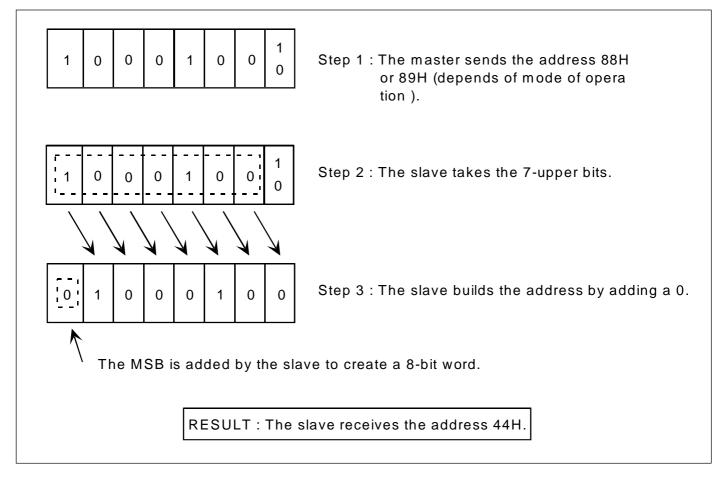

If the slave holds in its I2CADD register the value 44H, the master must send the value 88H to open communication with the slave. Because of the 7-bit address, the slave knows automatically that the LSB (least significant bit) is the Read / Write status bit. Therfore, the slave compares only the 7 upper bits to his own address. To make a complete word (8 bits), the slave adds a zero for the MSB (most significant bit). The result of this completion is compared to his own address (see figure 7 for an illustration).

Figure 7. Slave address procedure

**I2CDAT** : Holds the 8 data bits to be received or to be transmitted.

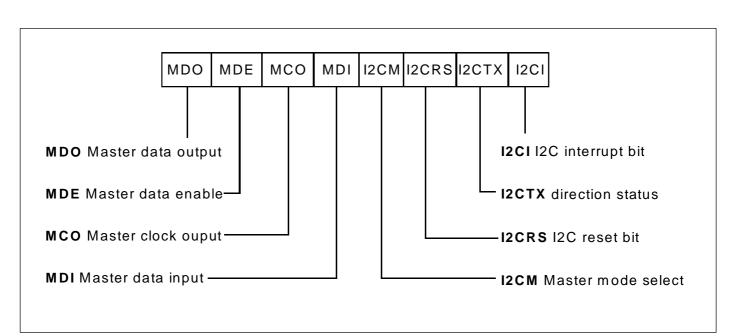

I2CCON : Holds configuration/control bits for master/slave mode of operation (see figure 7).

The slave uses the three lower bits of the I2CCON register. As the slave implementation is hardware, the slave will automatically detect a START bit, an acknowledge, an interrupt or STOP bits.

The master uses the four upper bits of the I2CCON register to control the generation of the master signals on the SCLOCK and SDATA pins. Therefore, in a software master, the user must generate both SCLOCK and SDATA signals in software using these bit addressable locations. For example, the bit that controls the SCLOCK signal ( pin 26 ) is defined as a bit addressable location ( MCO- bit address ) in the I2CCON register.

An example of code used to generate a continuous HIGH-LOW-HIGH pulses on the SCLOCK pin is shown below : AGAIN : SETB MCO

AGAIN

SETB MCO CLR MCO

JMP

## I<sup>2</sup>C COMMUNICATION (Master-transmitter to Slave-receiver)

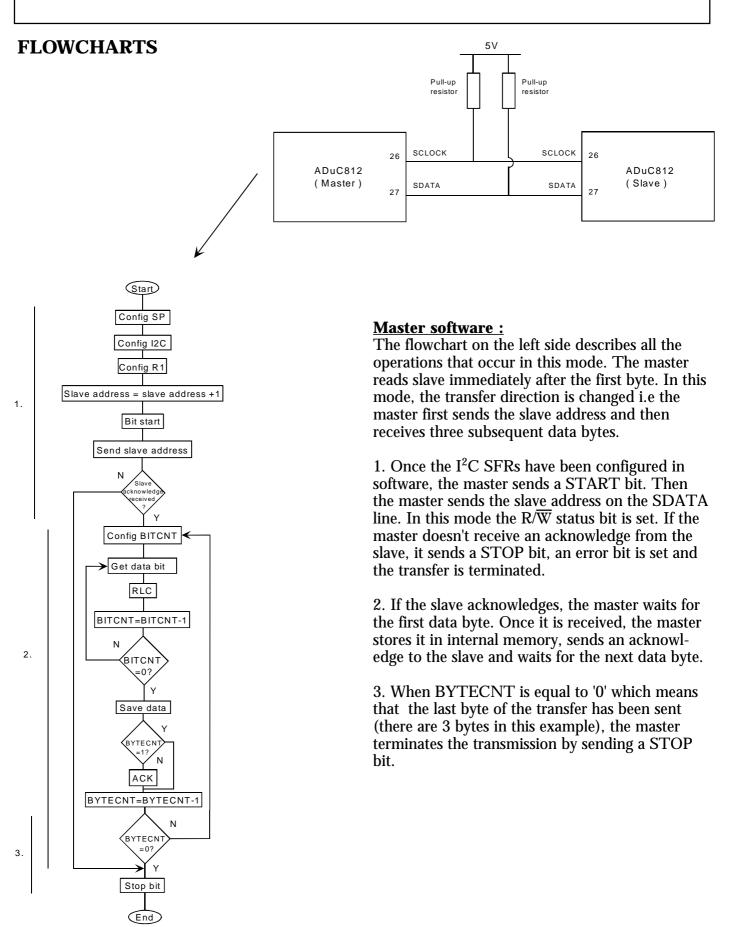

In this mode, the master both transmits the slave address and on receipt of a valid acknowledge also transmits three bytes ( the transmission/reception of three bytes is used for the code examples documented in this technical only) before terminating the communication by generating a stop bit.

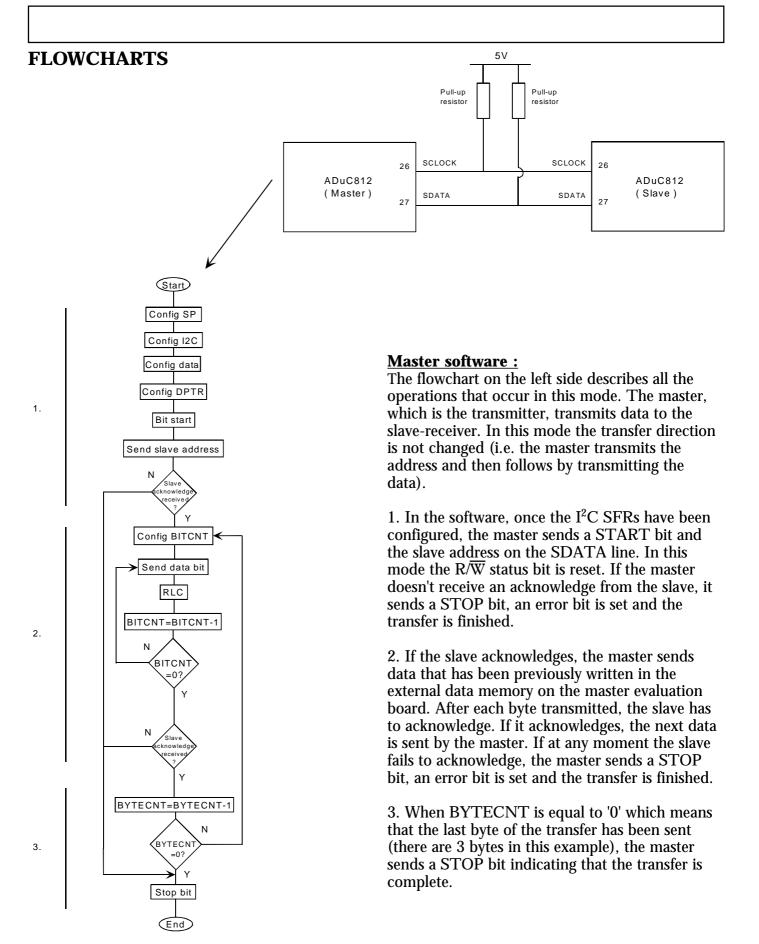

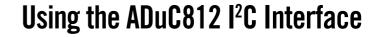

As you have two ADuC812s, you will need two different programs, one for the master, one for the slave. On the next two pages, you will find the flowcharts corresponding to both master and slave programs in a Master-transmitter Slave-receiver mode of operation.

The master uses this sequence of operations :

- -Send a Start bit. -Send the slave address. -Wait for a valid acknowledge bit. -Send the first data. -Wait for a valid acknowledge bit. -Send the second data. -Wait for a valid acknowledge bit.

- -Send the third data.

- -Wait for a valid acknowledge bit

- -Send a Stop bit.

The slave uses this sequence of operations :

-Receive address. -Send the acknowledge. -Receive the first data. -Send the acknowledge. -Receive the second data. -Send the acknowledge. -Receive the third data. -Send the acknowledge.

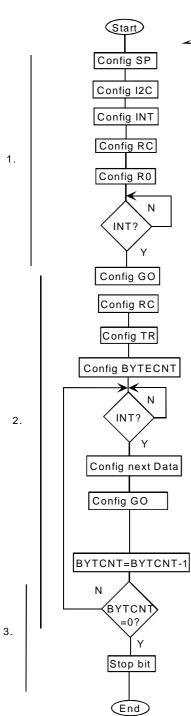

## I<sup>2</sup>C COMMUNICATION (Slave-transmitter to Master-receiver)

In this mode, the master transmits the slave address and on receipt of a valid acknowledge waits for three data bytes to be transmitted by the slave, before terminating the communication by generating a stop bit.

As you have two ADuC812s you again need two different programs, one for the master, one for the slave. On the next two pages, you will find the flowcharts corresponding to both master and slave programs in a Slave-transmitter to Master-receiver mode of operation.

The master uses this sequence of operations :

-Send a Start bit.

-Send the slave address.

-Wait for a valid acknowledge bit.

-Receive the first data.

-Send acknowledge.

-Receive the second data.

-Send acknowledge.

-Receive the third data.

-Send acknowledge.

-Send acknowledge.

-Send acknowledge.

-Send acknowledge.

The slave uses this sequence of operations :

-Receive address.

-Send the acknowledge.

-Send the first data.

-Expect acknowledge.

-Send the second data.

-Expect acknowledge.

-Send the third data.

-Expect acknowledge.

#### **Slave software :**

The flowchart on the left side describes the operations that occur in this mode. The master reads the slave immediately after the first byte. In this mode the transfer direction is changed i.e the master first sends the slave address and then receives three subsequent data.

1. In the software, once the I<sup>2</sup>C SFRs have been configured and after the START bit, which is sent by the master, the slave waits for the first data byte(the arrival of the data will generate an interrupt). Once it is received, the slave compares the data to its own address. If they match, the slave sends an acknowledge bit on the SDATA line.

2. As the  $R/\overline{W}$  status bit is set, the slave sends data that has been written previously in its internal memory.

After it has sent the data, the slave waits for an acknowledge from the master. After each valid acknowledge from the master, the slave sends another data byte and waits for the acknowledge.

3. When BYTECNT is equal to '0' which means that the last byte of the transfer has been sent (there are 3 bytes in this example), the master doesn't send an acknowledge but a STOP bit, and the transfer is terminated.

#### Note:

When an interrupt occurs, the interrupt bit (I2CI) is automatically set <u>but the user must clear it</u> in the interrupt routine (see line CLR I2CI in the code). If it's not cleared the slave will hold the clock line low thus disabling further I2C transmissions.

## CONCLUSIONS

The ADuC812 incorporates a software master, hardware slave I<sup>2</sup>C peripheral on-chip. While master mode I<sup>2</sup>C operation will require additional software overhead as described in this Application Note, software master mode uses the same SFR and identical I<sup>2</sup>C external pins to implement the I<sup>2</sup>C protocol and is capable of sustaining bit-rates in excess of 100Kbs.

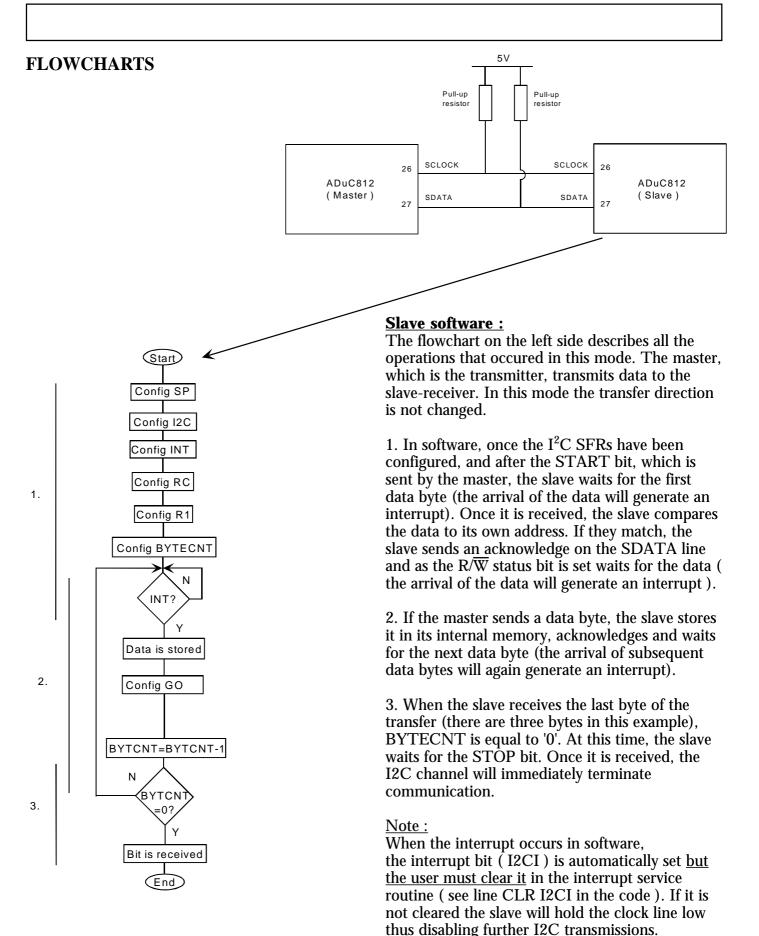

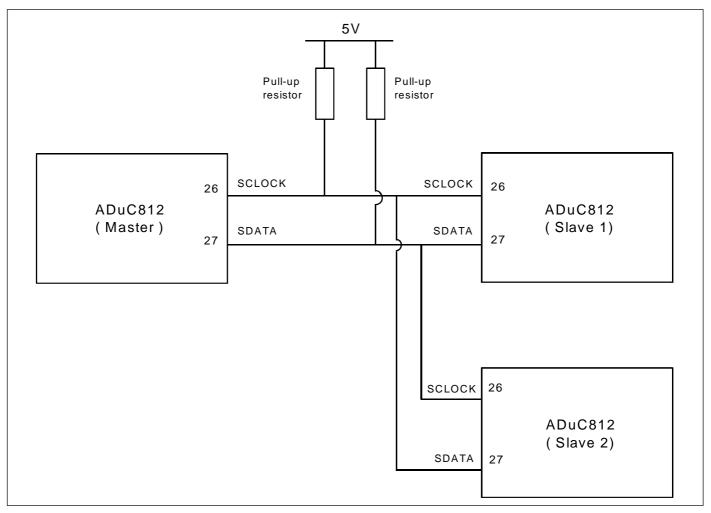

Even though a simple master/slave is described here, this can be easily extended to support multi-slave configurations as shown in figure 8 below.

Figure 8. 1-Master, 2-Slaves

#### Programs

The software described in this Application Note can be found at Analog Devices external web site : <u>http://www.analog.com/microconverter</u>

## FREQUENTLY ASKED QUESTIONS

#### **Question** :

When I run the code, both SDATA and SCLOCK lines stay low?

#### Answer :

Make sure that the external pull-up resistors ( 3.9k ) is present and connected to +5V on each line.

#### **Question** :

The master sends an address but there is no response from the slave?

#### Answer :

Be sure that the slave's I2CADD register is configured correctly.

#### **Question** :

The slave holds the value 44H in its I2CADD register, the master sends 44H but the slave doesn't acknowledge?

#### Answer :

Because of the 7-bit address, the master has to send 88H or 89H (depends of the  $R/\overline{W}$  status bit). For more details see page 4 of this application note.

#### **Question** :

The master sends the slave address and receives an acknowledge from the slave ; however the slave holds subsequently the SCLOCK line low?

#### Answer :

Each time the slave receives or sends a data, the interrupt bit (I2CI) is set and the slave runs an interrupt routine. In this interrupt routine the interrupt bit (I2CI) must be cleared otherwise the SCLOCK line will stay low.

#### **Question** :

The master sends the slave address, but it seems that the slave never reaches the interrupt? **Answer** :

Make sure that both interrupt registers (IE & IE2) are correctly configured.

IE = 80H enable all interrupts.

IE2 = 01H enable I2C interrupt.

## **APPENDIX A : MASTER.ASM**

| ;=======                                   | =======================================                         |                                                                                                       |  |  |  |

|--------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|

| ;<br>; Author :                            | Author : ADI - Apps                                             |                                                                                                       |  |  |  |

| ; Date :                                   | 7/24/98                                                         |                                                                                                       |  |  |  |

| ; File : n                                 | naster.asm                                                      |                                                                                                       |  |  |  |

| ; Description                              | : Code for a master in                                          | n an I2C system                                                                                       |  |  |  |

| ;========                                  |                                                                 |                                                                                                       |  |  |  |

| ,<br>\$MOD812                              | ;Us                                                             | e 8052 predefined Symbols                                                                             |  |  |  |

| ;                                          | Definitions                                                     |                                                                                                       |  |  |  |

| BITCNT<br>BYTECNT<br>SLAVEADD              | DATA 8h<br>DATA 030h<br>DATA 032h                               | ; bit counter for I2C routines<br>; byte counter for I2C routines<br>; slave address for I2C routines |  |  |  |

| FLAGS<br>NOACK<br>BUSY<br>ERROR<br>MISTAKE | DATA 28h<br>BIT FLAGS.<br>BIT FLAGS.<br>BIT FLAGS.<br>BIT P3.4  | 1 ; I2C busy flag                                                                                     |  |  |  |

| ORG 0                                      | он                                                              |                                                                                                       |  |  |  |

| ,                                          | JMP START                                                       |                                                                                                       |  |  |  |

| ORG 07BH ; Subroutines                     |                                                                 |                                                                                                       |  |  |  |

| ,                                          | ;;<br>; DELAY:Create a delay for the main signals(SCLOCK,SDATA) |                                                                                                       |  |  |  |

| ;<br>DELAY:                                |                                                                 |                                                                                                       |  |  |  |

RET

### ;------

## ; SENDSTOP:Send the bit stop of the transmission

| SENDSTOP: | SETB<br>CLR<br>SETB<br>ACALL | MDE<br>MDO<br>MCO<br>DELAY | ; to enable SDATA pin as an output<br>; get SDATA ready for stop<br>; set clock for stop |

|-----------|------------------------------|----------------------------|------------------------------------------------------------------------------------------|

|           | SETB<br>CLR<br>RET           | MDO<br>BUSY                | ; this is the stop bit<br>; bus should be released                                       |

;-----

; SENDBYTE:Send a 8-bits word to the slave

·\_\_\_\_\_

SENDBYTE:

| MOV                                    | BITCNT,#8                              | ; 8 bits in a byte                                                                       |

|----------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------|

| SETB<br>CLR<br>CLR                     | MDE<br>MDO<br>MCO                      | ; to enable SDATA pin as an output                                                       |

| LOOP:RLC<br>MOV<br>SETB<br>CLR<br>DJNZ | A<br>MDO,C<br>MCO<br>MCO<br>BITCNT,LOO | ; send one bit<br>; put data bit on pin<br>; send clock<br>; clock is off<br>OP          |

| CLR<br>SETB<br>JNB                     | MDE<br>MCO<br>MDI,NEXT                 | ; release data line for acknowledge<br>; send clock for acknowledge<br>; this is a check |

| SETB                                   | NOACK                                  | ; no acknowledge                                                                         |

| NEXT:CLR<br>RET                        | MCO                                    | ; clock for acknowledge                                                                  |

; BITSTART:Send the bit start of the transmission and the slave address to the slave

\_\_\_\_\_

| BITSTART: | SETB<br>SETB | BUSY<br>MDE | ; I2C is in progress<br>; to enable SDATA pin as an output |

|-----------|--------------|-------------|------------------------------------------------------------|

|           | CLR          | NOACK       |                                                            |

|           | CLR          | ERROR       |                                                            |

|           | JNB          | MCO,FAULT   |                                                            |

|           | JNB          | MDO,FAULT   |                                                            |

|           | CLR          | MDO         | ; this is                                                  |

|           | ACALL        | DELAY       | ; the                                                      |

|           | CLR          | MCO         | ; start bit                                                |

| FAUL      | T:           |             |                                                            |

|           | CLR          | MISTAKE     | ; set error flag                                           |

|           | MOV          | A,SLAVEADD  | ; Get slave address                                        |

|           | ACALL<br>RET | SENDBYTE    | ; call the routine to send the slave address byte          |

; SENDATA:Send all the sequence to the slave (slave address + data)

;-----

| SENDATA: | ACALL | BITSTART       |

|----------|-------|----------------|

|          | JB    | MDI,NEXT1      |

|          | MOV   | A,#00          |

| SLOC     | P:    |                |

|          | MOVX  | A,@DPTR        |

|          | ACALL | SENDBYTE       |

|          | INC   | DPTR           |

|          | JB    | NOACK,NEXT1    |

|          | DJNZ  | BYTECNT, SLOOP |

| NEXT     | 1:    |                |

| ACALL   | SENDSTOP |

|---------|----------|

| MOV     | A,FLAGS  |

| ANL     | A,#07h   |

| JZ      | RETOUR   |

| SETB    | P3.4     |

| CLR     | RST      |

| RETOUR: |          |

| RET     |          |

####

; RCVBYTE: receives one byte of data from an I2C slave device.

•

| RCVBYTE: | MOV                                                       | BITCNT,#8                                         | ;Set bit count.                                                             |

|----------|-----------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------|

| LOOP2:   | CLR<br>CLR<br>SETB                                        | MDE<br>MCO<br>MCO                                 | ;Data pin of the master is now an input                                     |

|          | CLR<br>MOV<br>RLC                                         | MCO<br>C,MDI<br>A                                 | ;Get data bit from pin.<br>;Rotate bit into result byte.                    |

|          | DJNZ                                                      | BITCNT,LOOP2                                      | ;Repeat until all bits received.                                            |

|          |                                                           |                                                   | ;result byte is in the accumulator                                          |

|          | PUSH                                                      | ACC                                               | ;Save result byte in the stack                                              |

|          | SETB                                                      | MDE                                               | ;Data pin of the master must be an output for<br>;the acknowledge           |

|          | MOV<br>CJNE<br>SETB<br>SJMP                               | A,BYTECNT<br>A,#1,SACK<br>MDO<br>NACK             | ;Check for last byte of frame.<br>;Send no acknowledge on last byte.        |

| SACK     | CLR                                                       | MDO                                               | ;Send acknowledge bit.                                                      |

| NAC      | K:<br>SETB<br>POP<br>ACALL<br>CLR<br>SETB<br>ACALL<br>CLR | MCO<br>ACC<br>DELAY<br>MCO<br>MDO<br>DELAY<br>MDE | ;Send acknowledge clock.<br>;Restore accumulator<br>;Clear acknowledge bit. |

|          | RET                                                       |                                                   |                                                                             |

······

;RCVDATA: receives one or more bytes of data from an I2C slave device.

;------

| RCVDATA:                                                                                    |                                                                               |                                                                                                                      |                                                                                                                                  |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                                                                                             | INC<br>ACALL<br>JB                                                            | SLAVEADD<br>BITSTART<br>NoAck,RDEX                                                                                   | ;Set for READ of slave.<br>;Acquire bus and send slave address.<br>;Check for slave not responding.                              |

| RDLoop:                                                                                     | ACALL<br>MOV<br>INC<br>DJNZ                                                   | RCVBYTE<br>@R1,A<br>R1<br>BYTECNT,RDLoop                                                                             | ;Receive next data byte.<br>;Save data byte in buffer.<br>;Advance buffer pointer.<br>;Repeat untill all bytes received.         |

| RDEX:                                                                                       | ACALL<br>RET                                                                  | SENDSTOP                                                                                                             | ;Done, send an I2C stop.                                                                                                         |

| ; Main progra                                                                               | am                                                                            |                                                                                                                      |                                                                                                                                  |

| ,<br>START:                                                                                 | MOV<br>CLR<br>MOV<br>MOV<br>MOV                                               | SP,#040h<br>NOACK<br>SLAVEADD,#088H<br>BYTECNT,#3<br>I2CCON,#0A8h                                                    | program                                                                                                                          |

| -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | ; code for a v<br>MOV<br>MOV<br>MOV<br>MOV<br>MOV<br>MOV<br>MOV<br>MOV<br>MOV | write mode (master-t<br>DPTR,#080H<br>@DPTR,A<br>DPTR,A081H<br>A,#044H<br>@DPTR,A<br>DPTR,A02H<br>A,#033H<br>@DPTR,A | ransmitter transmits to slave-receiver )<br>; master transmits to slave<br>; datas which are located in<br>; the external memory |

| •<br>3<br>•                                                                                 | MOV<br>ACALL                                                                  | DPTR,#080h<br>SENDATA                                                                                                |                                                                                                                                  |

|                                                                                             | ; code for a r                                                                | ead mode ( master re                                                                                                 | eads immediately after first byte)                                                                                               |

| FND                                                                                         | MOV<br>ACALL                                                                  | R1,#035h<br>RCVDATA                                                                                                  |                                                                                                                                  |

END

### **APPENDIX B : SLAVE.ASM**

| ;<br>; File :<br>;         | ; Date : 7/24/98  |                                           |                                                                                                    |  |  |

|----------------------------|-------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|

| ;========<br>;<br>\$MOD812 |                   | Use 80;                                   | 52 predefined Symbols                                                                              |  |  |

| ;                          |                   | Definitions                               |                                                                                                    |  |  |

| BYTECNT                    |                   | DATA 030h                                 | ; byte counter for I2C routines                                                                    |  |  |

| FLAGS<br>GO<br>RC<br>TR    | BIT<br>BIT<br>BIT | DATA 28h<br>FLAGS.0<br>FLAGS.1<br>FLAGS.2 | ; flag for all the interrupts<br>; flag for Write mode interrupt<br>; flag for Read mode interrupt |  |  |

| ORG                        | 00H               |                                           |                                                                                                    |  |  |

| ;                          | JMP               | START                                     | ; jump to label 'start'                                                                            |  |  |

| ,                          | ORG               | 03Bh                                      | ; I2C slave interrupt                                                                              |  |  |

| ·                          | JB<br>JB          | RC,RECEIVE<br>TR,TRANSMIT                 | ; depending on flags there<br>; are two different interrupts                                       |  |  |

|                | ORG                             | 07BH                   | ; Subroutines                                                                                                  |

|----------------|---------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------|

| ,              | receive interru                 | -                      |                                                                                                                |

| ,<br>RECEIVE:  | SETB<br>MOV<br>CLR<br>RETI      | ISI                    | T; move data on internal RAM<br>; clear interrupt bit                                                          |

| ,              | : transmit inte                 |                        |                                                                                                                |

| ,<br>TRANSMIT: | SETB<br>MOV<br>CLR<br>RETI      | GO<br>I2CDAT,R0<br>ISI | ; clear interrupt bit                                                                                          |

| RCVBYTE2       | receive byte                    | routine for rea        |                                                                                                                |

| ,<br>RCVBYTE2: |                                 |                        |                                                                                                                |

|                | NOP<br>RET                      |                        |                                                                                                                |

| ,              | receive byte r                  | outine                 |                                                                                                                |

| RCVBYTE:       |                                 |                        |                                                                                                                |

| WAIT           | T1:<br>JNB<br>INC<br>CLR<br>RET | GO,WAIT1<br>R1<br>GO   | ; wait for the interrupt<br>; next storage will be on 41h then 42h<br>; flag is cleared for the next interrupt |

Г

# Using the ADuC812 $I^2C$ Interface

| ,<br>;RCVDATA:         | receive bytes               | s routine            |                                                                        |

|------------------------|-----------------------------|----------------------|------------------------------------------------------------------------|

| RCVDATA:               |                             |                      |                                                                        |

| LOOP2:                 | MOV<br>ACALL<br>DJNZ<br>RET | RCVBYTE              | ; 4 bytes : address + 3 datas                                          |

| SENDBYTE               | byte transm                 | it routine           |                                                                        |

| SENDBYTE               | :                           |                      |                                                                        |

| WAIT                   | 2:JNB<br>INC<br>CLR<br>RET  | GO,WAIT2<br>R0<br>GO | ; wait for the interrupt<br>; second data is 34h and third data is 35h |

| ;SENDATA:              | bytes transm                | it routine           |                                                                        |

| ,<br>SENDATA:<br>LOOP: | MOV<br>ACALL                |                      | ; 3 data will be send by the slave                                     |

BYTECNT,LOOP

DJNZ RET

## ;Main program

#### START:

| CLR<br>MOV<br>MOV | GO<br>I2CADD,#044h<br>SP.#020h | ; clear flag used in the interrupt<br>; slave address |

|-------------------|--------------------------------|-------------------------------------------------------|

| MOV               | IE,#80h                        | ; enable all the interrupts                           |

| MOV               | IE2,#01h                       | ; enable I2C interrupt                                |

| MOV               | I2CCON,#000h                   | ; slave mode                                          |

\_\_\_\_\_

-----

; code for a write mode ( master-transmitter transmits to slave-receiver )

| SETB  | RC       | ; specific flag for the interrupt routine         |

|-------|----------|---------------------------------------------------|

| MOV   | R1,#040h | ; first data will be store in internal RAM at 40h |

| ACALL | RCVDATA  | ; slave receives his address + 3 datas            |

; code for a read mode ( master reads slave immediately after first byte )

| SETB<br>MOV<br>ACALL<br>CLR<br>SETB<br>ACALL | RC<br>R0,#033h<br>RCVBYTE2<br>RC<br>TR<br>SENDATA | ; specific flag for the interrupt routine<br>; first data send is 33h<br>; slave receives the address send by the master<br>; slave sends 3 datas |

|----------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| CLR P3.4                                     |                                                   | ; led is off, everything is OK                                                                                                                    |

END

;;;;