Rzeczpospolita Polska

Unia Europejska Europejski Fundusz Społeczny

Politechnika Śląska jako Centrum Nowoczesnego Kształcenia opartego o badania i innowacje

POWR.03.05.00-IP.08-00-PZ1/17

Projekt współfinansowany przez Unię Europejską ze środków Europejskiego Funduszu Społecznego

#### **Microprocessor and Embedded Systems**

Faculty of Automatic Control, Electronics and Computer Science, Informatics, Bachelor Degree

#### Lecture 15

# Memory addressing extensions

**B**artłomiej Zieliński, PhD, DSc

Program:

- Page Size Extension

- Physical Address Extension

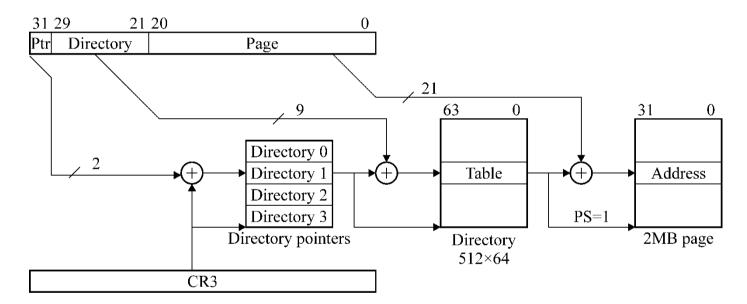

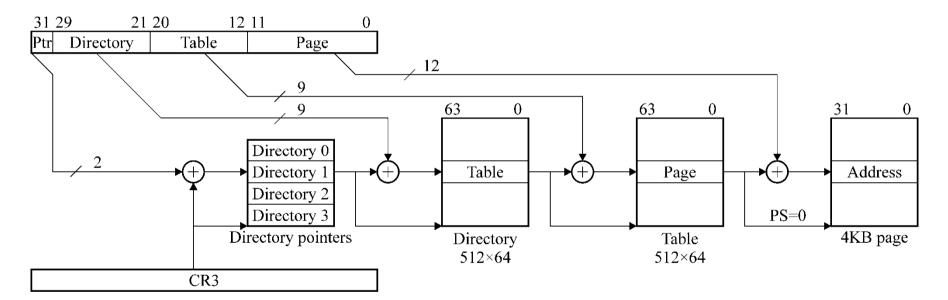

- PAE Physical Address Extension

- From Pentium Pro and Athlon

- 3 levels page table hierarchy

- 64-b table entries

- Direct access to over 4GB

- In x86-64 Long mode further extends to 4 levels

- Visible in a  $\mu p$  that has separate address bus

- A0..A35  $\rightarrow$  64 GB total memory

- Less apparent for HT or QPI-equipped  $\mu p's$

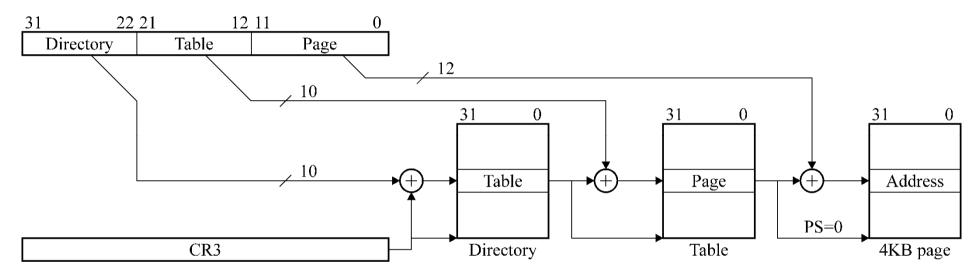

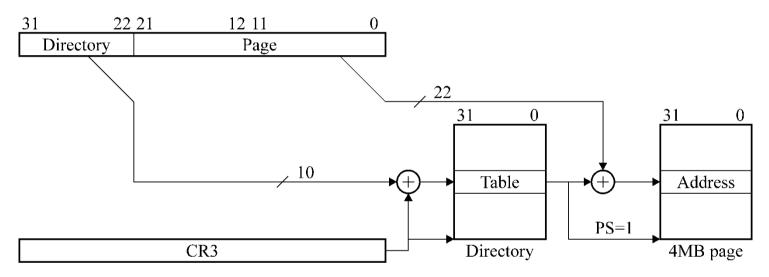

- PSE Page Size Extension

- Reduces system performance decrease when using "small" (4KB) pages

- E.g., 1MB memory

- 256 pages

- TLB entirely filled

- With PSE, 1MB = 1 page

- Only one TLB entry needed

- But internal fragmentation appears

- No PAE, 4KB page (as in 486)

- No PAE, 4MB page (PSE - Page Size Ext.)

– PAE, 4KB page

– PAE, 2MB page