# Politechnika Śląska jako Centrum Nowoczesnego Kształcenia opartego o badania i innowacje

POWR.03.05.00-IP.08-00-PZ1/17

Projekt współfinansowany przez Unię Europejską ze środków Europejskiego Funduszu Społecznego

#### Microprocessor and Embedded Systems

Faculty of Automatic Control, Electronics and Computer Science, Informatics, Bachelor Degree

#### Lecture 10

# 64-bit microprocessors AMD Athlon 64

Bartłomiej Zieliński, PhD, DSc

#### Program:

- Genesis of 64-b processors

- AMD Athlon

- Main properties

- Structure

- Operating modes

- HyperTransport bus

- System architecture

- Signalling

- Data packet communication

- Genesis of 64-b processing

- Goal:

- μp for highly efficient workstations and servers

- Two ways:

- AMD: evolution

- Extension of x86 architecture

- Intel: revolution

- Completely new (but interesting) architecture

- Discussion on AMD approach

- μp for highly efficient workstations and servers

- In a simplified form for "usual" PCs

- Assumptions

- x86 has limitations, but proper development can remove or omit them

- Backward compatibility with hard- and software is a great advantage

- Existing code should be executed with maximum possible performance (no 64-b programs)

- A typical user may need 64-b PC to efficiently manage memory >4 GB

- Discussion on Intel approach

- μp for highly efficient workstations and servers

- Assumptions

- x86 has limitations

- Backward compatibility complicates μp structure and operation

- Backward compatibility makes modifications difficult

- Highly efficient μp don't have to execute existing code with maximum performance

- There will be optimised code for 64-b  $\mu p's$

- Typical user does not need 64-b processing

- → IA-64 does not even resemble x86

- Athlon 64 main properties

- Structure similar to 32-b Athlon

- Built-in DDRAM controller

- HyperTransport bus

- 64-b operating modes

- x86 registers extended to 64 bits

- Number of registers doubled

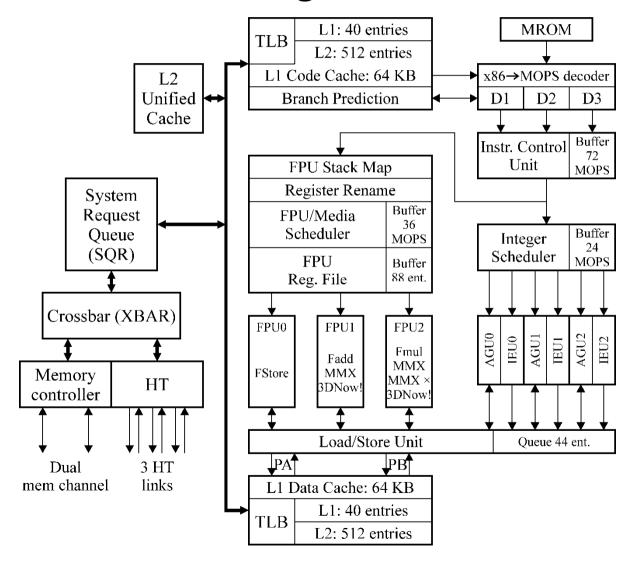

Athlon 64 – block diagram

## • Athlon 64 – registers

127

| 63 | 32 31 | 16 15              | 87 0 |

|----|-------|--------------------|------|

|    | RAX   | EAX                |      |

|    | RВX   | Ε <mark>β</mark> Χ | BX   |

|    | RÇX   | Ε¢Χ                | CX   |

|    | RÞX   | ΕÞΧ                | I    |

|    | RŞP   | Ε\$P               | SP   |

|    | ₽₿₽   | ΕŖ̈́Ρ              | ВP   |

|    | RSI   | EŞI                | ŞI   |

|    | rþi   | ΕÞΙ                | ŅΙ   |

|    | R8    |                    |      |

|    | R9    |                    |      |

|    | R10   |                    |      |

|    | R11   |                    |      |

|    | R12   |                    |      |

|    | R13   |                    |      |

|    | R14   |                    |      |

|    | R15   |                    |      |

| XMM0  |  |

|-------|--|

| XMM1  |  |

| XMM2  |  |

| XMM3  |  |

| XMM4  |  |

| XMM5  |  |

| XMM6  |  |

| XMM7  |  |

| XMM8  |  |

| XMM9  |  |

| XMM10 |  |

| XMM11 |  |

| XMM12 |  |

| XMM13 |  |

| XMM14 |  |

| XMM15 |  |

| ST0     |

|---------|

| ST1     |

| ST2     |

| ST3     |

| ST4     |

| ST5     |

| ST6     |

| <br>ST7 |

|         |

|         |

|         |

| RF ag | gs EFlags |

|-------|-----------|

| RIP   | EIP       |

- Athlon 64 operating modes

- Legacy for 32-b OS

- Typical x86, full-compatible with 32b, 16b apps

- No 64-b extensions

- LongMode for 64-b OS

- 64-b

- for 64-b apps

- 64-b processing

- 64-b registers

- Compatibility

- 32/16-b apps, no recompile necessary

- No 64-b extensions

- Athlon 64 main properties

- Built-in DDRAM controller

- Shorter delays (80 vs. 160 ns in NorthBridge)

- Higher throughput for random access

- Single (4 GB) or double (8 GB) channel

- 2.48 GBps/channel

- DDR support

- Less flexibility of memory selection

- Future upgrade to DDR2 support

- Memory access via NorthBridge still possible

- Athlon 64 main properties

- HyperTransport bus

- Open standard (opposite to Intel FSB)

- Serial, bi-dir, point-to-point links

- LVDS (Low Voltage Differential Signalling) 1.2V

- 400M to 2.8G transfers/s

- Data link 2, 4, 8, 16, 32 bits, can be asymetrical

- Up to 22.4 GBps

- Packet: 4..64 B payload, 8..12 B header

- Can cooperate with PCI, PCI-X, PCI-Express

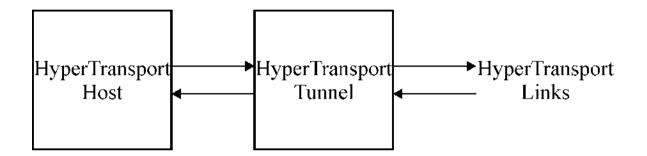

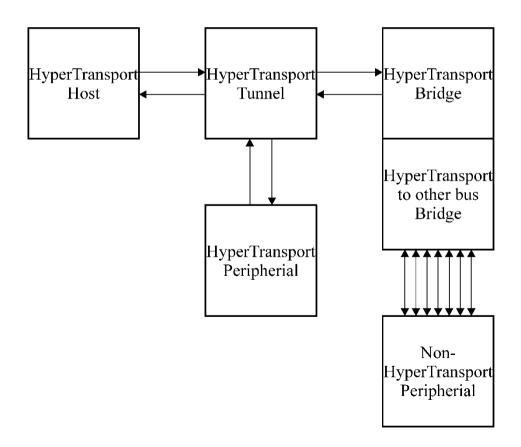

- HyperTransport Bus

- General architecture

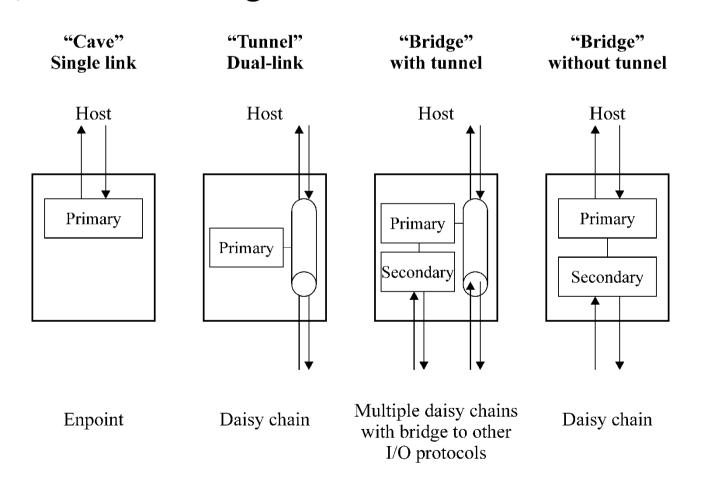

- HyperTransport Bus

- I/O device configurations

- HyperTransport Bus

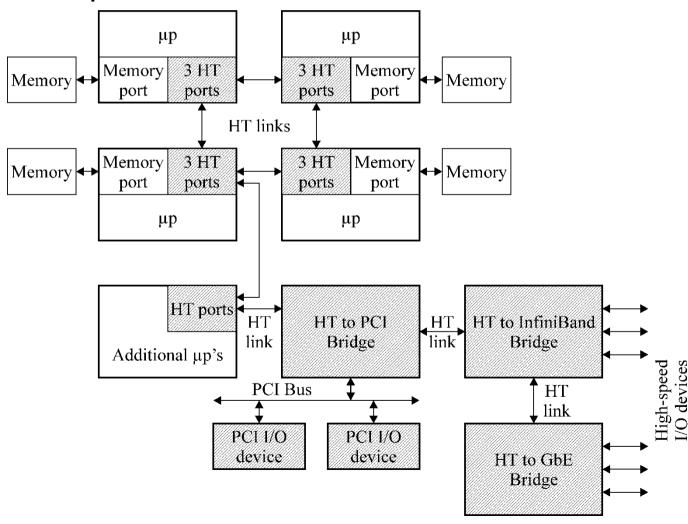

- System example

- Cooperation with PCI, PCI-X, PCI Express possible

- HyperTransport Bus

- Link

- Data path: 2, 4, 8, 16 or 32 bits

- Clock

- Control line

- Each signal = twin wire lines

- Signals

- CAD (command, address, data)

- CLK one per 8 CAD bits

2×, 4×, 8× only 1 CLK

- CTL control (1=control, 0=data)

- Reset, PWROK

- HyperTransport Bus

- Packet format

- Control 4 or 8 B

- Data 4..64 B

RdReq RdResp Data

4 B

Data

4..64 B

Low latency (low overhead)

WrReq

8 B

- E.g., PCI-Express:

- » 12-16 B transaction layer

- » 8 B data link layer

- » 8b/10b encoding (20%) physical layer

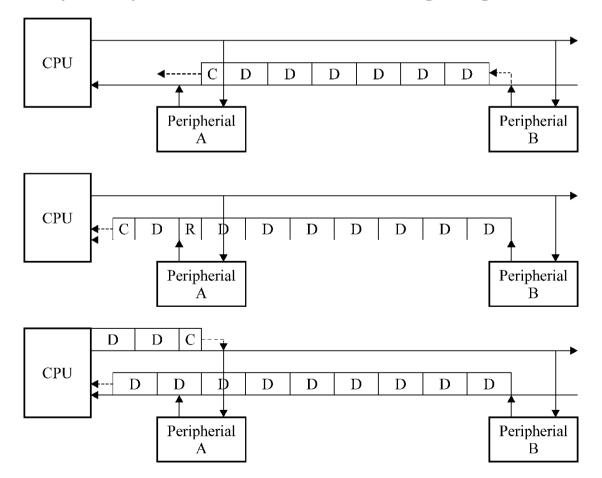

- HyperTransport Bus

- Priority Request Interleaving

- Request packet insertet into ongoing data stream

- HyperTransport Bus

- Example PC structure