Rzeczpospolita Polska

Unia Europejska Europejski Fundusz Społeczny

Politechnika Śląska jako Centrum Nowoczesnego Kształcenia opartego o badania i innowacje

POWR.03.05.00-IP.08-00-PZ1/17

Projekt współfinansowany przez Unię Europejską ze środków Europejskiego Funduszu Społecznego

#### **Microprocessor and Embedded Systems**

Faculty of Automatic Control, Electronics and Computer Science, Informatics, Bachelor Degree

#### Lecture 7

# **From EISA to PCI**

**B**artłomiej Zieliński, PhD, DSc

Program:

- EISA bus

- MCA architecture

- VLB architecture

- PCI architecture

- PCI signals

• PC architecture deployment

| Bus     | Data bits | Frequency [MHz] | Throughput [MBps] |

|---------|-----------|-----------------|-------------------|

| ISA     | 8 or 16   | 8.33            | 8.33              |

| EISA    | 32        | 8.33            | 33                |

| MCA     | 32        | 10              | 20                |

| VLB     | 32        | 40              | 120               |

| PCI 2.0 | 32        | 33              | 132               |

| PCI 2.0 | 64        | 33              | 264               |

| PCI 2.1 | 32        | 66              | 264               |

| AGP     | 32        | 66              | 264               |

| AGP     | 32        | 133             | 532               |

| AGP     | 32        | 266             | 1064              |

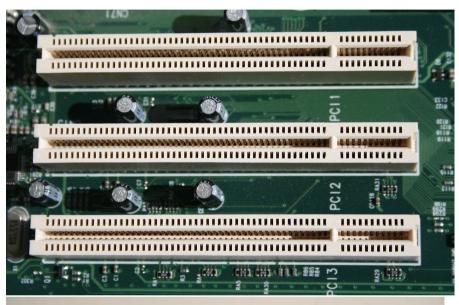

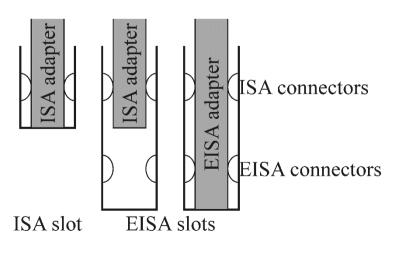

- EISA

- Extended Industry Standard Architecture

- Backward compatible with ISA

- 16/32-b recognition

- ISA cards work in EISA slots

- 2-level contact slot

- 98 ISA lines + 90 EISA-specific

- EISA

- Additional signals

- LA<sub>2..16</sub>, LA<sub>24..31</sub>

- $LA_{17..23}$  present in ISA

- Not buffered smaller delays

- D<sub>16..31</sub>, BE<sub>0..3</sub>

- EXE16, EXE32

- Force 16- or 32-b transfer

- Default = 8-b for compatibility

- EISA

- 32-b DMA, 8/16/32-b transfers, incl. 8237-like

- 7 channels

- 15 IRQ

- F<sub>clk</sub>=8.33 MHz (ISA)

- Memory access = CPU clock

- 1 clk / cycle

- EISA

- Configuration memory

- 4 KB

- Software-only device installation

- Configuration program for a card

- Numbered sockets

- МоВо: 0

- Slots: 1-15

- MoBo resources: MaxSlot+1..63

- BIOS tries to resolve resources conflicts

- MCA

- MicroChannel Architecture (IBM PS/2)

- 10 MHz, 2 clk/cycle

- 32-b DMA (no 8237-like)

- CPU + up to 16  $\mu$ p on expansion cards

- 4 arbitration bits

- Software-only device configuration

- Card numbers

- Socket numbers

- Software card disconnection possible

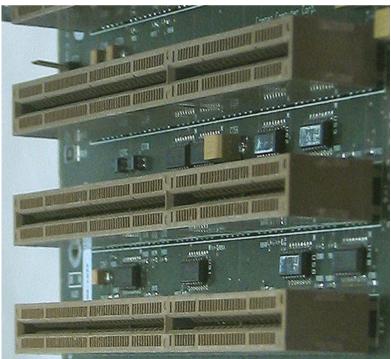

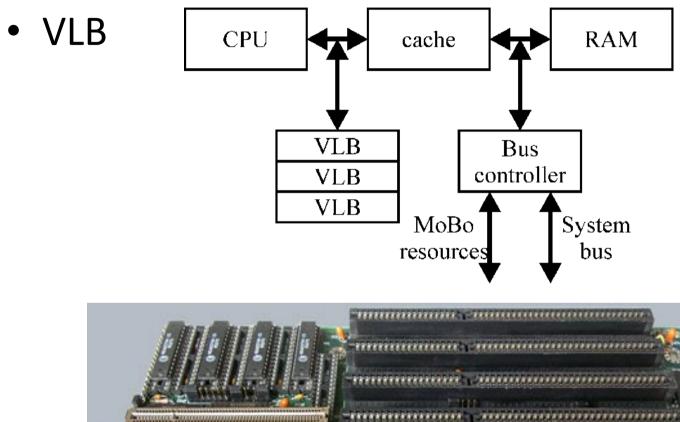

- VLB

- VESA Local Bus

- Video Electronics Standards Association

- Devices connected directly to  $\mu p$ 's local bus

- 80386, 80486, (also Pentium?)

- Fclk=CPU clk

- 1-3 slots

- Number of slots depends on frequency (?)

- 50 MHz 1 slot, 40 MHz 2 slots, 33 MHz 3 slots

- Card types

- Graphics card, HDD/FDD controllers, network cards

• VLB

- VLB

- Advantages

- Simplicity, low cost

- High throughput (up to 200 MBps @ 50 MHz)

- Disadvantages

- No auto-configuration

- Hardware-only configuration

- 486-signals dependence

- PCI-VLB bridges not very popular

- Limited number of slots

- Low reliability & scalability

- Problems with high frequencies

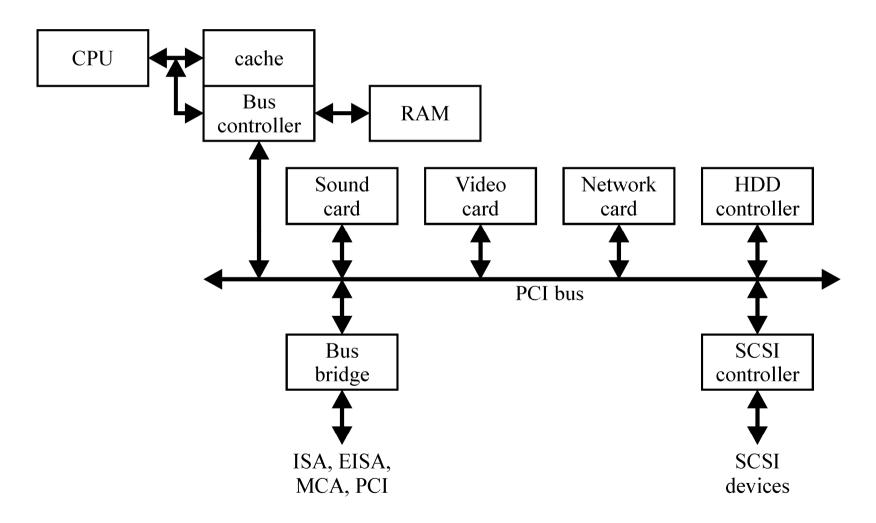

- PCI

- Peripherial Component Interconnect

- Very complex systems:

- 256 buses × 32 devices × 8 functions

- 33/66 MHz, 1 clk/cycle, 32/64 bits

- Devices:

- Initiator master

- Target slave

- Software configuration

- 256 B configuration memory

- Socket numbers

- Vendors & devices ID's

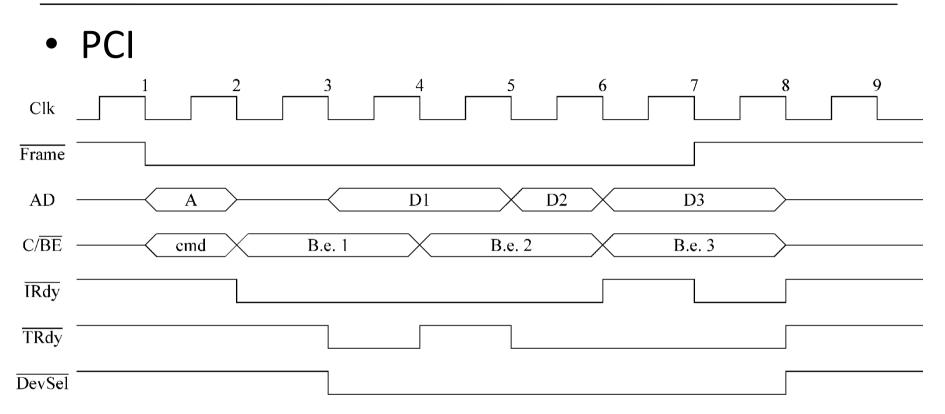

• PCI

- Frame=0  $\rightarrow$  read addr and cmd

- Addr  $OK \rightarrow devsel$

- Data exchange

- 1 clk/exchange

- Irdy, Trdy=1  $\rightarrow$  wait

- Frame=1  $\rightarrow$  end

- Devsel=1  $\rightarrow$  bus free

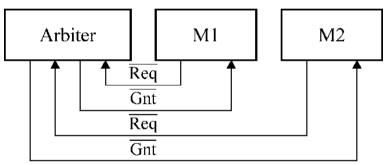

- PCI arbitration

- Performed when  $\geq 1$  master active

- Usually in Host/PCI, but not standarized

- Arbitration algorithm not defined

- E.g., round-robin, priority, etc.

- Possible during data transfer

- "hidden arbitration"

• PCI signals (basic – 32b and auxilliary – 64b)

| Master            | Signal                 | Slave             |

|-------------------|------------------------|-------------------|

| $\leftrightarrow$ | AD <sub>031</sub>      | $\leftrightarrow$ |

| $\rightarrow$     | $C/\overline{BE}_{03}$ | $\rightarrow$     |

| $\leftrightarrow$ | PAR                    | $\leftrightarrow$ |

| $\leftrightarrow$ | Frame                  | $\rightarrow$     |

| $\leftarrow$      | TRdy                   | $\leftarrow$      |

| $\rightarrow$     | IRdy                   | $\rightarrow$     |

| $\leftarrow$      | Stop                   | $\leftarrow$      |

| $\leftarrow$      | DevSel                 | $\leftarrow$      |

| ÷                 | IDSel                  | $\rightarrow$     |

| $\rightarrow$     | Req                    | ×                 |

| $\leftarrow$      | Gnt                    | ×                 |

| $\leftarrow$      | Clk                    | $\rightarrow$     |

| ÷                 | RST                    | $\rightarrow$     |

| $\leftarrow$      | PErr                   | $\leftarrow$      |

| $\rightarrow$     | SErr                   | $\leftarrow$      |

| Master            | Signal                 | Slave             |

|-------------------|------------------------|-------------------|

| $\leftrightarrow$ | AD <sub>3263</sub>     | $\leftrightarrow$ |

| $\rightarrow$     | $C/\overline{BE}_{47}$ | $\rightarrow$     |

| $\leftrightarrow$ | PAR64                  | $\leftrightarrow$ |

| $\leftrightarrow$ | Req64                  | $\rightarrow$     |

| $\leftarrow$      | Ack64                  | $\leftarrow$      |

| $\leftrightarrow$ | Lock                   | $\rightarrow$     |

| $\leftrightarrow$ | ClkRun                 | $\leftrightarrow$ |

| ×                 | <b>SBO</b>             | $\rightarrow$     |

| ×                 | Sdone                  | $\rightarrow$     |

| $\leftarrow$      | TDI                    | $\rightarrow$     |

| $\rightarrow$     | TDO                    | $\leftarrow$      |

| $\leftarrow$      | ТСК                    | $\rightarrow$     |

| $\leftarrow$      | TMS                    | $\rightarrow$     |

| $\leftarrow$      | TRst                   | $\rightarrow$     |

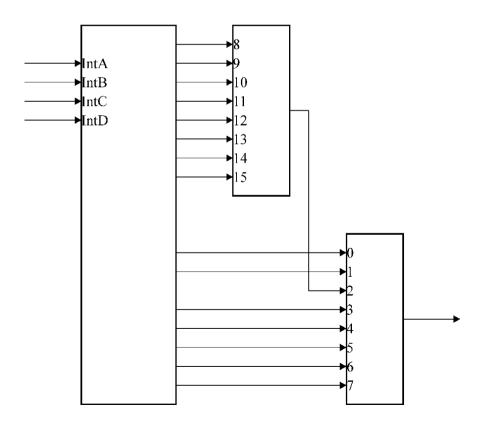

| $\rightarrow$     | IntA IntD              | $\leftarrow$      |

- PCI signals detailed

- AD address/data

- No bus sizing only 32- or 64-b transfers

- $-C/\overline{BE}$  command/byte enable

- Address phase command

- Data phase byte enable

- PAR parity check for AD and  $C/\overline{BE}$

- Parity error action depends on settings

- From ignore to NMI

#### • PCI signals detailed

| Code | Command                | Comment                                           |

|------|------------------------|---------------------------------------------------|

| 0    | IntAck                 | Read of interrupt controller; only for PC compat. |

| 1    | Special Cycle          | Broadcast to many targets                         |

| 2    | I/O Read               |                                                   |

| 3    | I/O Write              |                                                   |

| 4    | ®                      |                                                   |

| 5    | ®                      |                                                   |

| 6    | Mem Read               |                                                   |

| 7    | Mem Write              |                                                   |

| 8    | ®                      |                                                   |

| 9    | ®                      |                                                   |

| А    | Conf Read              |                                                   |

| В    | Conf Write             |                                                   |

| С    | Mem Read Multiple      | Long read beyond cache line                       |

| D    | Dual Address cycle     | 64-bit address from initiator                     |

| E    | Mem Read Line          | Read to the end of cache line                     |

| F    | Mem Write & Invalidate |                                                   |

- PCI signals detailed

- Frame activated by granted initiator

- Inactive during last transfer

- $-\overline{\text{TRdy}}$  target ready; inactive  $\rightarrow$  wait state

- IRdy initiator ready

- Stop immediate transmission end by target

- Reaction depends on  $\overline{TRdy}$  and  $\overline{DevSel}$

- DevSel address recognized by target

- No later than 2 clk after address sent

- IDSel used for Configuration rd/wr

- PCI signals detailed

- $-\overline{\text{Req}}, \overline{\text{Gnt}} \text{for initiator arbitration}$

- $-\overline{\text{PErr}}$  parity error

- $-\overline{\text{SErr}}$  system error other than parity;  $\rightarrow$  NMI

- PAR64 parity bits for 64-b extension

- $-\overline{\text{Req64}}$  attempt to perform 64-b transfer

- $-\overline{\text{Ack64}}$  64-b transfer allowed; timing like  $\overline{\text{DevSel}}$

- $-\overline{\text{Lock}}$  target locked

- ClkRun lower fclk; for power saving

- $-\overline{\text{SBO}}$  don't write to not update WriteBack cache

- PCI signals detailed

- $-\overline{\text{IntA}}$ ..  $\overline{\text{IntD}}$  interrupt lines

- Can be shared among PCI devices

- In PC translated to IRQ lines

- PCI signals detailed

- In PC, various INT assignment to various slots

- PCI devices can only use A6 pin

- INT conflits avoidance  $\rightarrow$  slot change

- Example assignment (from some real MoBo)

| Slot | A6 | A7 | B7 | <b>B8</b> |

|------|----|----|----|-----------|

| 1    | Α  | С  | В  | D         |

| 2    | В  | D  | А  | С         |

| 3    | С  | А  | В  | D         |

| 4    | Α  | В  | D  | С         |

| 5    | D  | В  | С  | А         |

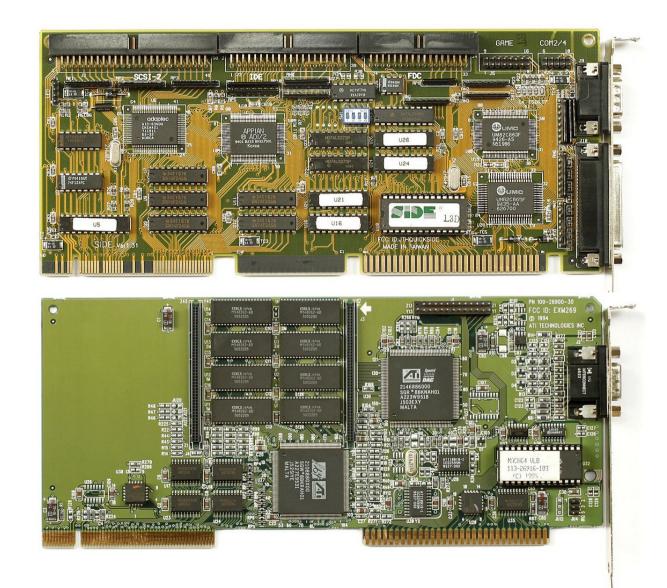

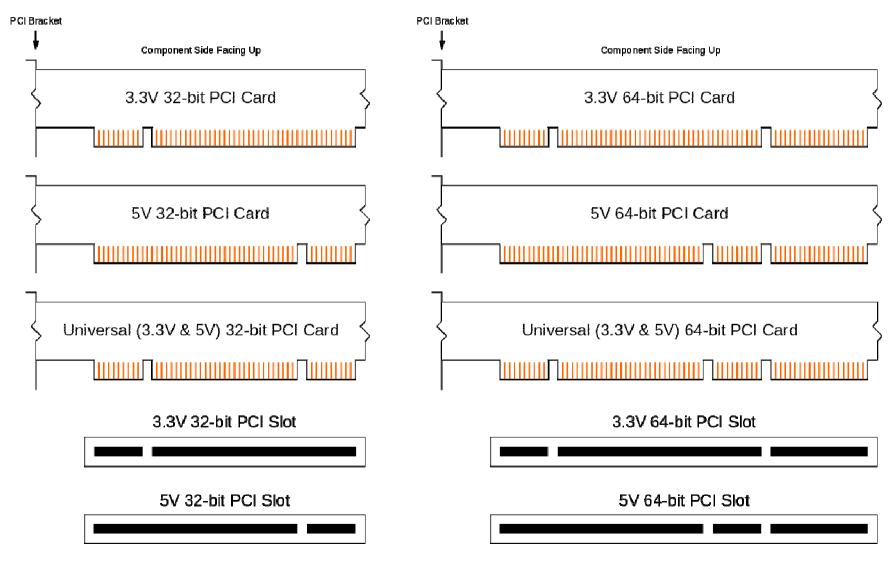

PCI – slot & card types

• PCI example photos