Rzeczpospolita Polska

Unia Europejska Europejski Fundusz Społeczny

Politechnika Śląska jako Centrum Nowoczesnego Kształcenia opartego o badania i innowacje

POWR.03.05.00-IP.08-00-PZ1/17

Projekt współfinansowany przez Unię Europejską ze środków Europejskiego Funduszu Społecznego

#### **Microprocessor and Embedded Systems**

Faculty of Automatic Control, Electronics and Computer Science, Informatics, Bachelor Degree

#### **Lecture 11**

#### PIC-family single-chip microcomputers Part 1 General architecture

**B**artłomiej Zieliński, PhD, DSc

Program:

#### (today)

- Von Neumann vs Harvard architecture

- PIC structure

- Memory organisation (next week)

- Built-in peripherials

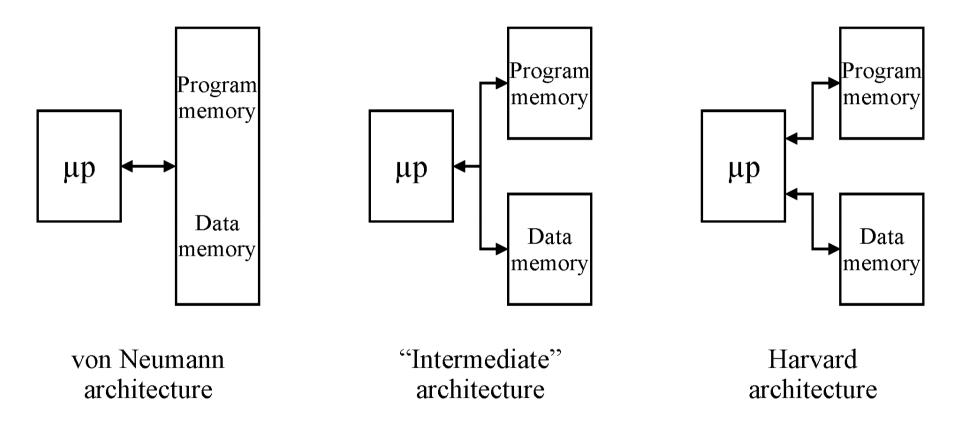

• Von Neumann vs Harvard architecture

- Von Neumann vs Harvard architecture

- Separate buses for program and data memories

- Data memory word length ≠ program memory word length

- Command code = 1 program memory word

- All code and data present in a single word

- Command code length and format can differ accross  $\mu p$  versions

- » Source-code compatibility

- Independent program and data memories access

- Parallel access

- » E.g., command 1 writes while command 2 is being fetched

- » Faster program execution  $\rightarrow$  pipellining

- Address ambiguity

- Must also specifiy program/data memory space

• PIC families

| Family    | Program | Commands | Examples               |

|-----------|---------|----------|------------------------|

| Base-line | 12 b    | 33       | PIC12Cxxx, PIC16Cx     |

| Mid-Range | 14 b    | 35       | PIC16C/Fxxx, PIC12C6xx |

| High End  | 16 b    | 55       | PIC17xxx               |

| Enhanced  | 16 b    | 77       | PIC18xxx               |

| dsPIC     |         |          |                        |

- Versions

- F = Flash

- C = OTP EPROM

- CR = ROM

- CE = OTP + EEPROM

- HV = High voltage (15V)

- L = Low voltage (2÷5.5V)

- E.g., LF, LCR, etc.

- PIC families

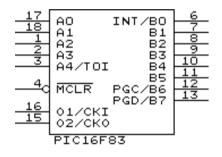

- Packages: 8, 18, 20, 28, 40, 64, 84 pins

- Built-in peripherials:

- EEPROM

- ADC, DAC

- Analogue comparator

- USART, SPI, I<sup>2</sup>C, CCP

- LIN, CAN, USB

- Temperature sensor

- Op-amp

- ...

• PIC – example pinouts

| 234567                                       | A1/AI1<br>A2/AI2/VR<br>A3/AI3/VR                              | H SCK/SCL/C3<br>SDI/SDA/C4                                                 | 15<br>16<br>17<br>18<br>23<br>24<br>25<br>26 |

|----------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------|

| 33<br>34<br>35<br>36<br>37<br>38<br>39<br>40 | BO/INT<br>B1/<br>B2<br>B3/PGM<br>B4<br>B5<br>B5/PGC<br>B7/PG0 | RX/DT/C7<br>PSP0/D0<br>PSP1/D1<br>PSP2/D2<br>PSP3/D3<br>PSP4/D4<br>PSP5/D5 | 26<br>19<br>20<br>21<br>22<br>27<br>28<br>29 |

| 1                                            | MCLR                                                          | PSP6/D6<br>PSP7/D7                                                         | 30                                           |

| <u>13</u><br>14                              | 01/CLKI<br>02/CLK0                                            | AI5/ <u>RD</u> /EO<br>AI6/ <u>WR</u> /E1<br>AI7/CS/E2                      | 8<br>9<br>10                                 |

|                                              | PIC16F877                                                     |                                                                            | _                                            |

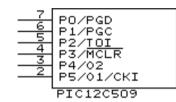

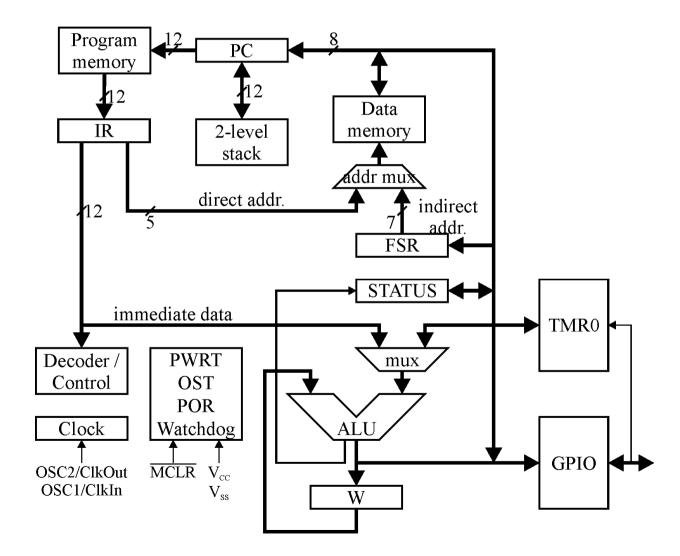

• PIC16F8x – general architecture

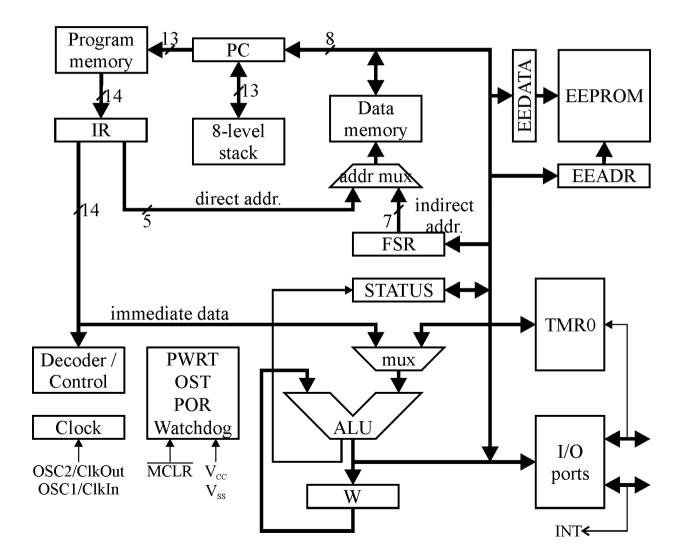

• PIC12C509 – general architecture

• PIC16C877 – general architecture

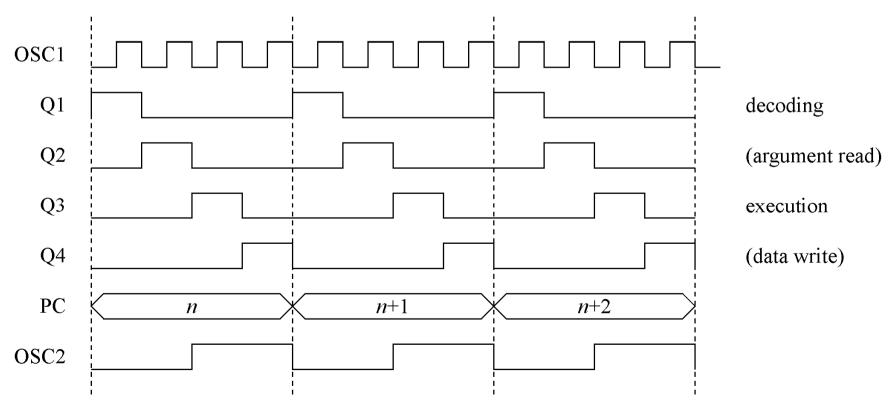

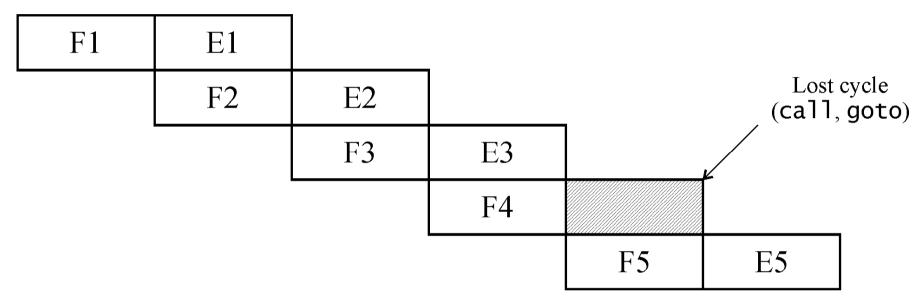

- PIC16F8x command cycle

- 4 machine cycles Q1÷Q4

- -1 machine cycle = 1 clock cycle

- e.g., 4 MHz  $\rightarrow$  1µs/command

• PIC16F8x – command cycle

- 1 command = 2 command cycles

- Except call, goto & others operating on PC

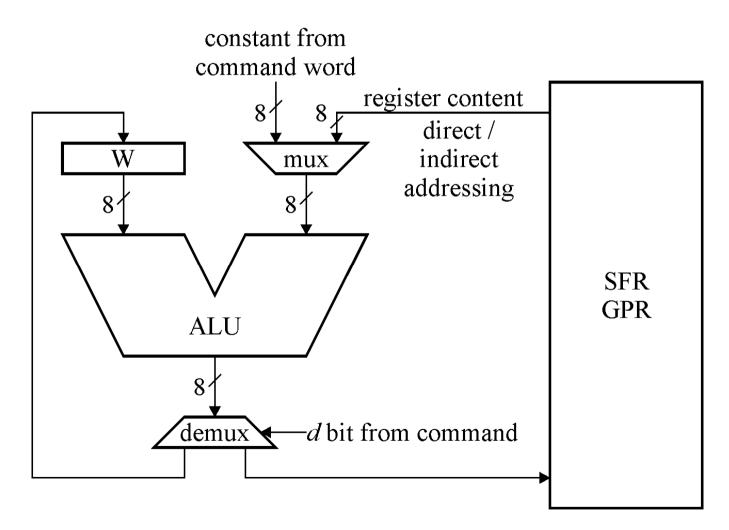

- PIC16F8x ALU operations

- Registers

- W register (*accumulator or not?*)

- GPR/SFR

- ALU arguments/results

- Arg1  $\leftarrow$  W

- Arg2 ← SFR, GPR or constant

- Result  $\rightarrow$  W, SFR, GPR

- Flags modification (STATUS reg.)

- C carry/borrow

- DC auxilliary carry/borrow

- Z zero

• PIC16F8x – ALU operations

- PIC16F8x ALU operations

- STATUS register

- Any value can be written

- C, DC, Z auto set

- !TO, !PD non-modificable

- − !TO=0  $\rightarrow$  watchdog overflow

- !PD=0  $\rightarrow$  after sleep command

- IRP RAM bank selection for indirect addressing

- Unused if 2 banks only

- RPO, RP1 RAM bank selection for direct addressing

- RP1 unused if less than 3 banks

- PIC16F8x OPTION\_REG

- !RBPU

- $0 \rightarrow PortB$  pull-up resistors on

- INTEDG

- Rising (1)/falling (0) edge external interrupt signalling

- T0CS

- Clock source for TO: external (1)/internal (0)

- TOSE

- Rising (1)/falling (0) edge active

- PSA

- Prescaler assigned to watchdog (1)/TMR0 (0)

- PS2..0

- Prescaler 1/2 ... 1/256 (TMR0), 1/1 ... 1/128 (watchdog)

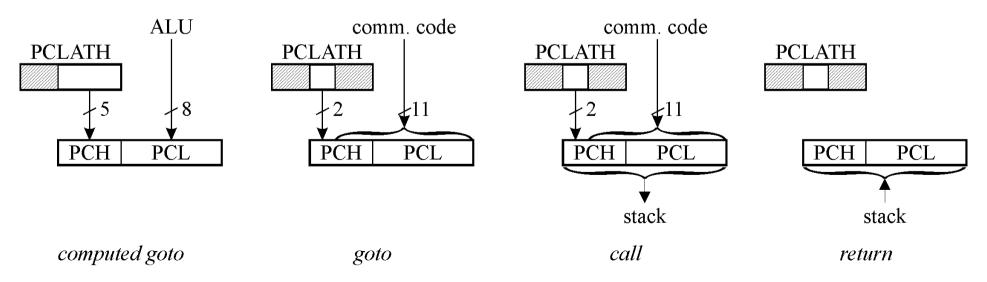

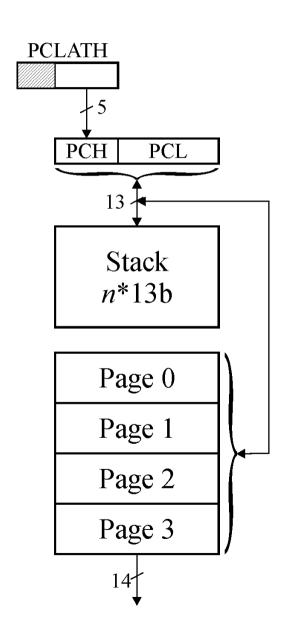

- PIC16F8x program counter (PC)

- PC<sub>0..12</sub>:

- $PCL = PC_{0..7}$

- Can be read or written

- PCH = PC<sub>8..12</sub>

- Can't be directly modified

- PCLATH for modification

- PIC16F8x program memory

- Reset vector: 0000h

- Interrupt vector: 0004h

- Stack: hardware only

- No software access

- No push, pop commands

- No argument passing

- No overflow signalling!

- Max capacity = 8k×14

- Can be less than 8k

- PIC16F8x configuration memory

- Above program memory

- Available only during programming

- Options:

- Oscillator type

- Watchdog on/off

- Power-on delay

- Program/EEPROM read disable

- Can't be read from outside of the  $\mu p$

• PIC16F8x – data memory

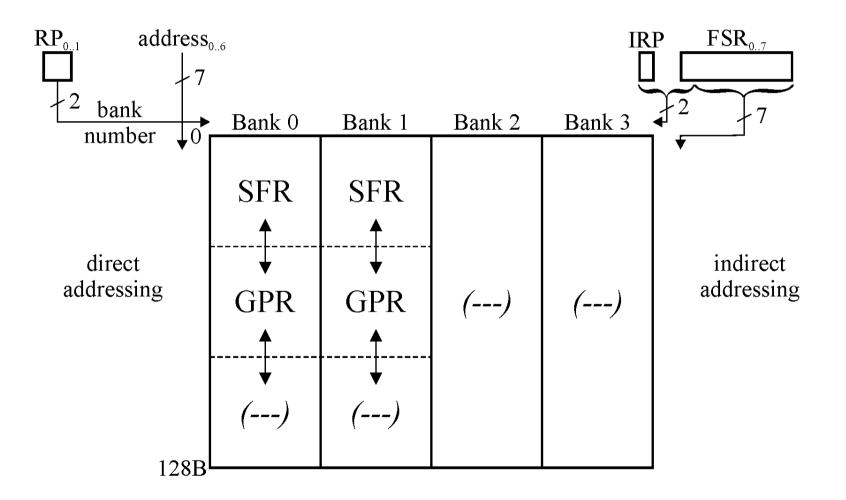

- PIC16F8x data memory

- $-\mu c$ -dependent:

- Capacity, zone borders, banks number

- SFR:

- Key registers

- Mapped in each bank

- Constant address

- Remaining registers

- Mapped in a single bank only

- GPR (bank 1) and GPR (bank 0)

- May map to the same memory cells

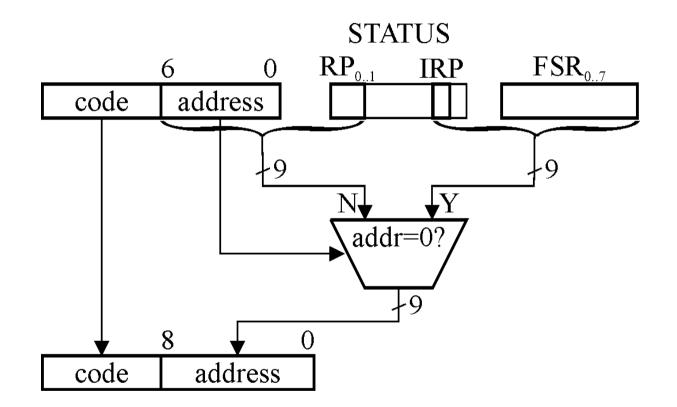

• PIC16F8x – data memory addressing

– Direct INDF access = indirect GPR access

- PIC16F8x data memory addressing

- Indirect addressing

- INDF pseudo-register

- Mapped at address 0 in each bank

- Is not a real register

- Read:

- $\operatorname{addr} \rightarrow \operatorname{IRP.FSR}$

- INDF  $\rightarrow$  data

- Write

- $\text{Addr} \rightarrow \text{IRP.FSR}$

- Data  $\rightarrow$  INDF

- PIC16F8x EEPROM memory

- Only indirect-addressable

- $\ge 10^7$  erase-write cycles

- Registers:

- EEDATA 8-bit data, Rd/Wr

- EEADR 8-bit address

- EECON1 Rd/Wr control

- WR, RD, WREN, WRERR, EEIF, EEPGD

- EECON2 write "magic word"

• PIC16F8x – EEPROM memory

| Read                      | Write                       |

|---------------------------|-----------------------------|

| addr $\rightarrow$ EEADR  | addr $\rightarrow$ EEADR    |

| EEPGD = 0                 | data $\rightarrow$ EEDATA   |

| EECON1.RD = 1             | (EEPGD = 0)                 |

| (∆t = 0)                  | EECON1.WREN = 1             |

| EEDATA $\rightarrow$ data | EECON2 = 55h                |

|                           | EECON2 = AAh                |

|                           | EECON1.WR = 1               |

|                           | (∆t ≈ 10 ms)                |

|                           | EEIF = 1, EECON1.WR cleared |

- PIC16F8x FLASH memory

- Similar to EEPROM, but longer address & data reg.

- Write only to non-secured area

| Read                              | Write                             |  |

|-----------------------------------|-----------------------------------|--|

| addr $\rightarrow$ EEADR, EEADRH  | addr $\rightarrow$ EEADR, EEADRH  |  |

| EEPGD = 1                         | data $\rightarrow$ EEDATA, EEDATH |  |

| EECON1.RD = 1                     | (EEPGD = 1)                       |  |

| nop ∆t for read from              | EECON1.WREN = 1                   |  |

| nop program memory                | EECON2 = 55h                      |  |

| EEDATA, EEDATH $\rightarrow$ data | EECON2 = AAh                      |  |

|                                   | EECON1.WR = 1                     |  |

|                                   | nop <i>µp omits this</i>          |  |

|                                   | nop $\Delta t \approx 10  ms$     |  |

|                                   | EEIF = 1, EECON1.WR cleared       |  |

– Programming from remote µc by "boot-loader"