Rzeczpospolita Polska

Unia Europejska Europejski Fundusz Społeczny

Politechnika Śląska jako Centrum Nowoczesnego Kształcenia opartego o badania i innowacje

POWR.03.05.00-IP.08-00-PZ1/17

Projekt współfinansowany przez Unię Europejską ze środków Europejskiego Funduszu Społecznego

#### **Microprocessor and Embedded Systems**

Faculty of Automatic Control, Electronics and Computer Science, Informatics, Bachelor Degree

#### Lecture 10

# Microprocessor systems development & testing

**B**artłomiej Zieliński, PhD, DSc

Program:

- Problems during µp systems development

- Hardware problems

- Software problems

- I/O problems

- μp systems analysis

- Asynchronous analysis

- Synchronous analysis

- Development tools

- Debuggers, simulators

- Logic state analyzers

- In-circuit emulators

- µp systems

- $\mu p's$  are VLSI

- No internal signals available

$\rightarrow$ Observe bus signals only

- $\mu p$  works according to a program

- Results of both hardware & software

- $\rightarrow$ Data collected from all buses concurrently

- µp systems testing & development

- New methods & tools necessary

- Problems during µp systems development

- Hardware problems

- "cold solder", bad contacts

- $\rightarrow$  Variable, weak or no electric contact

- IC damage or failure

- Bad IC installation on PCB

- Bad contact with IC socket

- Bad PCB project

- $\rightarrow$  crosstalk, interference

- High resistance of Vcc and Gnd paths

- $\rightarrow$  improper logic signals voltage levels

- $\rightarrow$  interference margin decreased

- Problems during µp systems development

- Software problems

- Hardware OK, software OK, together work bad

- Single step operation

- Loops jump to a random place

- "data execution"

- Sometimes works, sometimes not

- *"if something worked and stopped, something must have changed*" (Alex Ragen: *"*A lexicon of C" (?))

- I/O problems

- Wrong transmission rate

- Wrong data format

- Transmission lines interference

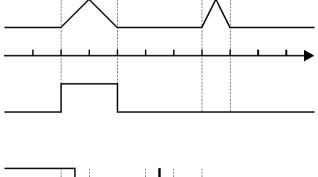

- Synchronous analysis

- Machine cycles storage according to  $\mu p$  clock

- Triggered by a given word

- Only a part of a program is observed/debugged

- Some words preceding trigger must also be stored

- $\rightarrow$  How the µp came to this program fragment?

- Jump / next instruction / malfunction

- Counting a trigger

- When circuit works or not

- Analysis starts with  $n^{th}\,\, pass$

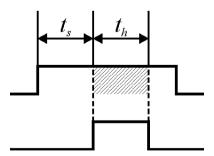

- Synchronous analysis

- Machine cycles storage according to  $\mu p$  clock

- Trigger by a "logic delay"

- Trigger word can't be precisely determined

- » Trigger found ("last known as good")

- » Count *n* cycles

- » Start to register

- Dynamic parameters not always taken into account

- "time set", "time hold"

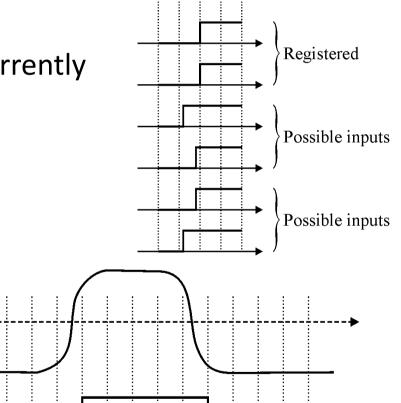

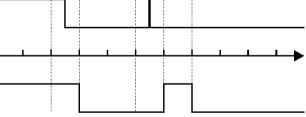

- Asynchronous analysis

- Probing at moments determined by analyser clock

- Very high frequency

- Probing all channels concurrently

- Results may be ambigous

- f≠∞

- Asynchronous analysis

- Glitch detection

- What is a glitch?

- Very short pulse

- Result of: crosstalk, interference, bad Vcc/Gnd

- Cause of: false Int, count errors, data exchange errors...

- How to detect a glitch?

- Very high frequency (e.g. 200 MHz  $\rightarrow$  5 ns glitch)

- » (Glitch < 5 ns not very relevant for  $\mu p$ )

- Latch flip-flops

- » Was there a single glitch, or a sequence?

- Separate signal and glitch registration

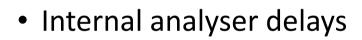

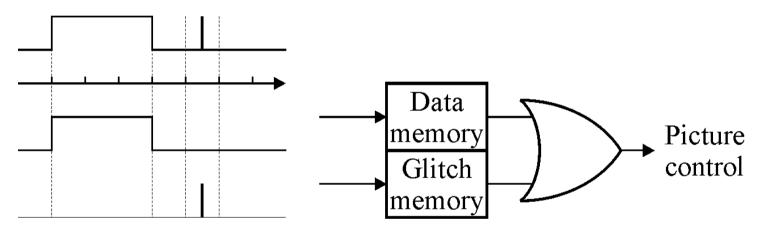

- Asynchronous analysis

- Glitch detection

- Probing method

• With latch registers

Glitch might be omitted by analyser input

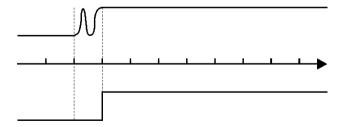

- Asynchronous analysis

- Glitch detection

- Separate data and glitch recording

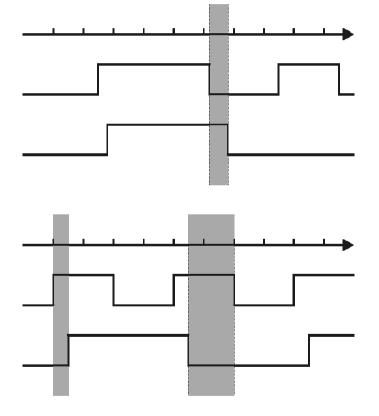

- Asynchronous analysis

- Trigger condition ambiguity in probed signals

- Missed trigger condition (between probes)

False trigger conditions

(e.g., because of different delays)

- Asynchronous analysis

- Trigger condition ambiguity in probed signals

- Time dependencies with regard to clk

- Delay = circuit propagation delay, and trigger pattern comparison only after that

- Recording with some delay after a trigger

- Interesting consequence of a dull ("boring") event

- Glitch-triggered recording

- 1. Recording a single word

- 2. No glitch  $\rightarrow$  goto 1

- 3. Glitch found  $\rightarrow$  record longer

- $\rightarrow$  where/when was a glitch, and what consequences it caused

- Analysis common problems

- Improper power, circuit assembly error

- Wrong voltage levels (e.g. TTL vs CMOS)

- Bad connections

- Analyser shows something different than the  $\mu p$  can see

- Time set/time hold

- etc.

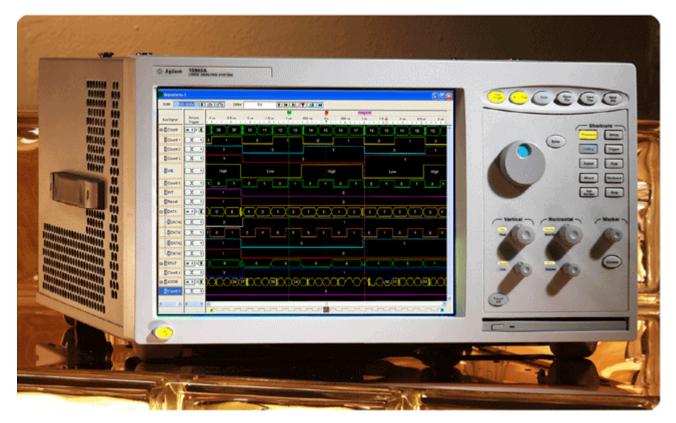

• Logic analyser – example

https://vishnuanirudh.files.wordpress.com/2012/07/logic-analyzer.gif

Logic analyser – example

https://eleshop.eu/sla1016.html

- Logic analyser functions

- Like oscilloscope, but:

- Many inputs (e.g., > 100) concurrently observed

- Digital signals

- Pattern-triggered analysis

- Output:

- Series of "0" and "1"

- Time diagrams for many signals

- Memory access map

- Useful for debugging µp-based systems

- Disassembled program

- Logic analyser summary

- Good for finding both hardware & software errors

- "Observe-only" operation

- Passive recording circuit behaviour

- No active influence on circuit

- We can find errors/mistakes, but we can't fix them

- Other tools could be useful

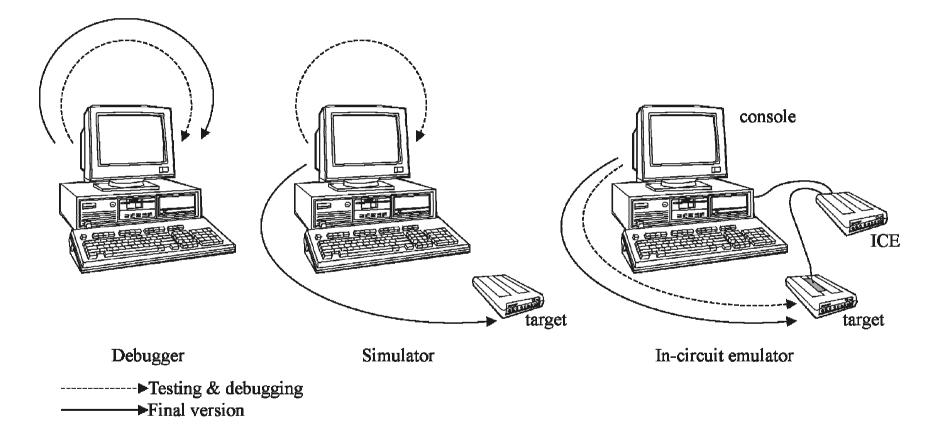

• Debugger / simulator / in-circuit emulator

- Debugger / simulator

- Continuous/single step program execution

- Some simulators can perform "step back"

- Program displayed as assembler code

- Symbolic names possible

- High-level language debugging possible

- Requires compiler/linker information for the debugger

- $-\mu p$  registers content display/modification

- Memory content display/modification

• Turbo Debugger 2.0 example

| - File Edit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | View Run B                                                                                                                                                   | reakroints                                                                                                                                       | Data                                                                                             | Ortions | Window | Help                                                                                            | READY                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------|--------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| C5:023C B8741<br>C5:023F B8741<br>C5:023F B8730<br>C5:0242 BE800<br>C5:0245 AC<br>C5:0246 56<br>C5:0246 56<br>C5:0247 98<br>C5:0248 0BC0<br>C5:0248 0BC0<br>C5:0248 7502<br>C5:0246 50<br>C5:0248 0BC0<br>C5:0248 0BC0<br>C5:0252 0B800<br>C5:0255                                                                                                                                                            | 5 mov<br>0 cal<br>0 mov<br>lod<br>pus<br>cbw<br>or<br>jne<br>jmp<br>8 mov<br>0 cal                                                                           | ax,1574<br>l WriteSt<br>si,0080<br>h si<br>ax,ax<br>024E<br>NoArsFo<br>h ax<br>ax,188D<br>l WriteSt<br>ax,ax                                     | ring<br>rSure (<br>ring                                                                          | 02BF)   |        |                                                                                                 | 1<br>C=0<br>V=0<br>S=0<br>P=0<br>P=0<br>A=0<br>i=1<br>d=0                                                 |

| CS: 025D F3AB<br>CS: 025F 06<br>CS: 0260 B8333<br>CS: 0263 CD21<br>CS: 0263 CD21<br>CS: 0265 8CC0<br>CS: 0267 07<br>CS: 0266 0BC3<br>CS: 0266 7407<br>CS: 0266 7407<br>CS: 0266 CD33<br>CS: 0270 40<br>CS: 0271 7405<br>CS: 0273 800E6<br>ChkArs<br>CS: 0278 59<br>CS: 0278 59<br>CS: 0278 F9<br>CS: 0278 F9<br>CS: 0278 F9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | rep<br>pus<br>5 mov<br>int<br>mov<br>pop<br>or<br>je<br>xor<br>int<br>inc<br>je<br>D0008 or<br>Pop<br>cld<br>jcx                                             | stosw<br>h es                                                                                                                                    |                                                                                                  | 1,08    |        | ss:0038                                                                                         | FFFF<br>49018<br>00014<br>213855<br>FFFFF<br>48FFFF<br>FFFFF<br>FFFFF<br>FFFFF<br>FFFFF<br>FFFFF<br>FFFFF |

| ds:1574 0D 0A<br>ds:157C 6F 72<br>ds:1584 30 2D<br>ds:1584 30 2D<br>ds:1584 69 6C<br>ds:1594 69 6C<br>ds:1594 69 6C<br>ds:1594 20 42<br>ds:15A4 70 79<br>ds:15A4 70 79<br>ds:15A4 2C 20<br>ds:15B4 2C 20<br>ds | 43 6F 6D 43<br>655 499 20<br>699 69 499 20<br>699 749 20<br>699 749 20<br>572 699 67 68<br>729 20 30<br>729 20<br>320 30 338<br>220 33 22E 32<br>55 73 61 67 | 20 31 ore P<br>47 65 0-III<br>55 74 meral<br>62 79 ility<br>43 6F BZik<br>74 20 ryrig<br>39 32 (C) 1<br>20 76 , 200<br>0D 0A er 3.<br>65 3A DUsa | C 1<br>Ge<br>Ut<br>Co<br>ht<br>992<br>992<br>992<br>992<br>992<br>992<br>992<br>992<br>992<br>99 |         |        | ss 0010<br>ss 000E<br>ss 000C<br>ss 000A<br>ss 0008<br>ss 0006<br>ss 0004<br>ss 0002<br>ss FFFE | 0000                                                                                                      |

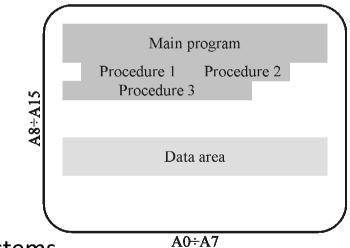

- Simulator vs debugger

- Simulator works in a "virtual" environment

- Commands  $\rightarrow$  procedures

- Registers  $\rightarrow$  variables

- Target system memories  $\rightarrow$  arrays, tables

- Target system I/O  $\rightarrow$  records + procedures

- Address ranges for Mem & IO must be defined

- Real-time simulation requires:

- Detailed knowledge of µp cycles (command cycles, machine cycles, clock cycles)

- Significantly higher computing power (e.g., Pentium II @ 300 MHz can simulate 8051 @ 12 MHz)

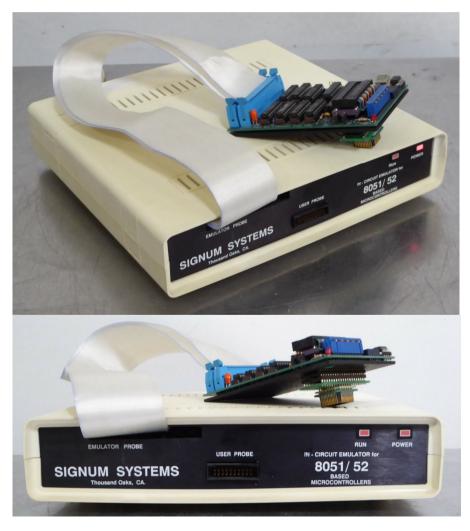

• In-circuit emulator – example

– Signum Systems ICE-51

- In-circuit emulator

- User can "see" the target circuit exactly as the μp does

- Memory types and addresses

- I/O interfaces

- External environment

- All imperfections can be found

- Logic design errors (i.e., wrong address decoding)

- PCB design/production error

- Circuit assembly mistakes

- Hardware/software integration problems

- Pure software problems

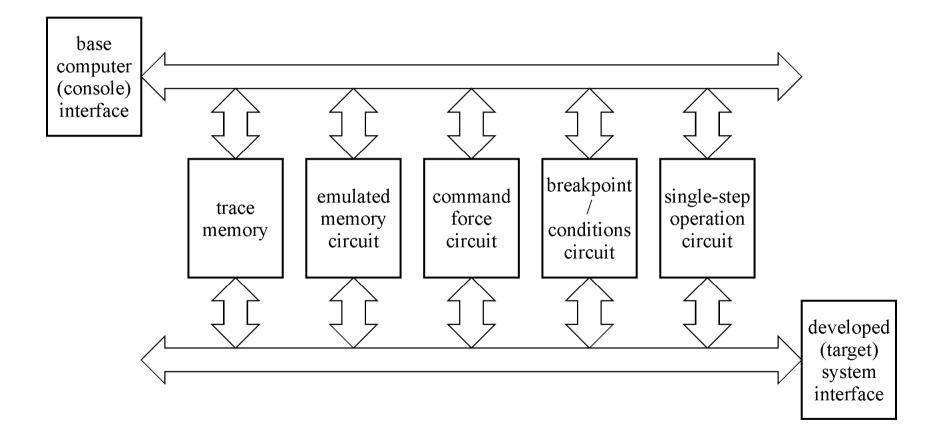

• In-circuit emulator – example structure

- In-circuit emulator example structure

- Single-step circuit

- Modes

- Continuous mode

- Stop at the nearest command

- » For software testing/debugging

- Stop at the nearest machine cycle

- » For hardware testing/debugging

- How to implement?

- Classical μp (e.g., Z80, 8086, etc.) machine cycle extension input (e.g., Wait, Ready etc.)

- Single chip /  $\mu$ c must have the support built-in (e.g., 8048 has  $\overline{SS}$  input, 8051 no built-in support)

- In-circuit emulator example structure

- Breakpoint circuit

- Simple

- Address and/or data equal to a given value

- Specified machine cycle occured

- (not so) simple

- Address and/or data matches the pattern

- » Only selected bits are compared

- Conjunction of simple conditions

- In-circuit emulator example structure

- Breakpoint circuit

- Complex (e.g., Signum Systems ICE-51)

- Events

- » Selected machine cycle (+adress, data pattern match)

- » User signals

- » Event count

- » Event sequence

- » Trace memory full

- Effects

- » Breakpoint

- » Event counter start/stop

- » Trace end

- In-circuit emulator example structure

- Command force circuit

- To make the µp perform a command/procedure that is absent from the program memory

- ... but why do we need it?

- To quickly fix a bug without need to recompile the program

- To perform a diagnostic procedure

- » E.g., store register content outside of the μp after breakpoint occured

- » Update µp state window

- To quickly test some actions before they are implemented in software/in system

- In-circuit emulator example structure

- Emulated memory circuit

- Replaces/completes system RAM/ROM

- Contains RAM only

- Higher priority than system memory

- » "hides"/works instead of the system memory

- Content can be modified easily

- » Especially when system memory is ROM/PROM/EEPROM

- Address ranges user-definable

- What about I/O interfaces?

- In-circuit emulator example structure

- Trace memory circuit

- Stores the execution trace

- All the machine cycles found on the  $\mu p$  pins

- User signals can also be traced

- Presented as a program flow with decoded commands, data, I/O signals, etc.

- Like logic analysers (synchronous analysis)

- JTAG modern methods

- Joint Test Action Group (1985)

- IEEE Std. 1149 (1990)

- Early applications

- device, board & system testing & diagnosis

- Modern applications

- Access of IC sub-blocks

- Debugging of embedded systems

- Firmware programming

- Boundary scan

- JTAG interface

- Another built-in interface in a  $\mu p/\mu c$

- "full" JTAG

- TDI (Test Data In)

- TDO (Test Data Out)

- TCK (Test Clock)

- TMS (Test Mode Select)

- TRST (*Test Reset*, optional)

- "compact" JTAG cJTAG

- TMSC (Test Serial Data)

- TCKC (*Test Clock*)