Rzeczpospolita Polska

Unia Europejska Europejski Fundusz Społeczny

Politechnika Śląska jako Centrum Nowoczesnego Kształcenia opartego o badania i innowacje

POWR.03.05.00-IP.08-00-PZ1/17

Projekt współfinansowany przez Unię Europejską ze środków Europejskiego Funduszu Społecznego

#### **Microprocessor and Embedded Systems**

Faculty of Automatic Control, Electronics and Computer Science, Informatics, Bachelor Degree

#### Lecture 7

#### **Interrupt controllers**

**B**artłomiej Zieliński, PhD, DSc

Program:

- Interrupt controller functions

- Interrupt controllers:

- Simple: 8214

- Complex, flexible, programmable: 8259(A)

- Interrupt controller functions

- Interrupt source recognition

- Priority control

- Interrupt mask control

- Informing the  $\mu p$  what to do

- Possible implementations

- Separate IC (e.g., Intel)

- "Distributed interrupt controller" (e.g., Zilog)

- Lower cost (?), better scalability

- Intel 8214

- Simple interrupt controller

- or maybe a complex priority encoder?

- (almost) programmable

- Constant (hierarchical) priority system

- No individual masking

- Configurable mask level

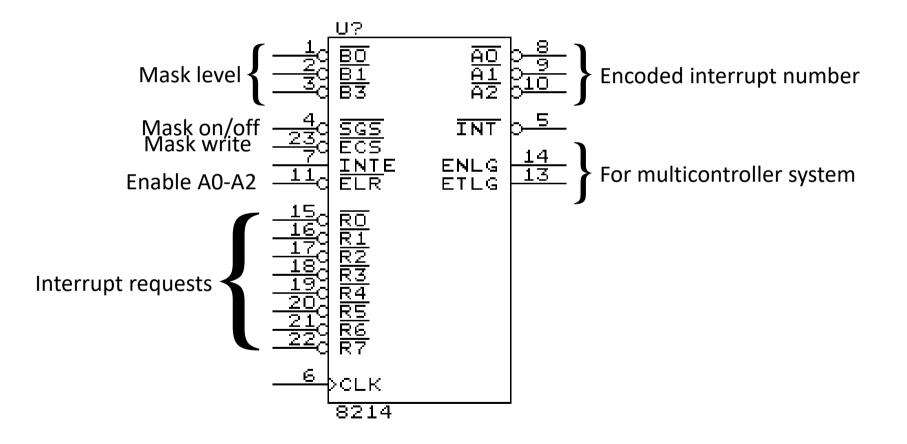

• Intel 8214 circuit pins

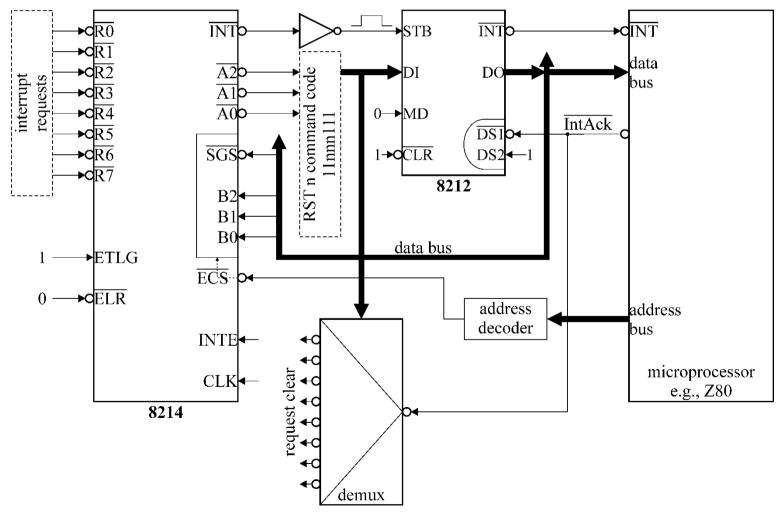

• Intel 8214 application

- For Z80 & similar microprocessors

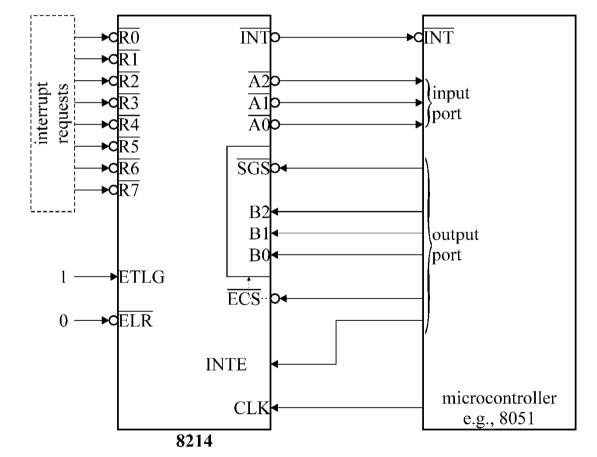

- Intel 8214 application

- For 8051 & similar microcontrollers

- Intel 8214 disadvantages

- Request signal active until interrupt service

- Otherwise µp may miss the request

- Request signal must be software cleared

- Otherwise µp will think it's the next request

- No information about interrupt service procedure placement

- Only interrupt ID is given

- On the other hand, it's like it's done nowadays

- ... but it's a simple controller anyway...

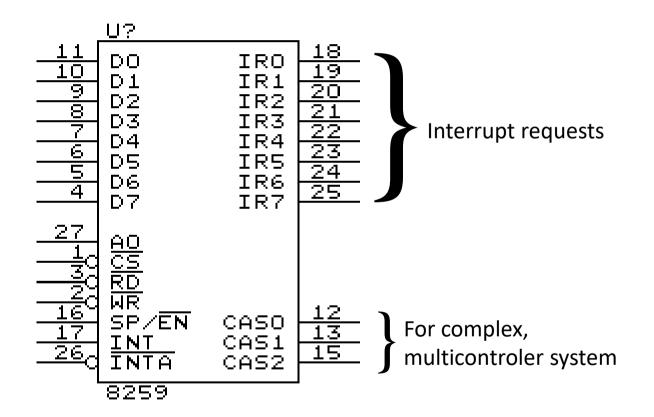

• Intel 8259 circuit pins

- Intel 8259A properties

- Up to 8 fully hardware-recognised interrupts

- Individual masking

- Few priority assignment methods

- Hierarchical (static)

- Rotating priority (dynamic)

- Special masking

- Polling mode

- Few End-of-Interrupt possibilities

- Complex system in cascade (Master/Slave) configuration

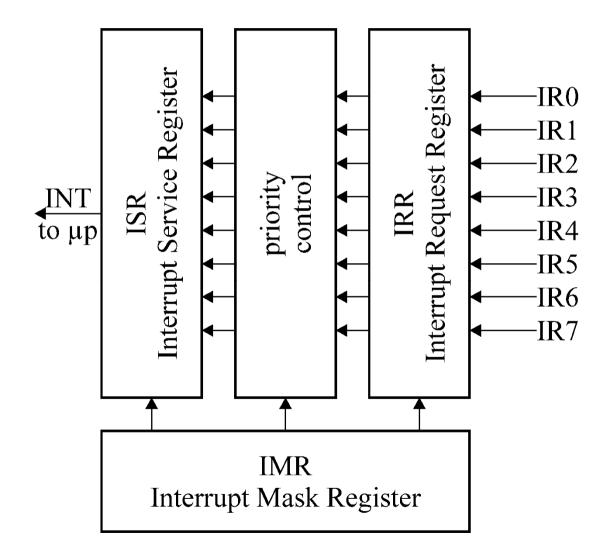

• Intel 8259A structure

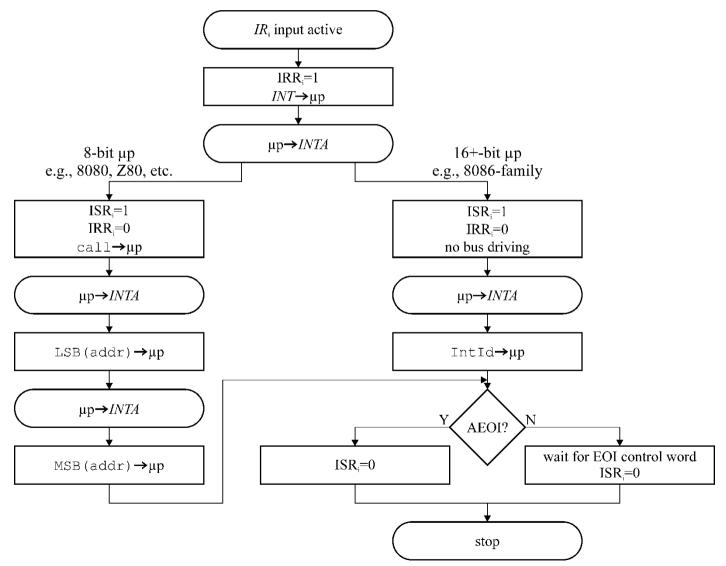

• Intel 8259A interrupt processing

- Intel 8259A priority modes (1)

- Fully Nested Mode

- Static assignment: IRO highest ... IR7 lowest priority

- Level N being served  $\rightarrow$  levels  $\geq N$  auto masked

- Special Fully Nested Mode

- Similar to Fully Nested Mode

- Level N being served  $\rightarrow$  levels >N auto masked

- Level N <u>not</u> masked

- Useful for Master in a cascade system

- Allows to accept interrupt from currently served Slave

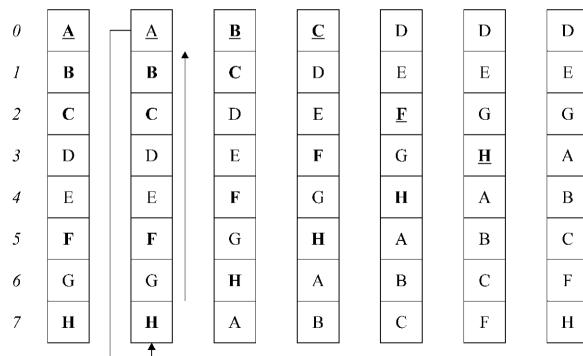

- Intel 8259A priority modes (2)

- Rotating Priority Mode

- Dynamic assignment

- Interrupt just served is "rewarded" with the lowest priority

- Remaining interrupts go one level higher in the hierarchy

- Intel 8259A priority modes (3)

- Special Masking Mode

- Can accept interrupts of a lower priority than currently being served

- Polled Mode

- INT line not used

- Interrupts status software returned by a command

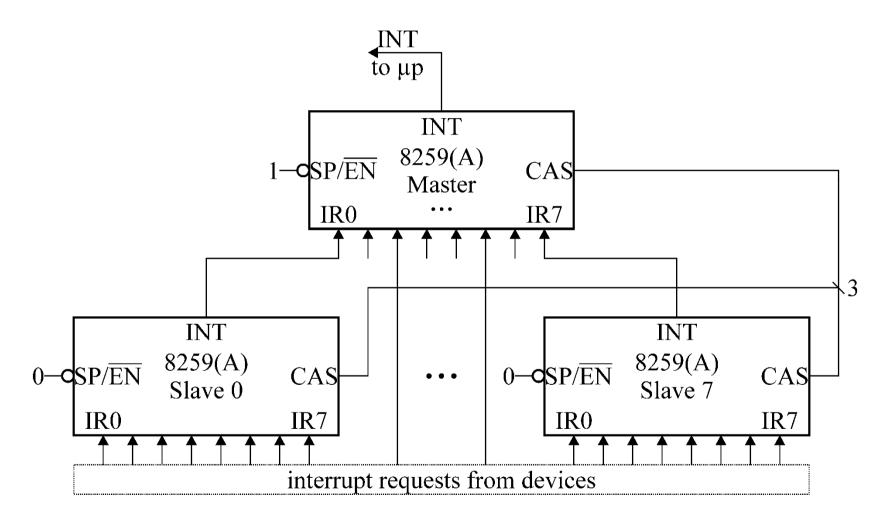

- Intel 8259A complex system

- Up to 1 Master and 8 Slave circuits

- Up to 64 fully hardware-recognised interrupts

- Master: a bitmap tells where slaves are connected

- Slaves: must know the Master IR input

- CAS bus: during IntAck, selects a Slave to complete the cycle

- IntID sent from:

- Selected Slave, if request went through slave

- Master, if request went directly to the master

- IBM PC/AT: 1 Master, 1 Slave, 15 interrupts

• Intel 8259A cascade system

- Intel 8259A programming

- Initialisation command words

- ICW1 general options

- ICW2 higher part of address/interrupt ID

- ICW3 for cascade systems

- ICW4 additional options (8259A)

- Operation command words

- OCW1 mask control

- OCW2 EOI, priority rotation

- OCW3 register read, special mask mode

- Intel 8259A programming

- Initialisation sequence

A0 D7 D5 D4 D3 D2 D0 D6 D1 Sngl ICW4 ICW1 LTIM ADI 0 A7 A6 A5 1 ICW2 A13 A12 A15 A14 A11 A10 A9 A8 if Sngl=1 S2/ **S**1/ S0/ ICW3 **S**3 **S**7 S5 **S6 S**4 ID2 ID1 ID0 if ICW4=1 SF ICW4 0 0 Buf M/S AEOI 0 μp NM

- Intel 8259A programming

- ICW1, ICW2

|      | D7  | D6  | D5  | D4  | D3   | D2  | D1   | D0   |

|------|-----|-----|-----|-----|------|-----|------|------|

| ICW1 | A7  | A6  | A5  | 1   | LTIM | ADI | Sngl | ICW4 |

| ICW2 | A15 | A14 | A13 | A12 | A11  | A10 | A9   | A8   |

- ICW4 ICW4 present

- Sngl single/multi controller interrupt system (ICW3!)

- ADI 4 or 8 bytes between iterrupt service procedures

- LTIM IR inputs edge or level sensitive

- A15-A5 higher adress bits of interrupt service procedures (for 8-b μp)

- A15-A11 common IntID part (for 16-b μp)

- A10-A8 = INT input number

- Intel 8259A programming

- ICW3, ICW4

|      | D7         | D6         | D5         | D4       | D3  | D2         | D1         | D0         |

|------|------------|------------|------------|----------|-----|------------|------------|------------|

| ICW3 | <b>S</b> 7 | <b>S</b> 6 | <b>S</b> 5 | S4       | S3  | S2/<br>ID2 | S1/<br>ID1 | S0/<br>ID0 |

| ICW4 | 0          | 0          | 0          | SF<br>NM | Buf | M/S        | AEOI       | μp         |

- S7-S0 (Master) slave connection bitmap

- ID3-ID0 (Slaves) master INT number

- AEOI Automatic End Of Interrupt

- M/S Master/Slave (in Buffered mode)

- Buf Buffered mode

- SFNM Special Fully Nested Mode

- μp μp type: 8-bit (8080/8085) / 16-bit (8086)

- Intel 8259A programming

- OCW1:

- M7-M0 mask bits

- OCW2:

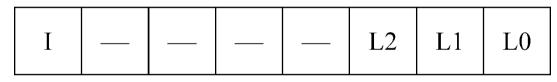

- A0 D7 D6 D5 D4 D3 D2 D1 D0 OCW1 M5 M7 M6 M4 M3 M2 M1 M0OCW2 = 0SL EOI L2 R 0 0 L1 LO OCW3 0 0 0 Р RR RIS 1

- R, SL, EOI EOI commands, priority rotation

- L2-L0 interrupt number for EOI/rotation

- OCW3:

- RR, RIS read IRR or ISR on the nearest  $\overline{\text{RD}}$

- P poll command

- SMM, ESMM set or reset Special Mask Mode

- Intel 8259A programming

- EOI types

- Non-specific EOI: reset the highest ISR active bit

- Specific EOI: reset the ISR bit specified by L2-L0

- When not in Fully Nested Mode

- AEOI: non-specific EOI automatically performed

- Priority rotation:

- Non-specific EOI + priority rotation

- Specific EOI + priority rotation

- Set/clear rotation on AEOI

- Specific rotation only

- Intel 8259A programming

- Poll mode

- Send OCW3 with P=1

- On the nearest  $\overline{\text{RD}}$ , status is given as follows:

- L2-L0 highest priority level requesting interrupt

- I if any interrupt is active

- Buffered mode

- $SP/\overline{EN}$  used to control external buffer

- Master/Slave selection software-set only

- Intel 8259A programming

- Word/register addressing summary

| <b>A0</b> | D4 | D3 | RD | WR | action                         |

|-----------|----|----|----|----|--------------------------------|

| 0         |    |    | 0  | 1  | Read IRR or ISR                |

| 1         |    |    | 0  | 1  | Read IMR                       |

| 0         | 0  | 0  | 1  | 0  | Write OCW2                     |

| 0         | 0  | 1  | 1  | 0  | Write OCW3                     |

| 0         | 1  | *  | 1  | 0  | Write ICW1                     |

| 1         | *  | *  | 1  | 0  | Write ICW2, ICW3, ICW4 or OCW1 |

|           |    |    |    |    |                                |