Rzeczpospolita Polska

Unia Europejska Europejski Fundusz Społeczny

Politechnika Śląska jako Centrum Nowoczesnego Kształcenia opartego o badania i innowacje

POWR.03.05.00-IP.08-00-PZ1/17

Projekt współfinansowany przez Unię Europejską ze środków Europejskiego Funduszu Społecznego

#### **Microprocessor and Embedded Systems**

Faculty of Automatic Control, Electronics and Computer Science, Informatics, Bachelor Degree

#### Lecture 5

#### Parallel input/output circuits

**B**artłomiej Zieliński, PhD, DSc

Program:

- General IO circuit properties

- Simple paralel IO with acknowledge

- 8212 circuit

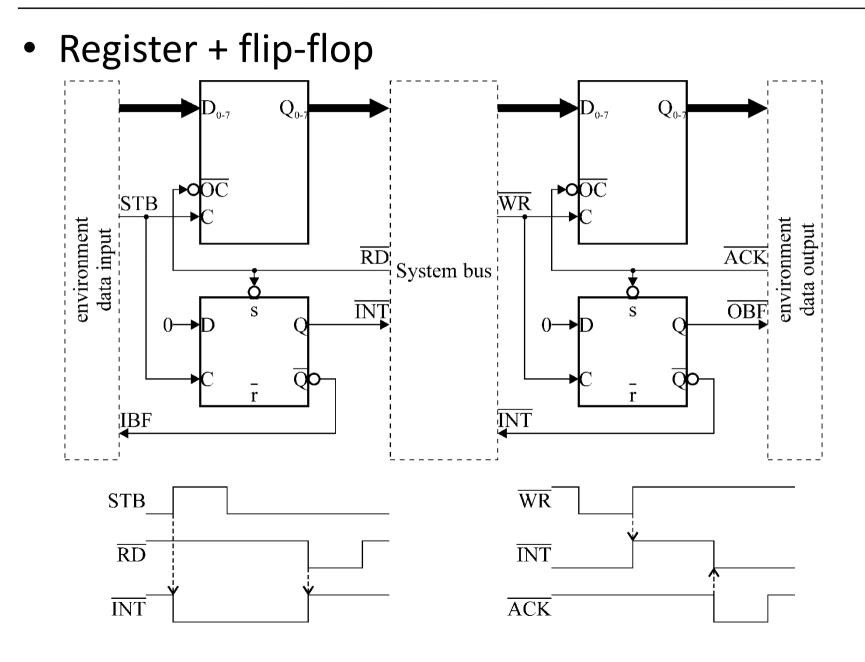

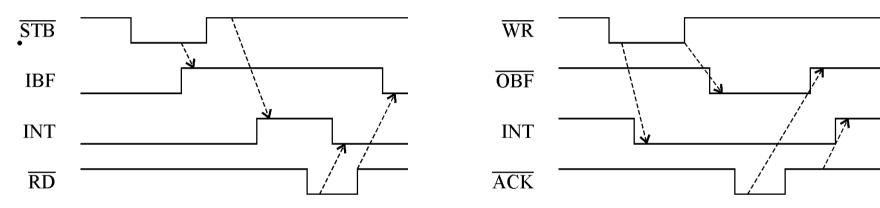

- Register + flip-flop

- Programmable paralel IO circuits

- Intel 8255

- Zilog Z80 PIO

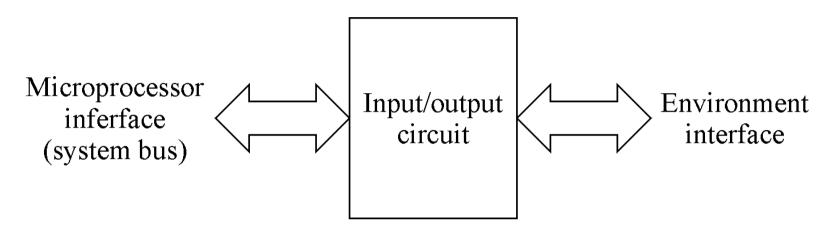

• General concept & properties

- Microprocessor interface

- Simple works with every  $\mu p$

- Dedicated (optimised) highly µp-dependent

- Environment interface

- Highly function-dependent

- Similar or compatible across various circuits

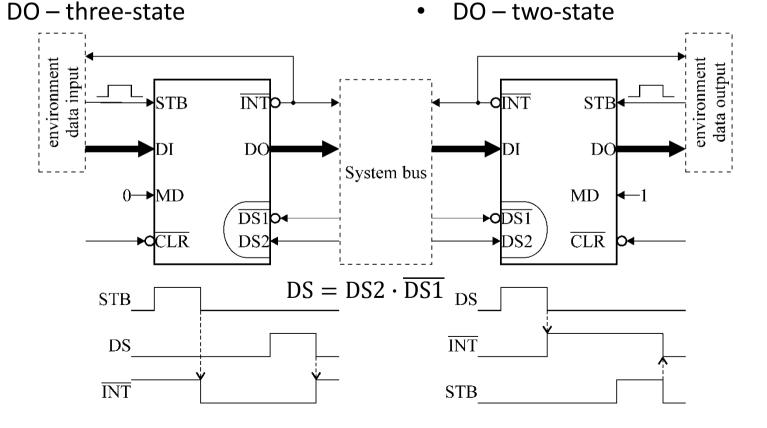

• 8212 circuit

•

- 8-bit universal I/O register with status signals

- Parallel input with data ready signal

• Parallel output with data request signal

- Intel 8255 circuit

- Programmable parallel I/O circuit

- 3 bi-directional, 8-bit I/O ports

- Port A bi-directional

- Port B input or output

- Port C input or output, control signals for A and B

- 3 modes

- Input or output without acknowledge (A, B, CL, CH)

- Input or output with acknowledge (A, B)

- Bi-directional with acknowledge (A)

• 8255 pins

| 34<br>33<br>32<br>31<br>30<br>29<br>28<br>27 | D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 |                                                                                                         | PA0<br>PA1<br>PA2<br>PA3<br>PA4<br>PA5<br>PA5<br>PA6<br>PA7 | 4<br>2<br>40<br>39<br>38<br>37                     |

|----------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------|

| 1 190 0 10 00 00 00 00 00 00 00 00 00 00 00  | AO<br>A1<br>CS<br><u>RD</u><br>WR            |                                                                                                         | PB0<br>PB1<br>PB2<br>PB3<br>PB4<br>PB5<br>PB6<br>PB7        | 18<br>19<br>20<br>21<br>22<br>23<br>23<br>24<br>25 |

| _35                                          | RES<br><u>IBFB</u> ,<br>STBB,                | <u>IRQB</u><br>( <u>ACKB</u> )<br>(0BFB)<br><u>IRQA</u><br>STBA<br><u>STBA</u><br><u>IBFA</u><br>(0BFA) | /PC1<br>/PC2<br>/PC3<br>/PC4<br>/PC5<br>/PC6                | 14<br>15<br>16<br>17<br>13<br>12<br>11<br>10       |

8255

- 8255 port modes

- Mode 0

- No acknowledge

- Transmission direction set for PA, PB, PCL, PCH

- Output data stored in a register

- Input data NOT stored, read directly from the pins

- Mode 1

- Acknowledge ("hand shake")

- Transmission direction set for PA, PB

- PC control signals for PA and PB

- Output data stored in a register

- Input data also stored in a register

• 8255 port modes

– Mode 1 (cont'd)

– Mode 2

- Similar to Mode 1

- Works only for PA

- Control signals as in Mode 1

- Input and output data stored in two separate registers

- 8255 port modes interrupts

- Mode 0

- No built-in interrupt mechanism

- External circuit can be used

- Mode 1 interrupts

- Hardware signal (INT)

- Software read of PC (polling)

- Mode 2 interrupts

- As in Mode 1

- Common INT line for both directions

- Requested, when INTE=1

- Modify INTE  $\rightarrow$  set/reset PC<sub>3</sub> (INTE<sub>A</sub>) or PC<sub>0</sub> (INTE<sub>B</sub>)

• 8255 registers

| A <sub>1</sub> A <sub>0</sub> | 00 | 01 | 10 | 11      |

|-------------------------------|----|----|----|---------|

| Register                      | PA | PB | PC | Control |

#### – Control register

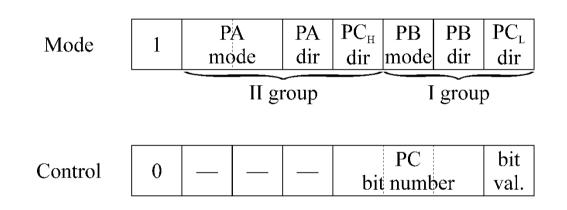

• Mode

| Bit | Function      |

|-----|---------------|

| 7   | 1             |

| 6-5 | PA mode       |

| 4   | PA direction  |

| 3   | PCH direction |

| 2   | PB mode       |

| 1   | PB direction  |

| 0   | PCL direction |

#### PC control

- Bit Function

- 7 0

6-4 -

- 3-1 PC bit numer

- 0 PC bit value

$$PC_{R_{1..3}} = R_0$$

• 8255 control register

#### - (write only)

- Direction bits:

- 1=1nput

- 0=0utput

- 8255 reset

- All ports set as Mode 0, input

- To avoid outputs conflicts

- Port lines in high-impedance state

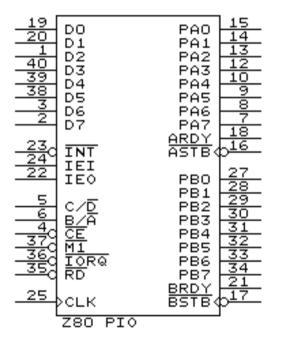

- Zilog Z80 PIO circuit

- Programmable parallel I/O circuit

- 2 bi-directional, 8-bit I/O ports

- Port A bi-directional

- Port B input or output

- 4 modes

- Input with acknowledge (PA, PB)

- Output with acknowledge (PA, PB)

- Bi-directional with acknowledge (PA only)

- PB limited to bit mode

- Bit (PA, PB)

• Z80 PIO pins

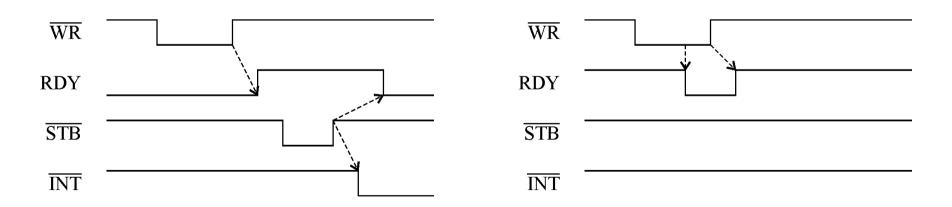

- Z80 PIO port modes

- Mode 0

- Output with optional acknowledge

- Works with PA and PB independently

- Output data stored in a register

- After data write, RDY  $0 \rightarrow 1$

- Z80 PIO port modes

- Mode 1

- Input with optional acknowledge

- Works with PA and PB independently

- Input data may be stored in a register

- After data read, RDY  $0 \rightarrow 1$

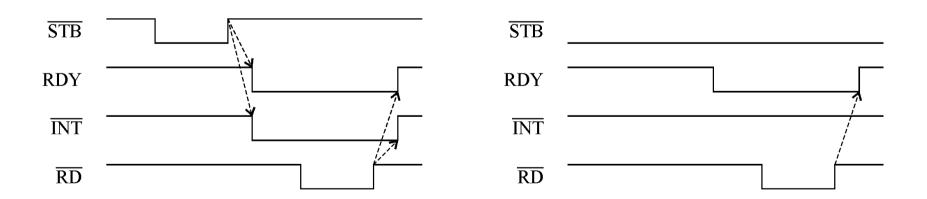

- Z80 PIO port modes

- Mode 2

- Bi-directional with acknowledge

- Works with PA only (PB only in bit mode)

- Data stored in separate registers

- After data read/write, RDY  $0 \rightarrow 1$

- ARDY/ASTB output, BRDY/BSTB input

- Z80 PIO port modes

- Mode 3

- Bit mode

- Works with PA or PB independently

- Each bit set as I or O

- RDY=0

- Automatic control function

- Selected bits

- Selected function (OR, AND)

- Selected value (0, 1)

- When fulfilled  $\rightarrow$  interrupt

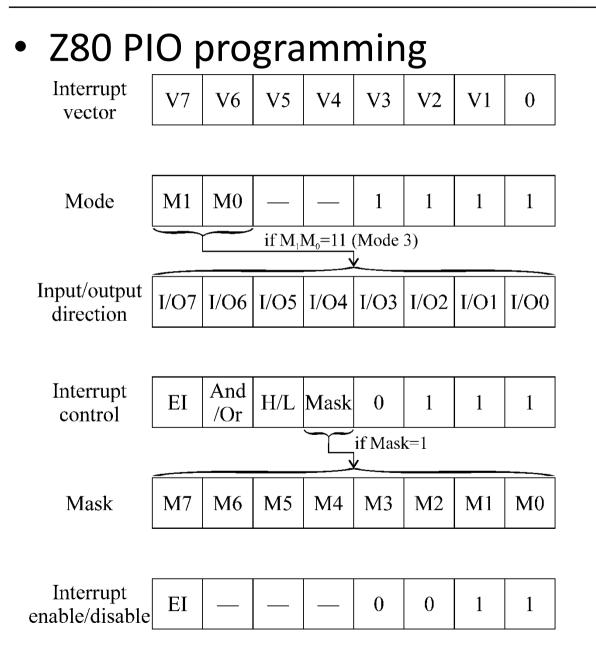

- Z80 PIO programming

- Registers (for each port separately)

- Data input (8-b)

- Data output (8-b)

- Mode (2-b)

- Mask (8-b)

- I/O direction (8-b)

- Interrupt vector (8-b)

- Mask control (2-b)

- Z80 PIO programming

- Interrupt vector ( $D_0=0$ ,  $D_{1-7}=vector$ )

- Mode (D<sub>0-3</sub>=1, D<sub>6-7</sub>=mode)

- If mode=3, next byte sets I/O direction (1=out, 0-in)

- Interrupt control ( $D_{0-2}=1$ ,  $D_3=0$ ,  $D_7=1/0$ enable/disable)

- If mode=3, D<sub>6</sub>=AND/OR, D<sub>5</sub>=1/0, D<sub>4</sub>=mask on/off

- If D<sub>4</sub> was 1, next byte is mask

- Interrupt enable/disable (D<sub>0-1</sub>=1, D<sub>2-3</sub>=0, D<sub>7</sub>=1/0 enable/disable)

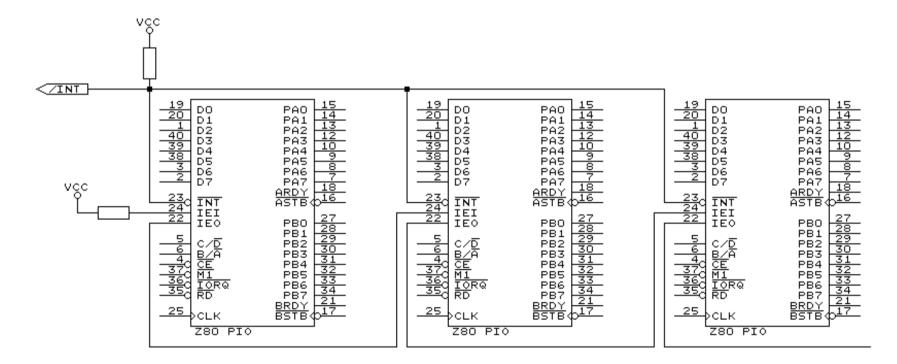

- Z80 PIO interrupts

- PA higher priority

- Mode 0, 1, 2 requested when  $\overline{\text{STB}}=0\rightarrow 1$

- Mode 3 requested when programmed conditions are fulfilled

- Interrupt accepted  $\rightarrow$  interrupt vector sent to  $\mu p$

- RETI command decoding

- Z80 PIO interrupts

- IEI, IEO, INT lines

- "daisy-chain" priority

- Z80 PIO reset

- All ports set as Mode 1, input

- To avoid outputs conflicts

- PA, PB high impedance

- ARDY=BRDY=0 (inactive)

- Interrupts disable

- PA and PB output registers=0

- Mask registers=0

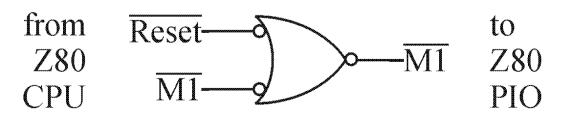

- No Reset input (!)

More information about Z80 family http://z80.info/