Rzeczpospolita Polska

Unia Europejska Europejski Fundusz Społeczny

Politechnika Śląska jako Centrum Nowoczesnego Kształcenia opartego o badania i innowacje

POWR.03.05.00-IP.08-00-PZ1/17

Projekt współfinansowany przez Unię Europejską ze środków Europejskiego Funduszu Społecznego

#### **Microprocessor and Embedded Systems**

Faculty of Automatic Control, Electronics and Computer Science, Informatics, Bachelor Degree

#### Lecture 2

#### Microprocessor and environment data exchange Z-80 microprocessor

Bartłomiej Zieliński, PhD, DSc

Program:

(last week)

- Elements of a microprocessor system

- Fundamental microprocessor structure

- Microprocessor operation cycles

- Basic addressing modes (today)

- Data exchange between a microprocessor and its environment

- Z-80 microprocessor

- Microprocessor system environment

- Office

- Keyboard, mouse, display (monitor), computer network, printer, scanner, ploter, pendrive, portable hard disk....

- But also built-in hard disk

- Measurement and control

- Controlled object

- Digital inputs, analogue inputs (A/D converters), pulse inputs, bi-state inputs, etc.

- Digital outputs, analogue outputs (D/A converters), pulse outputs (e.g., PWM), bi-state outputs, etc.

- External devices connect via I/O interfaces

- I/O interfaces:

- **Simple IO**: output registers, input buffers, no status information, for "always ready" devices

- Universal programmable IO: higher integration IC's, programmable operation modes, status information present

- **Dedicated controllers**: for high-complexity devices that require specialized control (HDD, monitor, network...)

- **IO coprocessors** (e.g., modern graphic adapters?)

- I/O interface selected with address

#### Memory addressing space

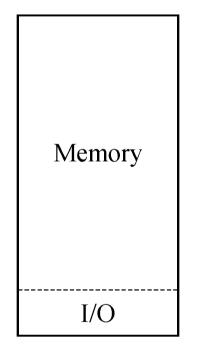

Memory-mapped IO

#### Memory-mapped IO

- Occuppies part of the memory addressing space

- The same commands

- The same addressing modes

- Works with every microprocessor

- Less memory

- More complex address decoding

- (!) less stability

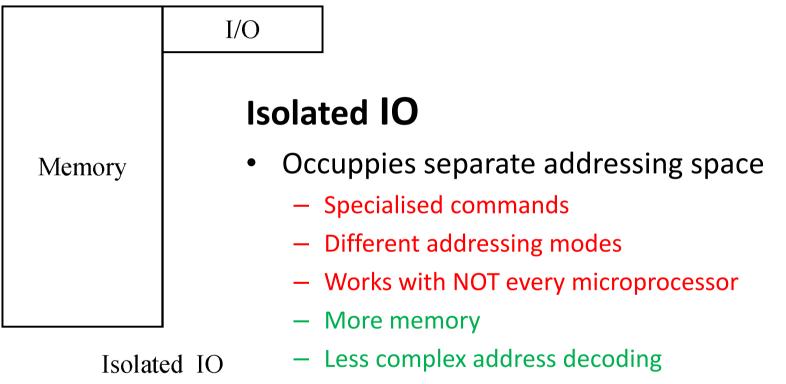

Memory IO addressing space addressing space

- (!) more stability

- Data exchange methods

- Polling

- Cyclic software read of all status registers

- Interrupts

- Requested by the ready devices

- Hardware/software identification

- Single level/multi-level

- Hierarchical/round-robin priorities

- Maskable/non-maskable interrupts (NMI)

- Direct memory access (DMA)

- Bus controlled by a DMA controller, not a microprocessor

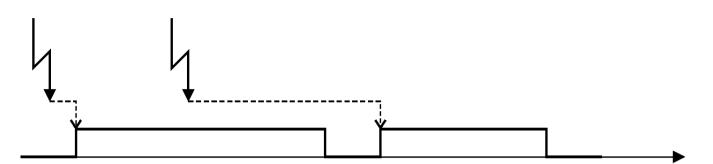

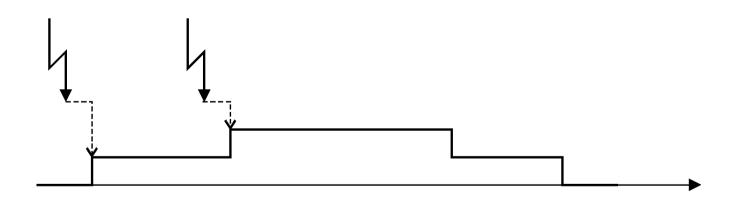

• Single level vs multi-level interrupt system

- Basic properties

- Single power voltage

- 16 adress lines, 8 data lines

- Clock 2.5 to 10 MHz (currently up to 20 MHz)

- Single power voltage

- 158 commands + undocumented command list

- Two interchangeable register sets

- 2 interrupt inputs, 3 interrupt modes

- DRAM refresh

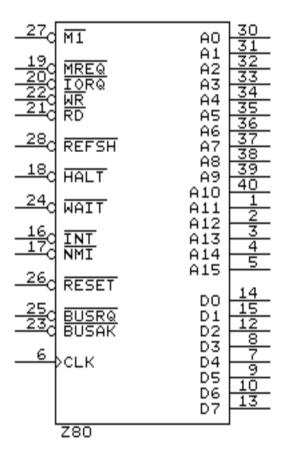

• Pinout

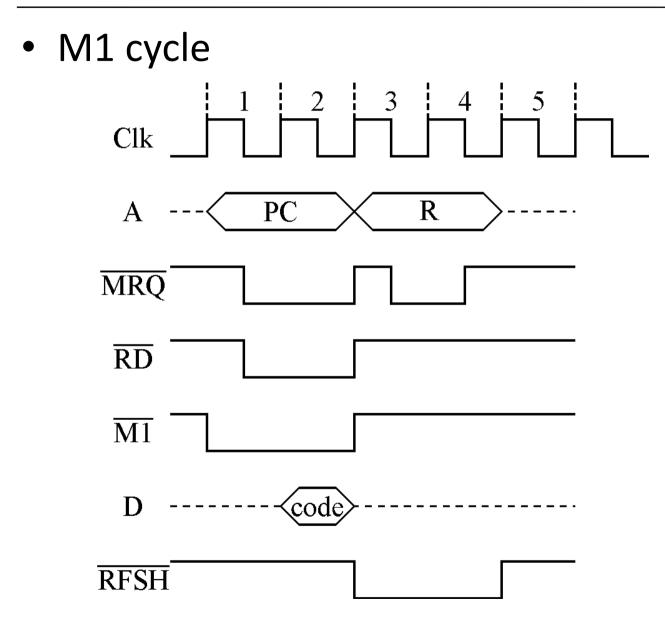

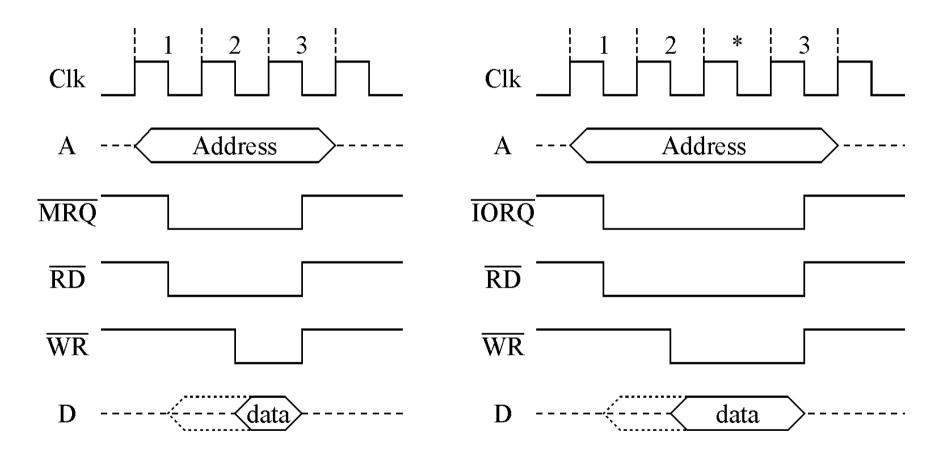

Mem/IO Rd/Wr cycles

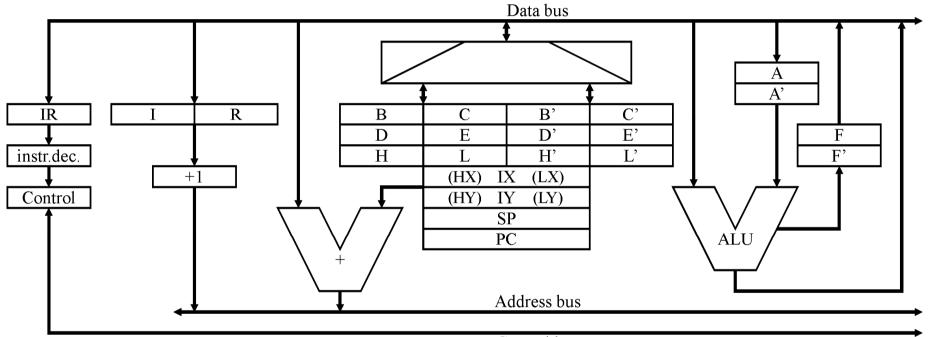

• Simplified structure

Control bus

- Registers:

- A accummulator

- F flags

- BC, DE, HL joined 8-bit registers, unequally used

- H, L traditional name from 8080 μp

- HL jump commands, 16-b accummulator

- BC counter, IO address

- IX, IY index registers

- Flags:

- C carry/borrow (also in shift and rotation)

- -Z zero (result = 0)

- $-S sign (A_7 bit)$

- P/V parity/overflow

- After logical command 1, if even numer of 1's in A

- After arithmetical command 1, if overflow

- H half carry/borrow from A<sub>3</sub>

- used for decimal correction

- N substract (1 immediately after substraction)

- used for decimal correction

- Commands:

- 1B or 2B data transfer

- Exchange

- Arithmetical/logical 1B, arithmetical 2B

- Shift, rotation

- Data block (string)

- Single bit

- Jump, procedure call, return

- Microprocessor control

- i/o

- Addressing modes

- Implied, e.g. CPL; LD SP, IY; SUB 10 (A=A-10)

- Immediate: ADD A, n; XOR n; LD IXL, n

- Extended immediate: LD HL, nn; JP nn

- Register: RL r; AND r

- Register indirect: LD A, (BC); INC (HL)

- Extended (direct): LD A, (nn); LD (nn), HL

- Modified page zero: RST p

- Relative: JR Z, d

- Indexed: AND (IX + d); LD (IY + d), N

- Bit: SET 0, B; SET 7, (HL)

https://8bitnotes.com/2017/05/z80-addressing-modes/

- Interrupts

- -NMI

- non-maskable

- Higher priority

- Procedure starts at 0066h

- Accepted always if  $\overline{\text{BUSRQ}}$ =1

- -INT

- Maskable

- Lower priority

- When accepted,  $\overline{IORQ} = \overline{M1} = 0$

- Three different service modes

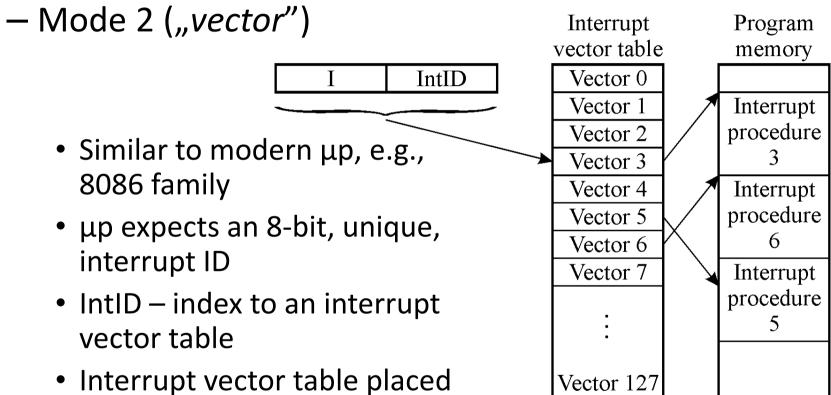

- Maskable interrupt service modes

- Mode 0 ("historical")

- As in 8080

- $\mu p \; expects \; \texttt{RST} \; \; p \; command$

- Procedures start at p

- p=(0..7)×8=0, 8, 16, 24...56

- 8 hardware recognised interrupts

- Mode 1 ("single chip")

- µp expects nothing

- Procedure starts at 0038h

• Maskable interrupt modes

in memory at location pointed by the content of I register

- Z80 IC family

- PIO, CTC, DMA, SIO, DART...

- Z80 clones

- Z80 applications

- Home μc (ZX Spectrum, Amstrad, CP/M-based)

- Embedded systems (e.g., TNC controllers)

- Z80 as a single chip  $\mu c$

- CPU + PIO + CTC + SIO in a single IC

- Add some memory and you get a complete  $\mu c$

- Many original IC disadvantages fixed